Már idén érkezik a PCI Express 4.0

Igyekszik reagálni a kihívásokra a PCI Express szabványt felügyelő iparági szervezet, a PCI-SIG is, a "szokásos" gyorsulás mellett érdekes új fejlesztéseket is kap az adatbusz következő, 4.0-s generációja.

A PC-s környezetben gyakorlatilag egyeduralkodó volt az elmúlt években a PCI Express, az utóbbi időben azonban több oldalról is kihívást kapott az adatbusz-szabvány. Alulról az ARM-ökoszisztéma felől jött kihívás, az alacsony fogyasztásra kihegyezett adatbuszokkal a tabletekben (és telefonokban) a PCI Express nem tudta felvenni a versenyt. De felülről, teljesítményorientált oldalról is érkezett kihívás, például az NVLink formájában, amely a szabványt egy új pont-pont adatbusszal váltaná ki a CPU-GPU kommunikációban (a riválisok pedig egy hasonló szabványt fejlesztenek CCIX néven).

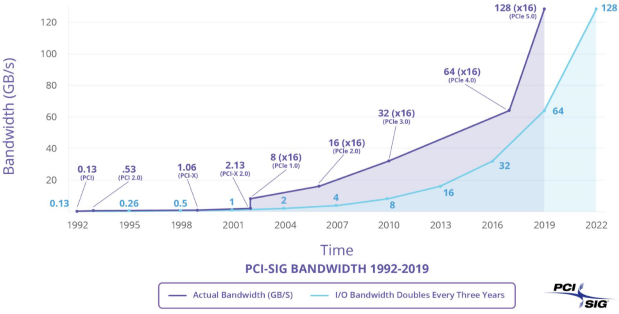

A vonalakat kreatívan húzva úgy tűnhet, hogy gyorsabb a fejlődés, mint a háromévenkénti duplázódás

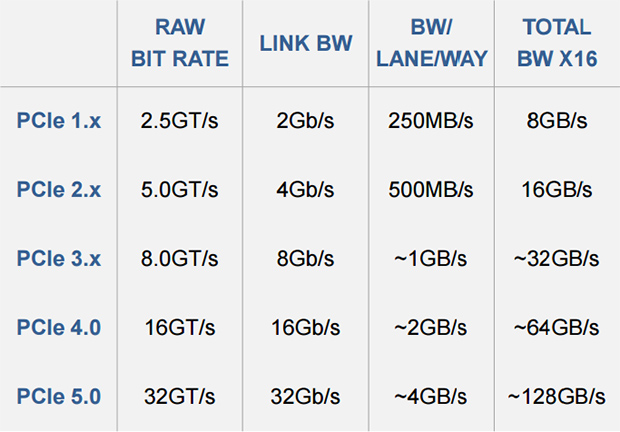

A PCI Express 4.0 mindkét kihívásra igyekszik választ adni - lássuk először a teljesítménybeli újdonságokat. Nyersen fogalmazva a 4.0-s csatoló kereken dupla sávszélességet biztosít a 3.0-s generációhoz képest, a nyers átviteli teljesítmény 16 gigatranszfer másodpercenként és csatornánként - ez a már 3.0-nál is használt 128b/130b kódolás miatt kicsit kisebb a gyakorlatban. Ez a szokásos 16 csatornás illesztőt figyelembe véve irányonként 32 gigabájt/másodperc sebességet jelent, aggregáltan 64 GBps az átvitel. Ez a pont-pont összeköttetést biztostó NVLinkkel már bőven egy kategória, az 8 csatornás kivitelben 50 (25+25) gigabájtot visz át másodpercenként.

A 4.0-s PCI Express azonban nem csak szabványtervezet formájában létezik, az első (igaz, még nem végleges) fizikai implementációk is lassan rajtra készen állnak. A PCI SIG tavalyi fejlesztő eseményén a Cadence, a PLDA és a Synopsys is demózta már saját PCIe 4.0 vezérlőjét, idén pedig már gyakorlatilag piacérett megoldásokkal jöttek a gyártók, a NEC például Ethernet-PCIe bridge chipet fejlesztett, de az ökoszisztéma többi része is készen áll, a tesztberendezések, kontrollerek, switchek is a fejlesztők rendelkezésére állnak.

Várhatóan a legelsőként az IBM fut majd be, az év második felében érkező Power 9-es chipek már Gen 4 támogatással rendelkeznek majd. Ezt az IBM szerverei hálózati vezérlőkhöz és különböző gyorsítókártyákhoz vetik majd be. Brad McCredie, a PCI Express fejlesztéseiért felelős IBM fellow szerint a Gen 4 implementáció nem hordozott meglepetéseket, különösebb probléma nélkül sikerült az (adatközponti színvonalú) validációt megugrani vele.

Az új szabvány azonban nem csak sebességben, hanem kiegészítő funkciókban is sokat hoz. Az egyik ilyen a lane margining, amely a szabvány kötelező eleme, és sokkal kifinomultabb (és olcsóbb/gyorsabb) minőségbiztosítást tesz lehetővé a gyártók számára. De további fejlesztések célozzák a rendszerszintű késleltetés visszaszorítását, a mobil környezetben kritikus alacsony fogyasztású működési módokat és a 16 csatorna fölötti skálázódást is, valamint várhatóan (a tervek szerint legalábbis) a szabványos alaplapi csatlakozóknál is jön meglepetés, a tervek szerint kötelező lesz a 300 wattos felvehető teljesítmény, ezzel eltűnhetnek a GPU-król a kiegészítő tápcsatlakozók.

PCI Express generációk - gyorsabban gyorsul

Jogod van tudni: mankó kirúgáshoz, munkahelyi szkanderezéshez Ezúttal egy mindenki számára kötelező, de laza jogi különkiadással jelentkezünk. Ennyi a minimum, amit munkavállalóként illik tudnod.

Hogy a konzumer szegmensbe mikor érhet el a PCI Express új verziója, erre tippünk sincs. A pletykák szerint az Intel már a Skylake kapcsán tervezte a szabvány támogatását, de erre végül nem került sor. Valószínűleg mind az AMD mind az Intel 2018-ban megjelenő chipjei fogják implementálni a technológiát - az AMD Vega GPU-i azonban várhatóan még idén megugorják a generációváltást.

Halad az 5.0-s generáció fejlesztése

A 4.0-val persze nem áll meg a PCI Express fejlődése, a szabványt felügyelő csoport előtt van már az 5.0-s verzió egyik első vázlata is. A jelenlegi célkitűzés roppant ambiciózus, a PCI-SIG nagyjából 2019-re szeretné befejezni a fejlesztést és a szabvány véglegesítését, amely egyébként újra duplázná a sávszélességet, ezúttal csatornánként 32 gigatranszfer/másodpercre. Ez persze roppant agresszív ütemterv és érdemes is helyén kezelni, a testület ugyanis a 4.0-val kapcsolatban is hasonlóan merészen tervezett, azt eredetileg 2014-2015 magasságában várta a piacra.

A PCI SIG azonban optimista: "A meglévő fizikai interfészekre nagyban tudunk építeni, fel tudjuk használni a más szabványok implementálásánál már elvégzett munkát" - mondta Al Yanes, a PCI SIG elnöke az EE Timesnak. "A Gen 4-gyel elvégzett munka jelentős része újrahasznosítható és könnyebbé teszi a Gen 5 fejlesztését. Az elektronikai implementációval foglalkozó munkacsoport nagyon bízik a számokban és a tervezett dátumokban."

A Gen 5 (vagy PCI Express 5.0) azért még gyerekcipőben van, így egyáltalán nem biztos, hogy a maximális távolságra vagy vagy az elektronikai komponensekkel való tűréshatárok nem szigorodnak a 4.0-hoz képest. Azt azonban egészen bizonyosan állítja a PCI SIG, hogy a szabvány visszafelé kompatibilis marad minden korábbi PCI Express megoldással,