A Fujitsu is saját processzort tervez a gépi tanuláshoz

A japán cég szerint gyorsítója a konkurencia megoldásainál tízszer hatékonyabb lesz.

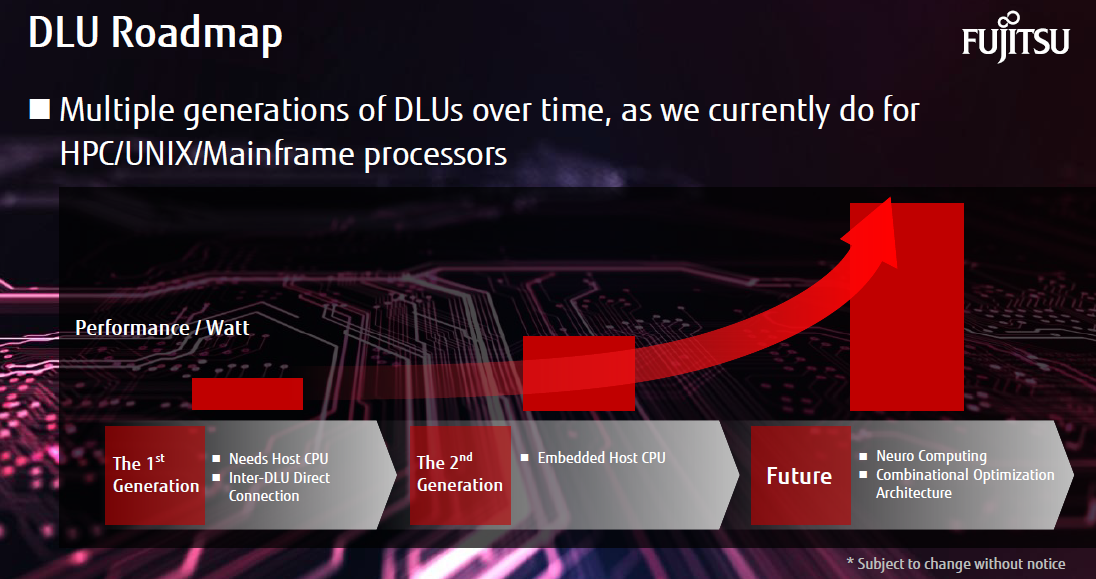

A Fujitsu is ASIC-cal, azaz alkalmazás specifikus áramkörrel képzeli el a gépi tanuláshoz szükséges műveletek gyorsítását. A vállalat ehhez DLU (Deep Learning Unit) néven egy saját dizájnt készít, amellyel igencsak ambiciózus célt tűzött ki, ugyanis az elvárások szerint a chip tízszer hatékonyabb lesz a konkurensek megoldásainál. A skálázható dizájn a tervek szerint már jövőre csatasorba állhat, ezt követően pedig még legalább két generáció érkezik.

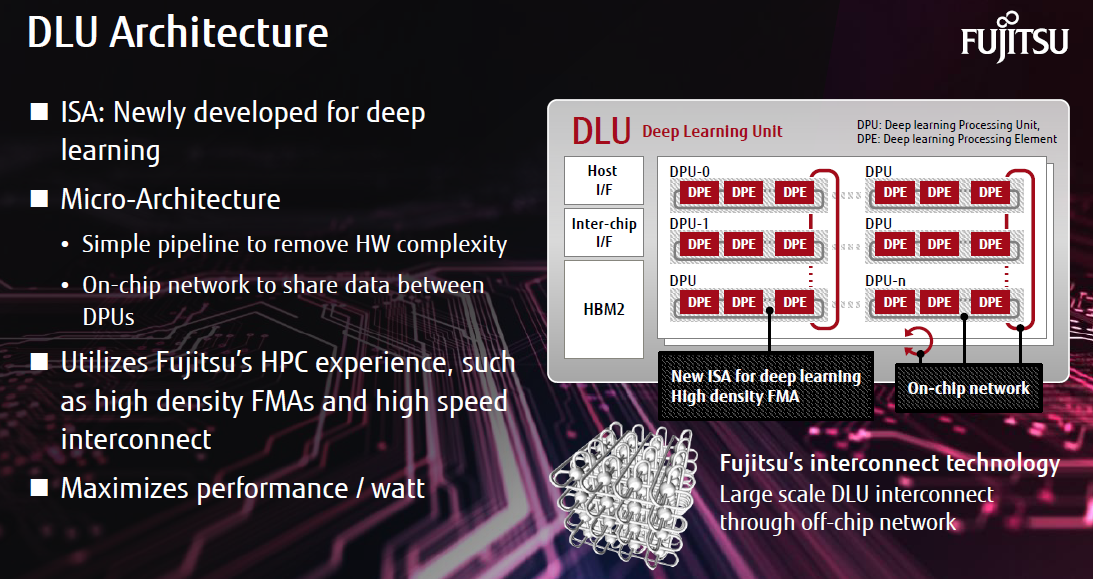

A DLU-t 2015-ben kezdte el tervezni a Fujitsu, amelynek részleteiről a napokban beszélt először a cég. Az információk alapján a dizájn nagy vonalakban hasonlít a modern GPU-khoz, abban ugyanis több, DPU (Deep Learning Processing Units) névre keresztelt mag kapcsolódik, amelyek mindegyike képes FP32, FP16, INT16, és INT8 műveletek végrehajtására. Manapság utóbbi számít igazán népszerűnek, ezt a 8 bites egészszámos végrehajtást támogatja az Nvidia Pascal család néhány tagja is. A szakemberek szerint ezzel meglehetősen nagy tempó érhető el anélkül, hogy komolyabb csorbát szenvedne a pontosság, illetve az problémát okozna a végeredményben. A DPU-t további egységekre bontható, mindegyik elem 16 darab DPE-t (Deep learning Processing Element) tartalmaz. Ez egyenként nyolc SIMD végrehajtót és egy szoftveresen vezérlehető, nagy regiszterfájlt tartalmaz.

A lapkán belül elhelyezkedő egyes DPU-k hálózatba rendeződve működnek, vezérlésükről pedig egy központi mag gondoskodik, beleértve a memóriaműveleteket is, amelyek az Nvidia és az AMD egyes kártyáiról megismert HBM2-es chipekbe futnak ki. Az egyelőre nem lehet tudni, hogy hány chippel számol a Fujitsu, de várhatóan legalább kettő kerül a DLU mellé, amivel legfeljebb 512 GB/s-os sávszélességet és 16 gigabájtos tárkapacitást lehetne elérni.

A memóriavezérlő mellett egy interkonnekt vezérlő is helyet kap a lapkában, ez a Fujitsu által fejlesztett, a SPARC processzoroknál már régebb óta alkalmazott Tofut (Torus fusion) támogatja. Ennek segítségével kommunikálhat a gazdaprocesszorral a gyorsító, illetve ezzel skálázható egészen nagy méretekig és komplexitásig deep learning rendszer. A Fujitsu jelenlegi tervei szerint a második generációs DPU már a processzorral azonos lapkában vagy tokozáson kap helyet, a harmadik verzióra pedig kombinált mikroarchitektúrát célzott meg a cég.

Jogod van tudni: mankó kirúgáshoz, munkahelyi szkanderezéshez Ezúttal egy mindenki számára kötelező, de laza jogi különkiadással jelentkezünk. Ennyi a minimum, amit munkavállalóként illik tudnod.

A Fujitsu számára egyébként nem új keletű a processzortervezés, a japán cég SPARC családja egészen a 90-es évek első feléig vezethető vissza, a legújabb szülött SPARC64 XII pedig mindössze néhány hónapja jelent meg, várhatóan ehhez kapcsolva kínálja majd jövőre érkező DPU-ját a vállalat, amelynek munkálataiban amúgy számos, korábban a SPARC-on dolgozó szakember vesz részt.

A dedikált gyorsítóké a jövő?

Nem a Fujitsu az első, amely dedikált gyorsítót készít gépi tanuláshoz. A Google ehhez már két éve használ saját megoldást, a TensorFlow gépi tanulásos algoritmusok gyorsításához tervezett TPU egy mátrixokkal dolgozó CISC processzor, amely a cég mérései szerint 35-ször gyorsabb az Intel korábbi csúcs Xeonjánál, miközben fogyasztása alacsonyabb, tehát a kritikus fontosságú fogyasztás/teljesítmény mutató is számottevően jobb, mint CPU (vagy akár GPU) esetében. Mindez elsősorban a GPU-kat tervező Nvidia számára lehet rossz hír, amely cég a versenyben maradáshoz idővel kénytelen lesz egy kizárólag a gépi tanulás gyorsításához tervezett terméket kifejleszteni.