Mi lesz veled DRAM?

Elérhető közelségbe kerültek a DRAM korlátjai, a pár év múlva 50. születésnapját ünneplő technológia belátható időn belül limitálhatja a fejlődést, a felmerülő problémákra pedig egyelőre csak átmeneti megoldások vannak.

Rohamléptekben közelít a DRAM pályafutásának vége, a gyártók egyre több, a technológia alapjaiban gyökerező limitációba ütköznek. A (könnyen elérhető) sávszélesség-potenciál mellett a skálázhatóság is egyre problémásabb. A következő évtizedben eljöhet a kritikus pont, mikor a fejlettebb, alacsonyabb csíkszélességű gyártástechnológia bevetése nem csökkenti tovább a gyártási költségeket. Átmeneti megoldások már akadnak, de egybehangzó vélemény egy univerzális trónörökösről egyelőre nincs.

A skálázódás vége

Jogod van tudni: mankó kirúgáshoz, munkahelyi szkanderezéshez Ezúttal egy mindenki számára kötelező, de laza jogi különkiadással jelentkezünk. Ennyi a minimum, amit munkavállalóként illik tudnod.

A DRAM-ok esetében már a kezdetek óta a költséghatékonyság növelésére törekednek a gyártók, mely elengedhetetlen ahhoz, hogy ezen a hullámvasútszerű, volatilis piacon nyereségesek maradhassanak. Ennek legfőbb módja az egyre fejlettebb gyártástechnológiák bevetése, amivel automatikusan nő a szilíciumostyánként kitermelhető DRAM lapkák száma. Ezzel egyetlen lapka előállítására vetített költségek csökkenhetnek, legalábbis egy bizonyos pontig.

Szakértők egybehangzó véleménye szerint még legfeljebb három-négy félvezető-technológiai lépcső állhat a gyártók, azaz a Samsung, az SK Hynix, és a Micron előtt. A trió közül jelenleg a piacvezető Samsung áll a legjobban, a dél-koreai cég már javában dolgozik a 18 nanométer bevezetésén, ami jelen állás szerint valamikor a nyár folyamán megtörténik, ezt követően a dél-koreai cégnek már csak két lépcsője marad, egy 14 és 16, egy másik pedig 14 és 12 nanométer között. Ez alatt előreláthatólag már nem éri majd meg a kutatás és fejlesztés költsége, illetve az egyre komplexebb gyártás futtatása, egységnyi kapacitást drágább lesz előállítani még a kedvezőbb tranzisztorsűrűség ellenére is. Hogy ennek pontosan milyen következményei lehetnek majd, arról egyelőre csak találgatni lehet, de az árak stagnálása mellett egy esetleges áremelkedés is benne van a pakliban.

Lesz-e DDR5?

De nem csak az alap építőelem, a DRAM jelent problémát. A DDR memóriák elmúlt nagyjából másfél évtizedes fejlődése viszonylag sima volt, a fejlesztések relatíve egyszerűek és kiszámíthatóak voltak. A cél a sávszélesség folyamatos, de lassú növelése, miközben a fogyasztást a gyártók próbáltál lejjebb szorítani, vagy legalább a korábbi szabvány szintjén tartani. A konzervatív megközelítés egyik oka a költségek kordában tartására vezethető vissza, a forradalmi újítások rendszerint komolyabb befektetéseket igényelnek, a fejlesztési és gyártási kiadások mellett pedig az implementáció is drágább.

Ugyanakkor a rohamléptekben növekvő igények tükrében kétséges, hogy ez az irány tartható-e. Jelenleg közel sem biztos, hogy az evolúció folytatódik, és az aktuális DDR4 szabványt a DDR5 személyében egy újabb állomás követi. Egyelőre utóbbi mellett szól, hogy a szerverek kapacitásigénye folyamatosan növekszik, a tendenciának pedig egyelőre nem látni pontosan a végét. Itt továbbra is jó szolgálatot tesz a DDR(4), mely szabványra épülő modulokkal költséghatékonyan, illetve viszonylag egyszerűen bővíthető az operatív tár mérete, ennél olcsóbb megoldás jelenleg nincs a piacon.

Eltérő igények

Az elmúlt bő egy évtizedben eltérő igények rajzolódtak ki a különféle rendszerekhez szükséges memóriák palettáján. Az asztali PC-k sávszélesség, illetve kapacitásigénye csupán kisebb mértékben nőtt, míg a kiszolgálók esetében ennek épp a fordítottja figyelhető meg. Emellett megjelent az ultramobil szegmens, ahova nagy sávszélességű, alacsony fogyasztású, minimális helyigényű, mindeközben pedig olcsó megoldásra vágynak leginkább a gyártók, miközben a hálózati eszközökben az alacsony késleltetés a legfontosabb szempont.

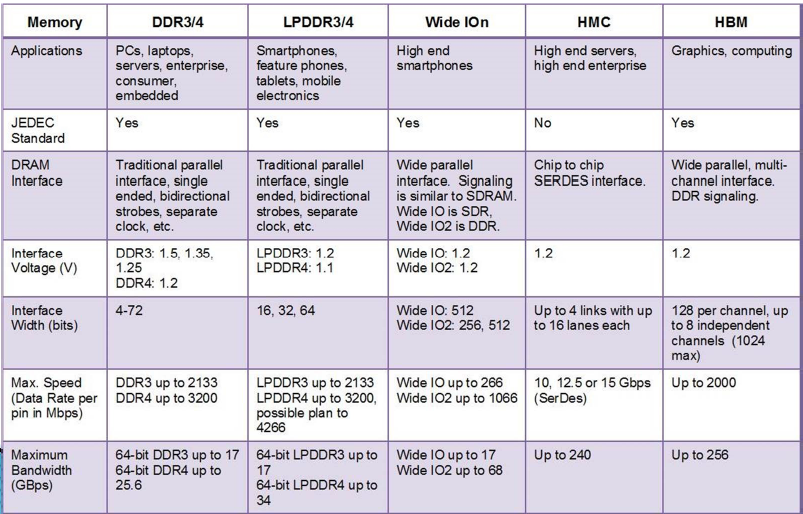

Egyetlen memóriaszabvánnyal ezen igényeket jelenleg nem lehet megfelelően kielégíteni, így az elmúlt pár évben napvilágot látott néhány kompromisszumos megoldás, melyek ugyanakkor továbbra is DRAM alapokra építkeznek, tehát a cellákat egy tranzisztor és egy kondenzátor párosa alkotja, utóbbit pedig 64 ezredmásodpercenként frissíteni (azaz olvasni és felülírni) kell, különben elveszíti a töltését, az adott bit pedig korrupttá válik.

Alternatívák kellenek

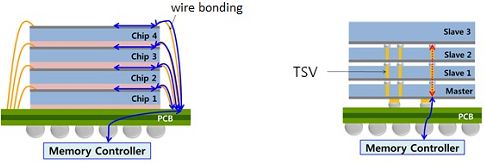

A különféle problémákkal a gyártók is tökéletesen tisztában vannak, évek óta folynak a fejlesztések, amelyekkel meg lehet hosszabbítani az egyre korosodó DRAM életútját. A különféle rétegzett megoldások épp ezt a célt szolgálják, melyek egyik, egyszerűbb variánsa a TSV (through-silicon via). Ennél az egyes memóriachipek egyetlen tokozáson belül több szilíciumlapkát is tartalmazhatnak kapacitásuk növelése érdekében.

A tradicionális, egyrétegű eljárással szemben a TSV-nél az egymásra rétegezett szilíciumlapkákon belül kialakított több száz járaton keresztül futnak végig a vezetékek. Ezzel elhagyható a relatíve vastag elválasztóréteg, illetve a huzalok hossza is jelentősen redukálható, így a korábbi megoldáshoz viszonyítva több lapka helyezhető egymásra, miközben a fogyasztás is csökken. A technológiával jelentősen növelhető egyetlen chip kapacitása, ez viszont csak egyetlen problémát hidal át, azt is csak részben.

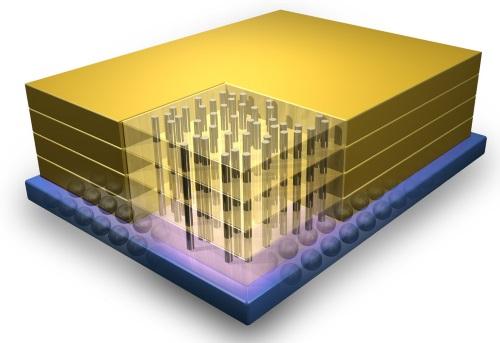

Szintén rétegezett memória a HMC (Hybrid Memory Cube) és a HBM (High Bandwidth Memory), ugyanakkor ezek a TSV-nél már komplexebb megoldások, ezeknél a kapacitás mellett a sávszélesség is nő, miközben az alacsonyabb órajel miatt a fogyasztás csökken. A HMC a Micron, a HBM-et pedig az SK Hynix fejleszti, a két megoldás hasonló elven alapszik, ugyanakkor vannak alapvető eltérések, az egyik fontos, hogy utóbbi már szabványos, a JEDEC szerint is elfogadott, míg az utóbbi egyelőre csak a Micron háziszabványa. A HBM egy a DDR-éhez hasonló interfészt lényegesen szélesebb busszal használ, a HMC pedig ezzel szemben egy merőben más, pont-pont SerDes buszt alkalmaz, ami a processzor memóriavezérlőjének oldaláról komolyabb módosításokat igényel, ezen a ponton az implementáció valamelyest bonyolultabb, költségesebb.

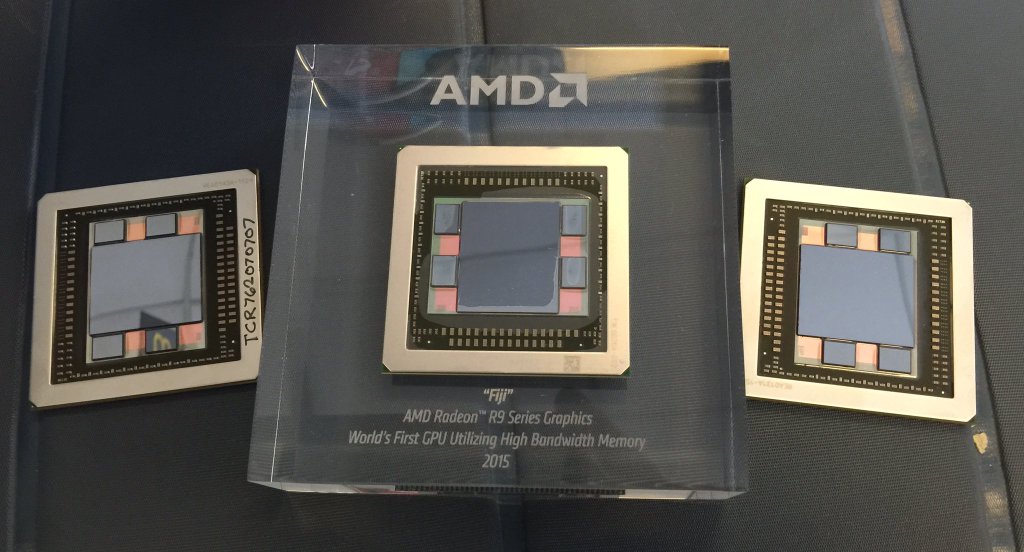

A speciális busznak köszönhetően ugyanakkor a lapkák relatíve kevés érintkezővel rendelkeznek, a BGA tokozású verziók 896, az FBGA-s variánsok pedig 666 érintkezőt vonultatnak fel, így azok közvetlenül a NYÁK-ra helyezhetőek. A HBM implementációja ebből az aspektusból komplikáltabb, egyetlen lapka 3-4000 érintkezőjéhez már interpózer szükséges, ekkora számú összeköttetést nyomtatott áramkörben viszonylag kis területen nem lehet megvalósítani. Mindez komplex és költséges gyártáshoz vezet, az eddigi egyetlen, HBM memóriát alkalmazó AMD Fiji grafikus chip összeállításához a GPU lapkáját gyártó TSMC mellett az interpózert készítő UMC, illetve a HBM chipeket szállító SK Hynix közreműködése is kellett, a gyártás végső fázisát pedig egy negyedik cég, az ASE végezte.

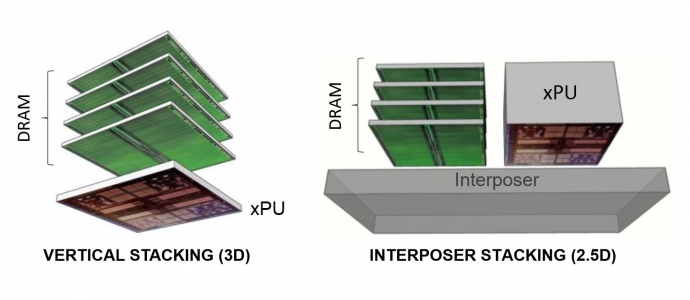

Míg a HMC elsősorban nagy teljesítményű szerverek, szuperszámítógépek gyorsítóin kaphat helyet, addig a HBM leggyakoribb előfordulási helye a grafikus kártya, amivel kimarad egy egyre fontosabb szegmens, a telefonos-tabletes piac. A speciálisan ezt a területet megcélzó Wide IO a HBM-hez hasonlóan a DDR interfészre építkezik, de egy annál jóval szélesebb buszt alkalmazva. A HBM-mel ellentétben a Wide IO memória közvetlenül a processzor lapkájára kerül (3D stacking), az összeköttetést pedig a feljebb ecsetelt TSV technológia biztosítja.

Így bár interpózerre nincs szükség, az összeállítás és a megfelelő hőelvezetés kidolgozása növeli a komplexitást, ezzel párhuzamosan pedig a költségeket is. Ennek ellenére már elérhető távolságban van a Wide IO, hisz az ARM kimutatása szerint 2009 és 2014 között tizenhatszorosára nőtt az ultramobil alkalmazásprocesszorok sávszélesség igénye, mely tendencia bár lassul, de a DDR4 még így sem lesz képes kiszolgálni a csúcskészülékek szükségleteit.

Lesz-e univerzális megoldás, és mikor?

A memóriagyártóknak - és velük együtt a teljes iparnak - egyre komolyabb kihívásokkal kell szembenézniük, az elmúlt pár év során jelentősen megváltozó igényeknek köszönhetően pontosan három taggal nőtt a memóriaszabványok palettája. Mindez növeli a költségeket, hisz egy bizonyos szabvány csak egyetlen területre ideális, ami a méretgazdaságosságra hat negatívan. Emellett már látótávolságon belül a skálázódás vége, a DRAM, mint a jelenlegi összes memória alapja a következő évtizedben még komolyabb gátat szabhat a fejlődésnek. A vállalatok évtizedek óta kutatják az utódot, de a DRAM gazdaságosságát még hosszú ideig nehéz lesz megközelíteni.

Az egyik, sokak által az első helyre rangsorolt alternatíva az MRAM lehet. A magnetorezisztív RAM a rég elfeledett ferromágneses memóriához hasonlóan elektromos töltések helyett mágneses mezőt használ az adatbitek tárolására. Az MRAM "nem felejt", azaz kikapcsolás után is megőrzi a tartalmát, miközben írási és olvasási sebessége a cache memóriaként is használt villámgyors SRAM-okéval vetekszik, lényegesen felülmúlva mind a flash, mind a DRAM chipekét. Az MRAM-nak további előnye, hogy élettartama gyakorlatilag végtelen hosszú, ellentétben például a flash chipekével (vagy az Intel-Micron 3D XPointtal), melyek csak korlátozott számú írás-olvasási ciklust bírnak ki. Összességében az MRAM jellemzői lehetővé teszik, hogy hosszú távon méltó utódja legyen a DRAM-nak (vagy akár flash memóriának), de mint oly sok technológia esetében, a magas költségek egyelőre akadályt jelentenek a magnetorezisztív RAM-nak, a komoly buktató leküzdéséhez pedig könnyen lehet, hogy még évtizedekre lesz szükség.