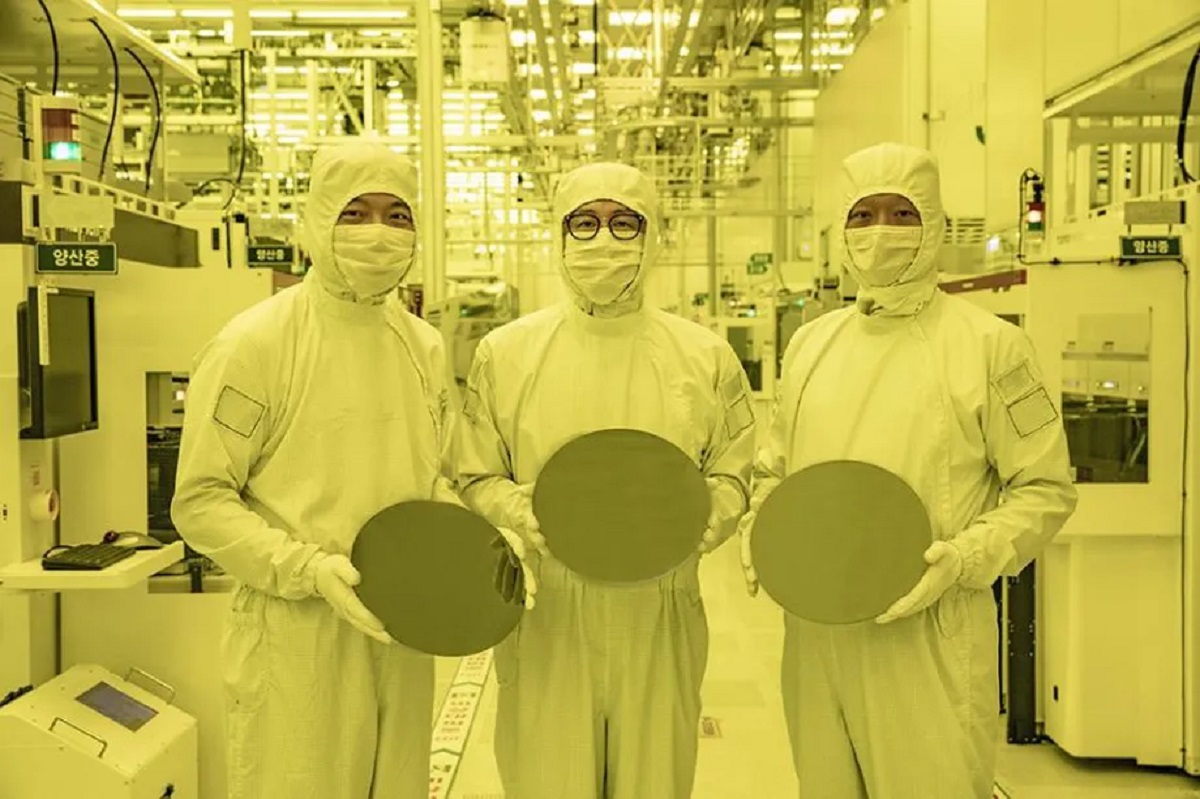

Elrajtolt a Samsung 3 nanométeres chipgyártása

A dél-koreaiak megelőzték a tajvani TSMC-t 3 nanométeren, a Gate-All-Around (GAA) tranzisztor-architektúrának köszönhetően az új gyártási eljárás 45 százalékkal energiahatékonyabb, mint a korábbi 5 nm-es eljárás, és 23 százalékkal jobb teljesítményt biztosít.

A Samsung megkezdte a 3 nanométeres chipek gyártását, ezzel megelőzve a világ legnagyobb szerződéses félvezetőgyártójának számító rivális TSMC-t, ami csak az év második felében vezeti be új node-ját. A dél-koreai bérgyártó még 2018-ban jelentette be, hogy 3 nanométeren beveti a nanohuzal-tranzisztorokat. Ez a már ismert koreográfiának megfelelőn két variánst jelent, a 3GAAE (Gate-All-Around Early), illetve 3GAAP (Gate-All-Around Plus) formájában. A GAA-ra, vagyis a nanohuzal tranzisztorra épülő saját implementációját MBCFET-nek (multi-bridge-channel FET) hívja a Samsung, amelynek fejlesztése egészen 2002-ig nyúlik vissza, így alaphangon egy 20 éves kutatói és fejlesztői munka érik be a 3 nanométer piacra kerülésével.

A dél-koreai óriás bejelentése szerint az új gyártási eljárás 45 százalékkal energiahatékonyabb, mint a korábbi 5 nm-es eljárás, 23 százalékkal jobb teljesítményt biztosít, miközben 16 százalékkal csökken az egységnyi felület. A cég már fejleszti a második generációs 3 nm-es node-ot is, ami a fogyasztási előnyt 50%-ra, a teljesítményt pedig 30%-ra növelheti. Hogy milyen lapkák készülnek először az elsőgenerációs GAA megoldáson, még nem közölte a Samsung, de jó eséllyel nem mobilchipek. A chipeket egyelőre Dél-Koreában gyártják. A cég soron következő texasi chipgyára, amely a korai jelentések szerint végül képes lesz 3 nm-es chipek gyártására, a tervek szerint csak 2024-ben kezdi meg a tömeggyártást.

USA Tech Hub: ahonnan a passzátszél fúj Minden, ami a technológiai szektorban történik, jellemzően az USA-ból indul.

Az elmúlt pár évben egyre többet emlegetett GAA a lehetséges tranzisztorfejlesztési irányokból a legígéretesebbnek tűnt. A fejlesztés ugyanis a FinFET-nél valamelyest kedvezőbb elektromos tulajdonságokkal rendelkezik, miközben a skálázhatóságot számottevően kitolja. Utóbbinak hála tovább csökkenthető a csíkszélesség, nanohuzal tranzisztorokkal 5 nanométer alá is be lehet menni, ezzel egységnyi területre még több tranzisztort besűrítve. A GAA esetében a forrás (source) és a nyelő (drain) között fektetett nanohuzalok vannak, amelyeket mint egy szigetelt elektromos vezetéket, teljesen körülölel a HKMG (magas k-együtthatójú dielektrikum és fém kapuoxid) elektróda, innen a Gate-All-Around elnevezés - szemben a FinFET három oldali ölelésével.

A bejelentés kulcsfontosságú mérföldkő a Samsung és a TSMC közti versengésben. A többek közt Apple chipeket gyártó TSMC áprilisban erősítette meg egy befektetőknek tartott gyűlésen, hogy remekül halad a 2 nanométeres csíkszélességének (N2) fejlesztése is, melynek érkezéséről még 2020-ban beszélt először a vállalat. A jelenlegi tervek szerint a 2 nanométeres architektúrán alapuló lapkák tömeggyártása 2025-ben kezdődik meg. A tajvani bérgyártó az év második felében kezdi meg a 3nm-es lapkák bevezetését, de ezzel még nem vezeti be GAAFET tranzisztorstruktúrát, hanem marad a FinFET-nél, a gyártósorok pedig továbbra is extrém ultraibolya (EUV) litográfiai eljárást alkalmaznak majd.