AMD: az egyre kisebb részegységeké a jövő

A tokokozásos és chipletes fejlesztési irányait boncolgatta az idei Hot Chips konferencia alkalmából az AMD. A releváns és piacképes fejlesztések szempontjából az Intel előtt járó tervezőcég a következő években egyre több szilíciumlapkára bontaná a különféle processzorokat.

Jogod van tudni: mankó kirúgáshoz, munkahelyi szkanderezéshez Ezúttal egy mindenki számára kötelező, de laza jogi különkiadással jelentkezünk. Ennyi a minimum, amit munkavállalóként illik tudnod.

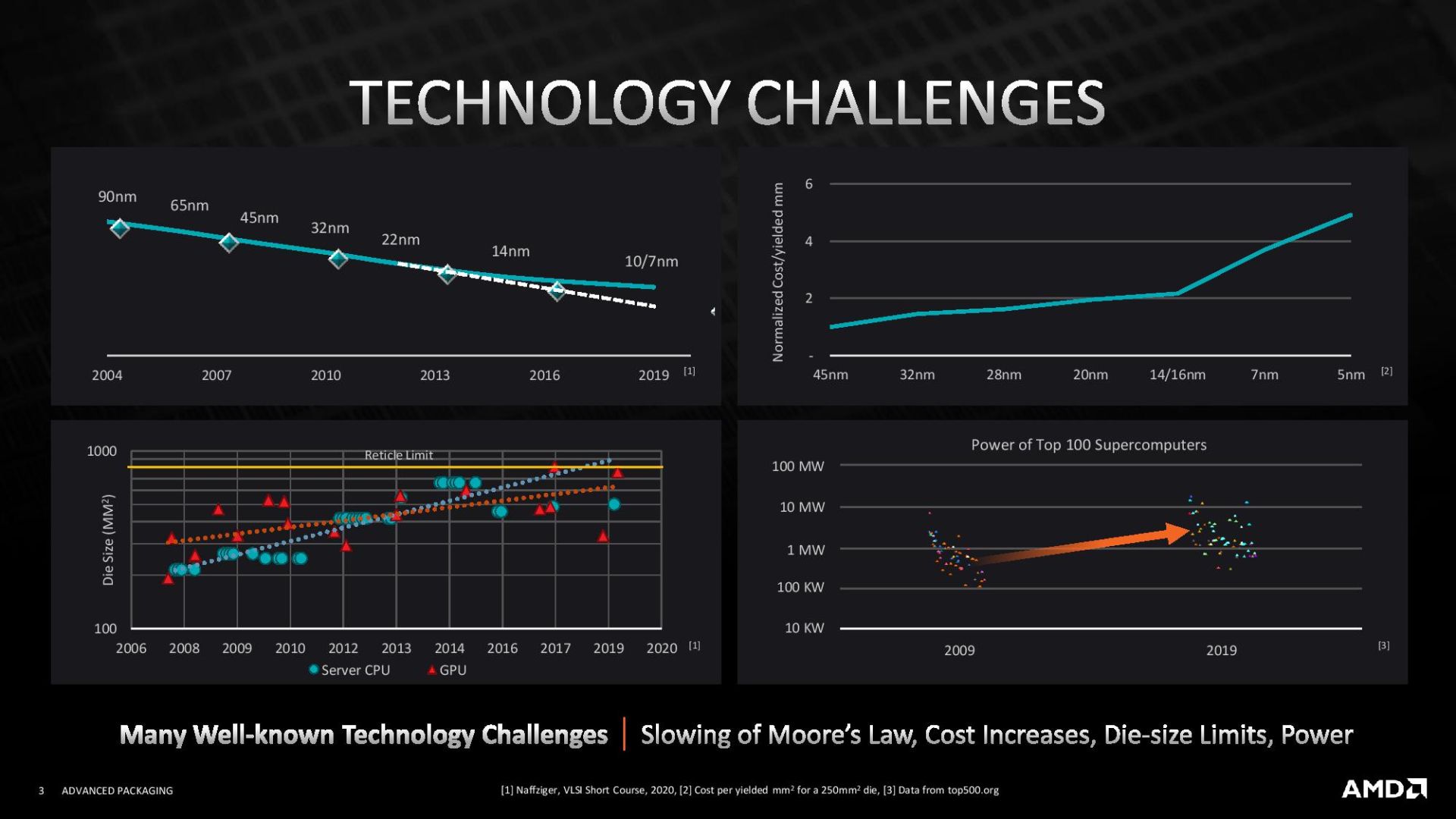

Az AMD a Zen első iterációjával vezette be az úgynevezett chipletes, vagyis több, különálló lapkából álló processzorokat. Az első generációs Epyc (és Threadripper) összesen négy darab nyolcmagos egységet tokozott egybe a komplett CPU-hoz. Az AMD multi-chip (vagy multi-die) megoldását elsősorban a termelés gazdaságossági szempontjai mozgatták, másodlagosan pedig a felépítés biztosította rugalmasság és a tervezési ciklus alacsonyabb kockázata.

A stratégia vitathatatlan előnye, hogy mindössze egyetlen lapkadizájnt kellett kidolgozni, ami a tervezési költségek mellett a gyártási kiadásokat is számottevően csökkentette. A lapkadizájn levilágításhoz (gyártásához) ugyanis egyedi maszkok szükségesek, amelyek elkészítése rendkívül költséges feladat. Ezek darabja már akár az 1 millió dollárt is bőven meghaladhatja, a komponensekből pedig egy modernebb gyártástechnológiához 60-80+ darab is kellhet egyetlen lapkadizájnnál.

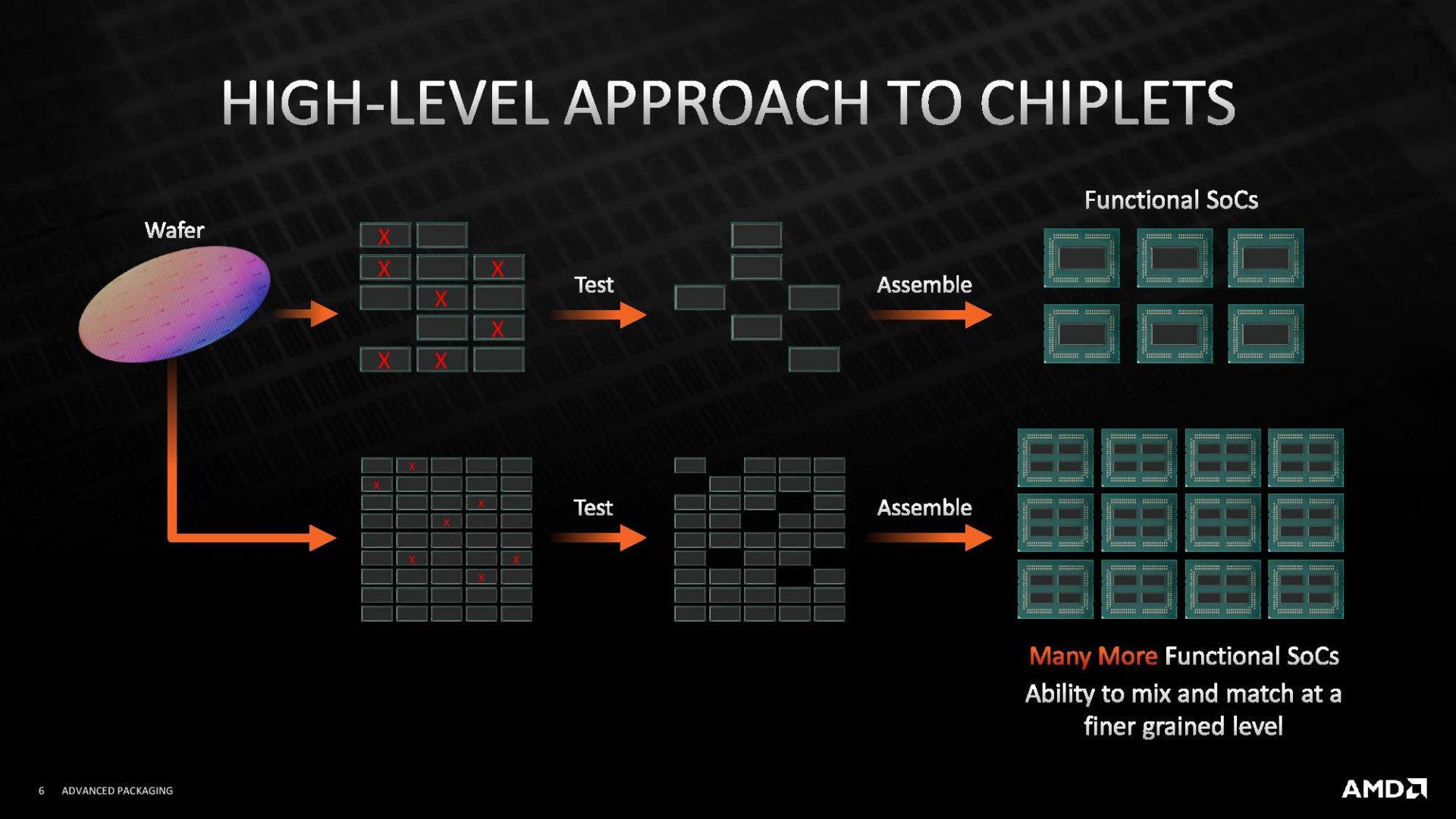

A megközelítésnek van egy másik nagy előnye: Kisebb lapkák esetében a gyártás során egyetlen szilíciumostya megmunkálásánál jelentkező különféle hibák kevésbé befolyásolják az abból kinyerhető komplett lapkák felhasználhatóságát, vagyis kedvezőbb a selejtarány. Ez a bérgyártásban jellemzően ostyánkénti árazásnál alacsonyabb lapkánkénti összeget eredményez, amivel végül a rugalmasabb és gazdaságosabb termelés felülírja a teljesítményben kötött kompromisszumot.

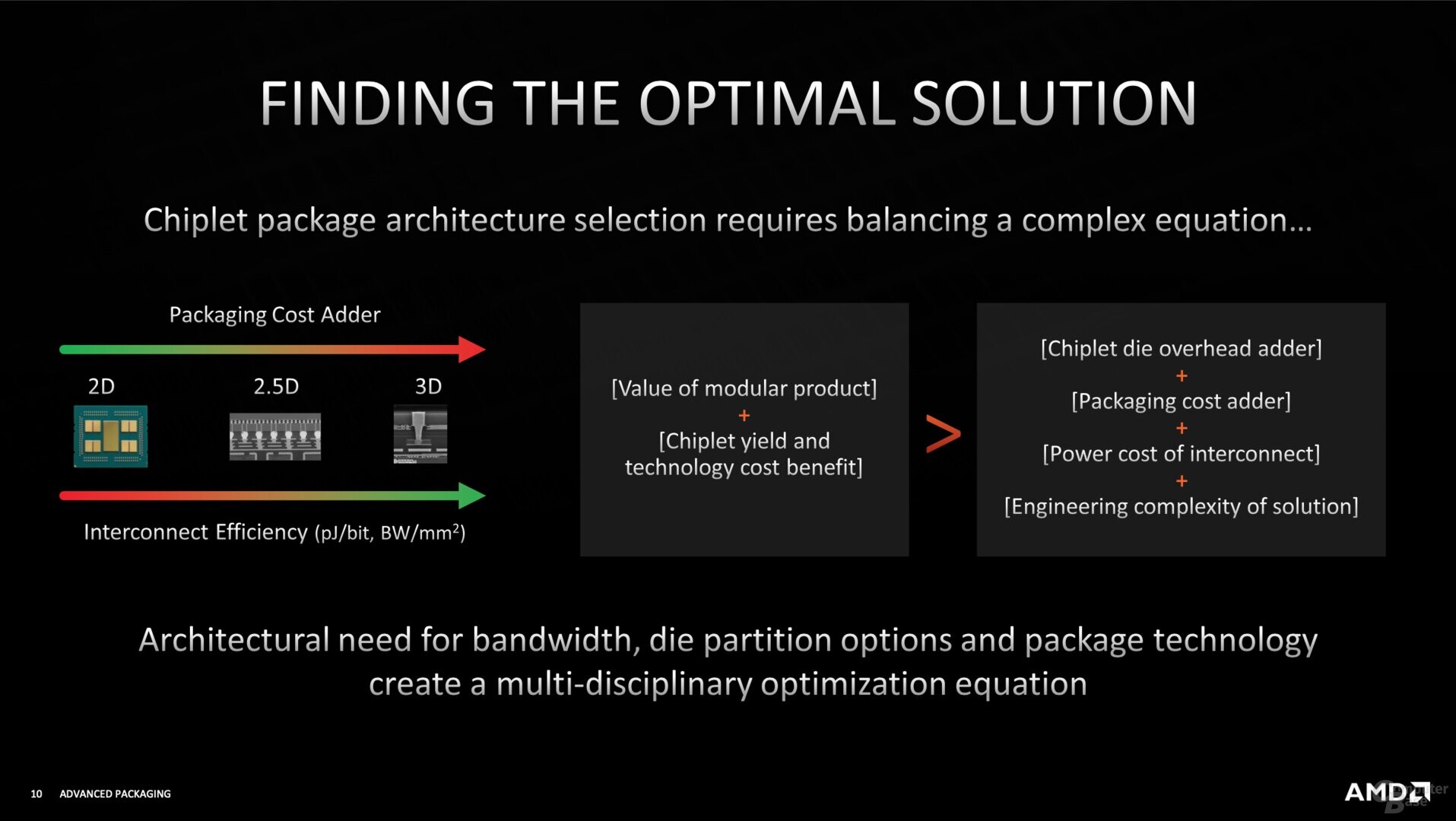

Az egyes lapkákat azonban a processzor tokozásán (nyomtatott áramkörén) kell "összedrótozni". Ez hosszabb, speciális huzalozást jelenthet (interconnect), amely a disszipáción túl a késleltetésre is kedvezőtlen hatással lehet, vagyis két (vagy több) lapka között lassabb lehet az adatcserere. A másik hátrány is ebből ered, az összekötések ugyanis komplex(ebb) tokozást igényelnek, amely bonyolultabb összeállításhoz, így pedig magasabb költségekhez vezet. Az AMD szerint ezért nagyon alapos tervezést és kalkulációt igényelnek a többlapkás termékek, szélsőséges esetben ugyanis a drágább tokozásból adódó komplexitás felemésztheti a kisebb lapkákból eredő gazdasági előnyt.

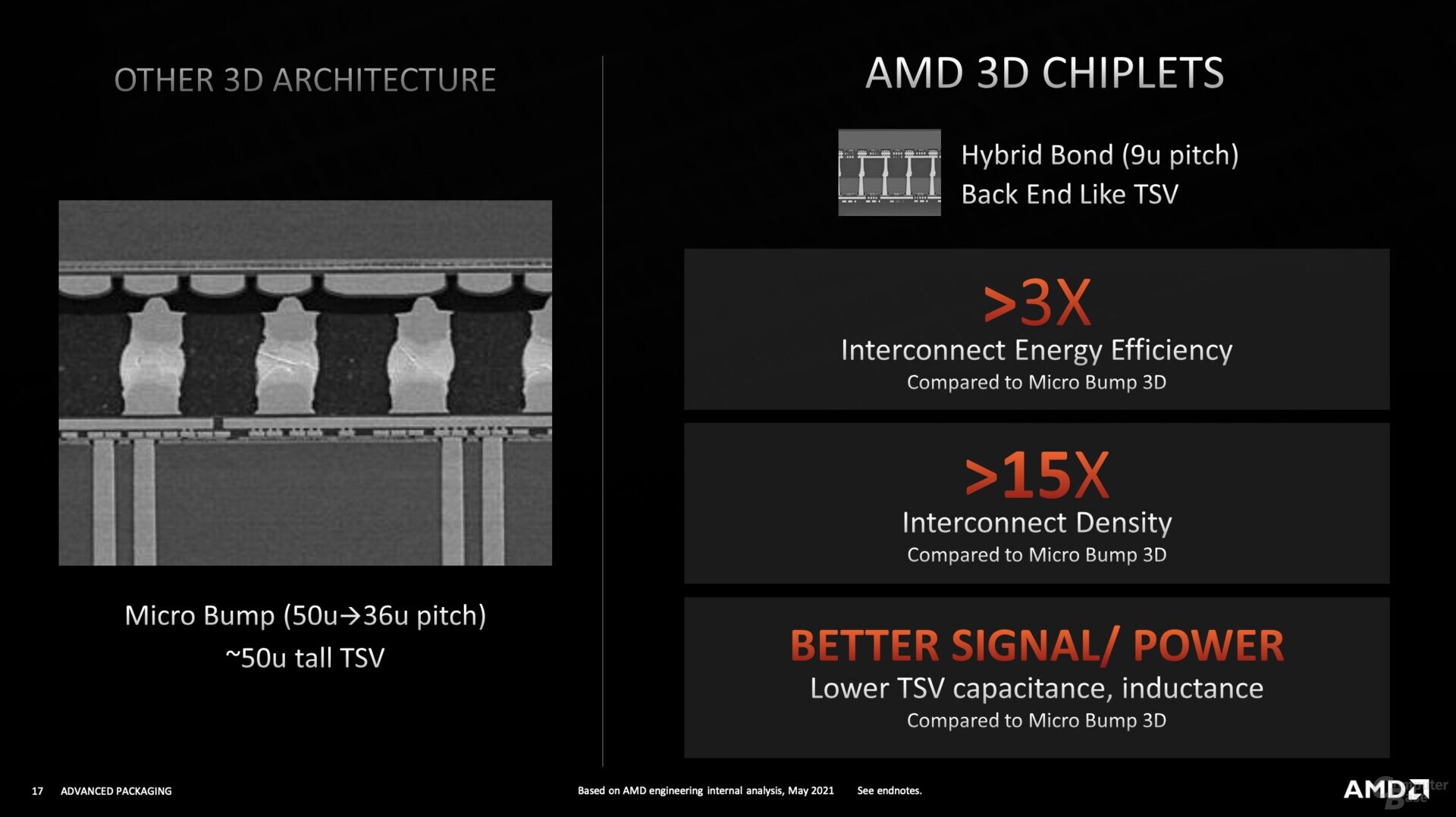

A tervezőcég mindezek tudatában folytatja kutatásait és fejlesztéseit. A következő piacra kerülő megoldásával egy nagyobb kapacitású SRAM lapkát helyezett a Zen 3-as magokat tartalmazó CCD lapkára a cég, 3D tokozási eljárással. Az iparági körökben jól ismert 3D tokozási eljárások lényege, hogy a fix interpózert (átvezető lapkát) alkalmazó, úgynevezett 2.5D-s megoldásokkal ellentétben egymásra építik a lapkákat, hasonlóan mint a rétegzett, HBM memóriáknál. Ennek előnye, hogy ily módon kisebb lehet a komplett processzor területe (és tokozása), illetve optimális esetben azok gyártási költsége. A 3D tokozásnak hála a funkcionalitás alapján külön lapkákra felosztott, heterogén koncepció előnyéről sem kell lemondani.

Az eljárásnak hála komponensektől függően akár más-más gyártástechnológiával is készülhetnek a lapkák, az egyes különálló chipeket pedig a processzor tokozásán belül "drótozzák" össze. A megközelítéssel végeredményben csökkenthetőek a költségek, nem utolsó sorban pedig felgyorsítható az egyes újabb gyártástechnológiák bevetése, nem kell megvárni, hogy a kihozatal elérje a nagyobb lapkák gazdaságos előállításához szükséges szintet.

Az AMD-féle 3D V-Cache esetében az AMD egy 64 megabájtos SRAM lapkát helyez a Zen 3-as CCD lapkára, a két egységet pedig négyzetmilliméterenként több száz rézvezetékkel kapcsolja össze TSV eljárással. Utóbbival az egymásra helyezett szilíciumlapkákon belül kialakított, jelen esetben mintegy 23 000(!) darab járaton keresztül futnak végig az összeköttetést biztosító vezetékek, amelyek között csupán 9 mikrométeres távolság van. Ezzel az apró, mindössze 36 mm2 területű SRAM lapka kapacitása kvázi összeforr a processzormagok melletti harmadszintű gyorsítótáréval, 32 helyett 96 megabájtra emelve a cache méretét. Az AMD szerint az eljárással 2 TB/s-os sávszélesség érhető el viszonylag alacsony késleltetés, illetve disszipáció mellett.

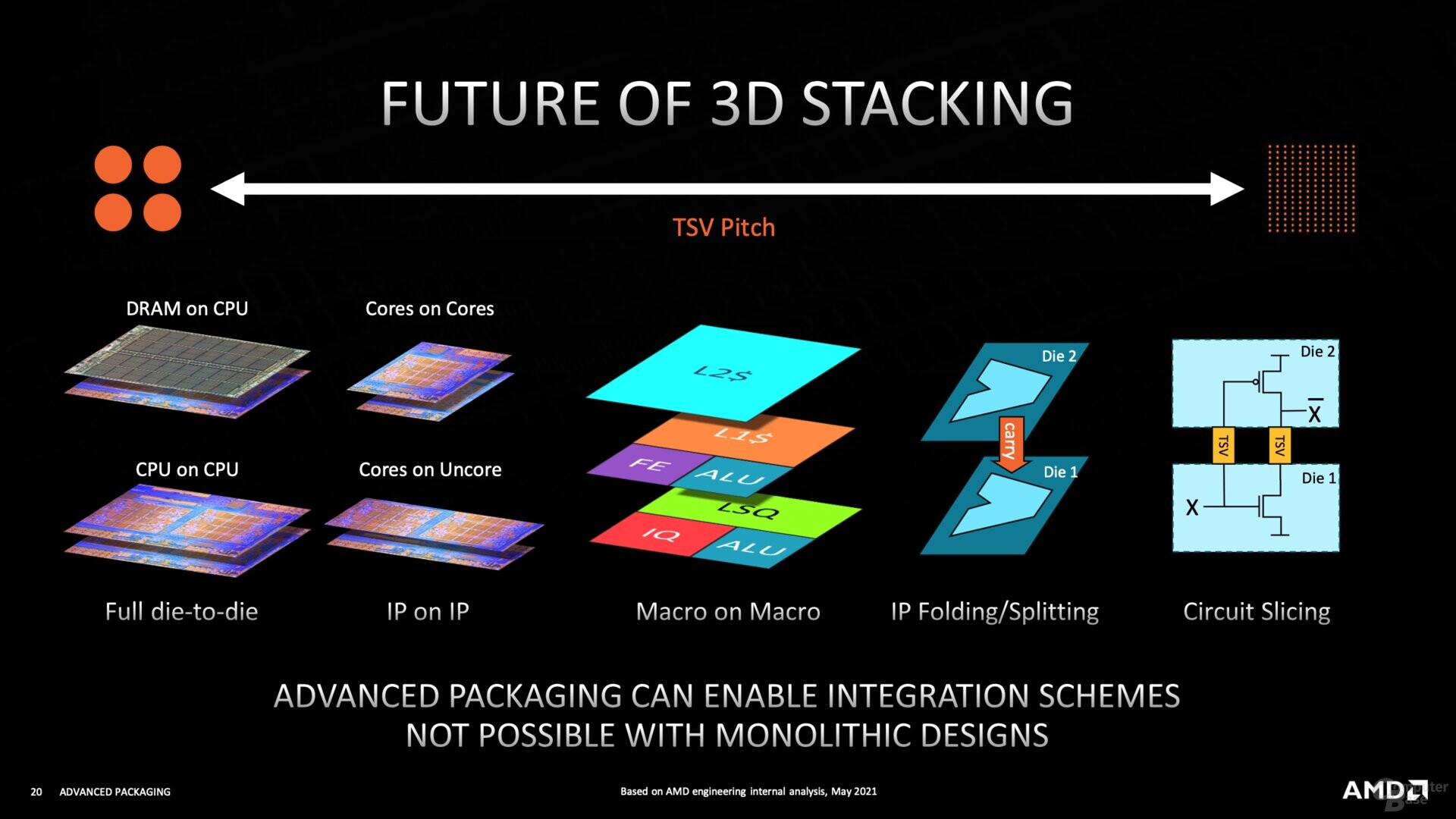

A tervezőcég elárulta, hogy hosszú évek óta dolgozik a fenti fejlesztésen, amely várhatóan valamikor a következő években kerülhet piacra. Mindezek fényében nem meglepő, hogy a tervezőcégnek már a következő lépcsők körül forognak a gondolatai. A TSV-s eljárással ugyanis akár a magokat, illetve az azok működtetéséhez szükséges úgynevezett uncore részt is egymásra lehet helyezni. Eggyel tovább lépve a nyolcmagos lapkát akár nyolc darab különálló magként is le lehet gyártani, majd végül azokat egybetokozni, amennyiben így a gazdaságosabb. Hosszabb távon pedig akár egyetlen magot is szét lehet bontani feldolgozókra és gyorsítótárakra és azokból összeállítani a komplett, működő egységet.

Azt, hogy az AMD pár éve jó irányt választott, mi sem bizonyítja jobban, hogy a közvetlen konkurensek is a többlapkás megoldásokban látja a jövőt. Az Intel néhány éve még jóformán egy összeeszkábált tákolmánynak nevezte az AMD négylapkás Epyc processzorát, a "Sapphire Rapids" Xeonok azonban már egy nagyon hasonló négylapkás felépítéssel érkeznek, valamikor 2022-ben.