Hamarosan elkészül a PCI Express 6.0

A terveknek megfelelően halad a PCI Express 6.0 specifikálása - közölte a PCI-SIG. A szabvány még az idei évben elérheti a végleges verzióját, amit követően a gyártók

megkezdhetik az adaptációt.

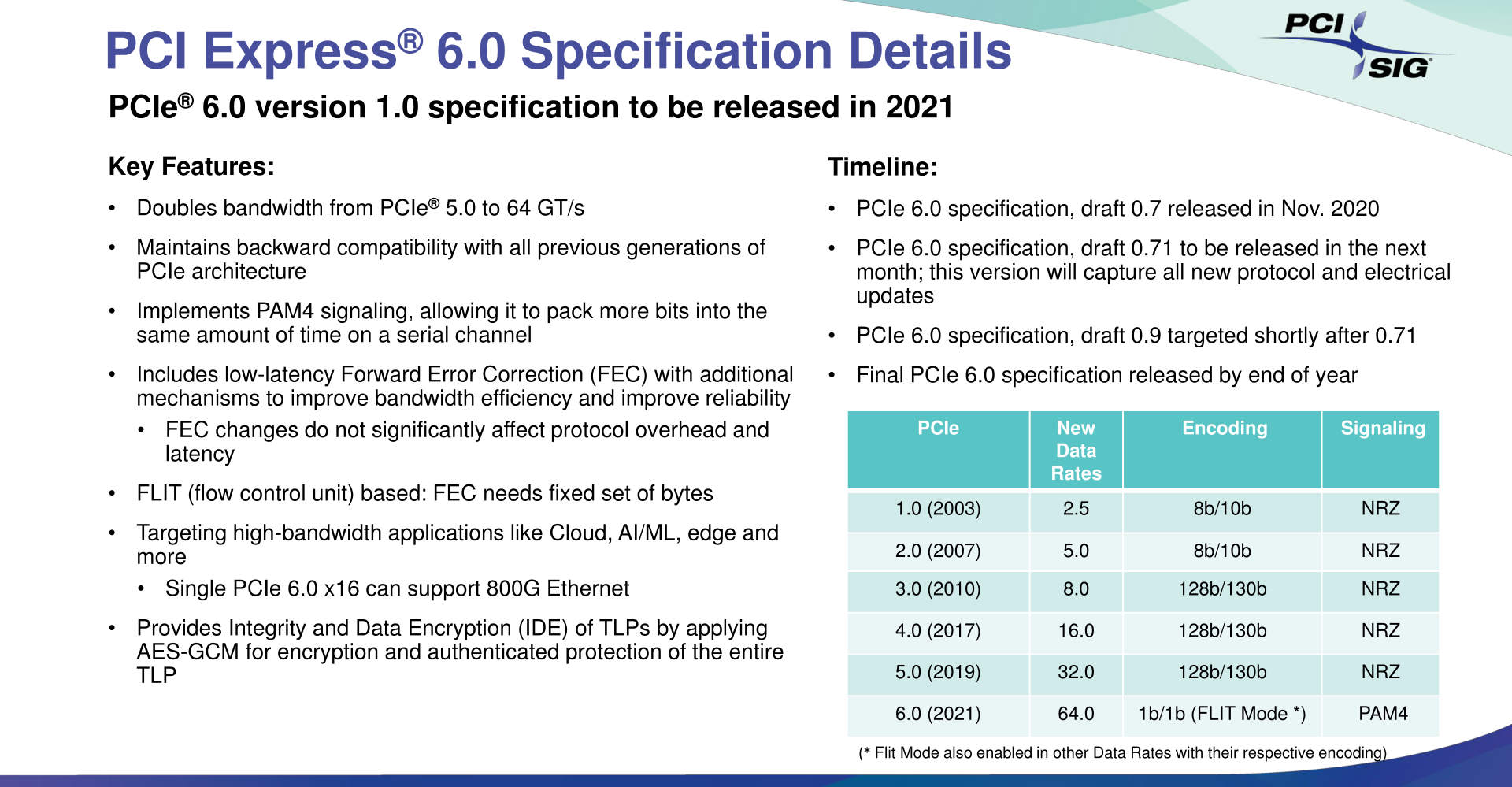

A leírást végző PCI-SIG rövid közleménye szerint a szabvány jelenleg a 0.71-es verziójánál jár, amit az előző héten meg is kaptak a fejlesztésben résztvevő cégek. Amennyiben nem érkezik nagyobb súlyú javaslat vagy észrevétel, a szabványt felügyelő iparági szervezet pár héten belül a 0.9-es verzióval is előáll, amely már a közel végleges kiadás lesz. Ezt követi az 1.0-s kiadás, amit követően a gyártók elkezdhetnek dolgozni a PCI Express 6.0-t támogató termékek véglegesítésén.

Jogod van tudni: mankó kirúgáshoz, munkahelyi szkanderezéshez Ezúttal egy mindenki számára kötelező, de laza jogi különkiadással jelentkezünk. Ennyi a minimum, amit munkavállalóként illik tudnod.

A jól bejáratott koreográfia szerint a Gen6 is rádupláz az előd sávszélességére, melynek hála egy sztenderd 16 sávos csatoló estében a csúcsérték elérheti a másodpercenkénti (közel) 128 gigabájtot. Bár a további növekedésnek elsősorban most is nagyvállalati környezetben lehet igazán létjogosultsága, a duplázásnak hála bizonyos eszközöket a jelenleginél kevesebb sávval is ki lehet majd hajtani, amely egyszerűbb áramköröket eredményezhet. Mindez optimális esetben az árakra is kedvező hatással lehet, habár a 6.0 szabvány fizikai implementációja valamelyest növelheti a költségeket.

A 6.0-s verzió kétségkívül legnagyobb fejlesztését a PAM4, magyarul a négyszintű impulzusamplitúdó-moduláció jelenti. Az 5.0-s verzióig bezárólag a PCI Express NRZ-t, vagyis nullára vissza nem térő kódolást alkalmaz. Az NRZ esetében a bináris információt egyenáramú, szabályos impulzusok hordozzák, amelyekkel 1 bitet lehet továbbítani. A PAM4 is egy impulzus sorozatot használ vivőhullámnak, mellyel azonban egy ciklus alatt több, összesen 2 adatbit továbbítható, így változatlan frekvencia mellett duplázható a sávszélesség.

A PAM4 bevezetése azért szükséges, mert már a PCIe 5.0 is a rendkívül magas, 30 GHz-es frekvenciatartományban üzemel. A jelenleg alkalmazott NRZ-vel még feljebb kellene tornászni a már amúgy is magas frekvenciát, amely a tervezőket és a gyártókat egyaránt komoly kihívások elég állítaná. Bár a PAM4 erre megoldást kínál, a több jelszint (ahogy a NAND-oknál is) újabb problémákat vet fel. Az egyik ilyen a fejlettebb hibajavítás, amit a PCI-SIG az FEC-vel (Forward Error Correction) oldana meg. Az FEC az adat mellé elhelyezett redundanciából (többletadat) lehet képes visszaállítani az eredeti adatcsomag bitjeit, úgy, hogy közben az átvitel sebessége nem csökken (észrevehetően). Ennek hála a maximális jelveszteség értéke nem változott, a PCIe 5.0-hoz hasonlóan 36 dB-es értéket állapított meg a PCI-SIG.

A PAM4 másik hátulütője, hogy hozzá kell igazítani az átvitelben résztvevő összes áramkört, amely áttervezéseket, ezzel pedig további kiadásokat kíván majd a gyártók oldaláról. Mindeközben a korábbi, NRZ módot is meg kell tartani, hisz csak ezzel maradhat meg a korábbi PCIe verziót támogató eszközök kompatibilitása, amely borítékolhatóan több munkaórát kíván majd a mérnökök részéről. Mindez azonban vélhetően nem jelent majd túl nehezen megugorható kihívásokat, a PAM4-et ugyanis viszonylag régóta alkalmazza az ipar, többek között az ultra-high-end hálózatos eszközöknél (pl. 100-400 gigabites Ethernet).