A következő Xeonnal tarolni akar az Intel

Alig néhány napja mutatkozott be a szerverekbe szánt Ice Lake-SP, külföldi híroldalak azonban már az utódról cikkeznek. A kiszivárgott adatok alapján tetemes előrelépésre lehet számítani. Az Intel célja világos: meg kell verni az AMD Epyc-et.

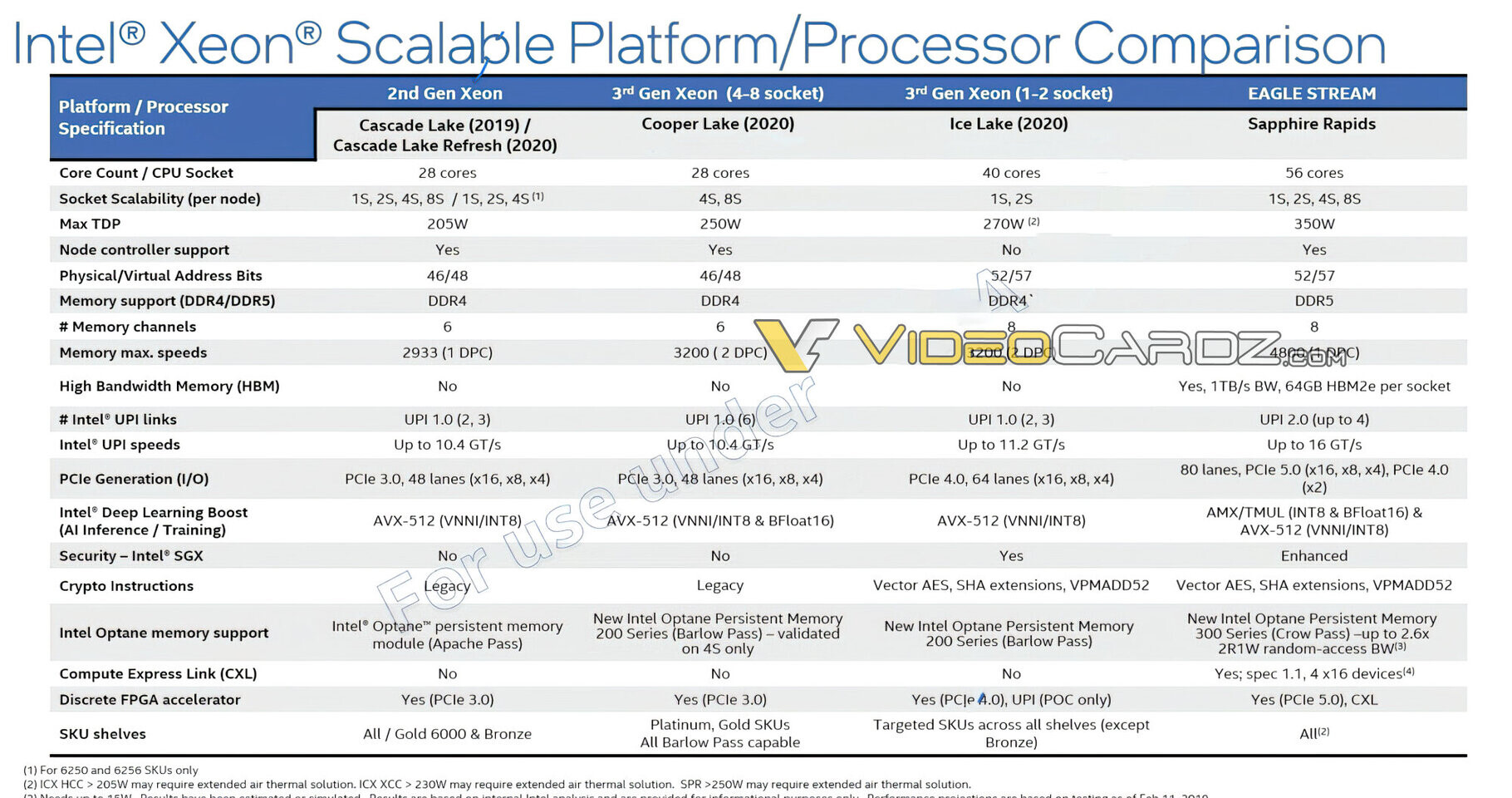

A negyedik generációs Xeon Scalable család alapjául szolgáló Sapphire Rapids fejleszési munkálatai előrehaladott állapotban vannak, ami optimális esetben 2022-es piaci bemutatkozást jelenthet. A kiszolgálókba szánt CPU minden téren számottevő előrelépést jelenthet majd az Intel akutális termékeihez képest. Az új mikroarchitektúrának hála tovább növekszik az IPC, tovább emelkedik a magszám, megjelenik a DDR5 és a PCIe Gen5 támogatása, illetve HBM2e memória is felkerülhet a processzorok tokozására.

Jogod van tudni: mankó kirúgáshoz, munkahelyi szkanderezéshez Ezúttal egy mindenki számára kötelező, de laza jogi különkiadással jelentkezünk. Ennyi a minimum, amit munkavállalóként illik tudnod.

A processzormagok minden bizonnyal a Golden Cove kódnéven fejlesztésre épülnek, amelyek az Intel korábbi közleménye szerint számottevő növekedést hoznak IPC-ben. A vállalat továbbá gépi tanulásos (INT8, BFloat16), hálózatos, illetve biztonsági fejlesztéseket és optimalizációkat ígért korábban a Golden Cove-hoz. Az egy órajel alatt végrehajtható műveletek növekedésével párhuzamosan a magszám is emelkedik. A kiszivárgott adatok szerint 40 százalékkal 56 darabra növekszik a végrehajtók száma, amely bár jelentős ugrás, az érték még mindig elmarad az AMD Epyc 64 magjától. Ezzel kapcsolatban az jelenti a fő kérdést, hogy az új mikroarchitektúra tudják-e majd kompenzálni az alacsonyabb magszámot.

Az Intel a magokat átölelő körítéshez is komolyan hozzányúl. A következő évek trendjeinek megfelelően megjelenik a PCI Express 5.0 támogatás, amit 64 helyett 80 sávval lehet majd kiaknázni. Ezzel párhuzamosan a DDR szabvány ötödik generációja is megérkezik. A Sapphire Rapids legfeljebb 4800 MHz-es modulokat támogat majd az Ice Lake-SP-vel bevezetett nyolc darab memóriacsatornán keresztül. Ennél érdekesebb a HBM2e támogatás, mely alapján modelltől föggően integrált memóriával érkeznek bizonyos modellek. Ennek kapacitása egészen 64 gigabájtig skálázódhat legfeljebb 1 TB/s sávszélesség mellett. Az egyelőre nem világos, hogy a fedélzeti memória milyen szerepet kap majd a hierarchiában, azaz gyorsítótárként, operatív tárként, esetleg ezek valamilyen hibrideként funkcionál-e majd az integrált HBM2e.

Mindezek mellett az egyes processzorok közötti interkonnekt szerepét betöltő UPI is sokat gyorsul, 11,2-ről egészen 16 GT/s-ra. A gyártástechnológia nem változik számottevően, marad a 10 nanométeres csíkszélesség, illetve annak egy továbbfejlesztett variánsa érkezik. Vélhetően ez, vagyis a kisebb gyártástechnológiai ugrás az egyik oka annak, hogy még tovább, 270-ről egészen 350 wattig ugrik majd a következő generációs Xeonok fogyasztási keretének maximuma.