Saját szerverprocesszorral könnyítené helyzetét az Nvidia

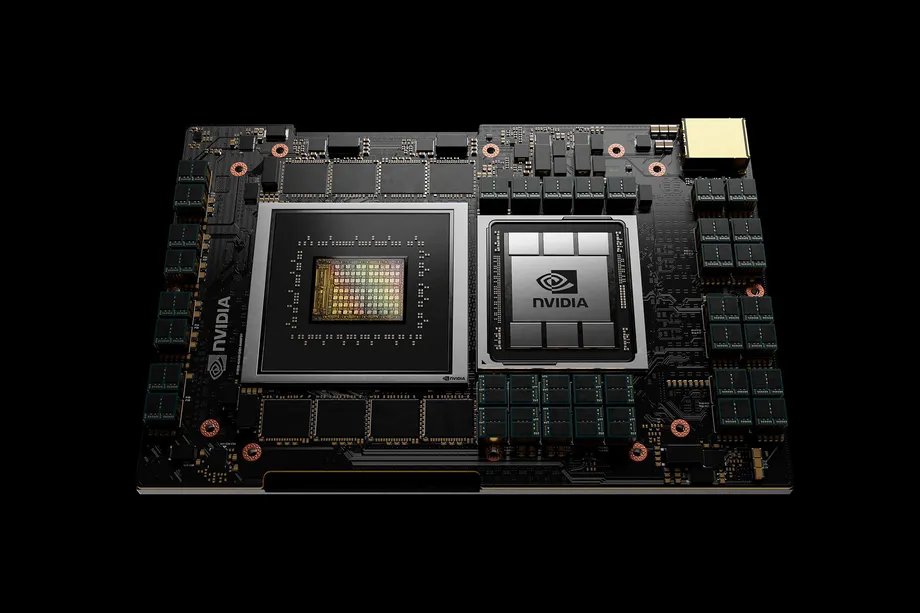

A rendkívül sikeres adatközpontos GPU-k mellé saját, ARM-alapú CPU-kat tervez az Nvidia. A Grace Hopper programozóról elnevezett fejlesztést elsősorban házon belül összeállított kiszolgálóiba szánja a tervezőcég. Kérdés, hogy sokadik próbálkozóként az Nvidia sikerre tudja-e vinni a kiszolgálós piacon az ARM utasításarchitektúráját.

A Grace kódnéven futó fejlesztést elsősorban nagy neurális hálózatoknál jellemző munkafolyamatokhoz tervezi az Nvidia. Jensen Huang, a vállalat elnök-vezérigazgatója csak néhány alapvető paramétert osztott meg a végleges formájától még távol álló chipről, illetve platformról. A CPU-ba az ARM valamely következő generációs, kifejezetten szerverekhez tervezett Neoverse magjai kerülnek, vélhetően már az ARM v9 utasításarchitektúrára építve. Arról egyelőre csak találgatni lehet, hogy pontosan hány darab egységgel számol az Nvidia, azonban vélhetően legalább 64-96 mag kerül majd a végleges a lapkába.

USA Tech Hub: ahonnan a passzátszél fúj Minden, ami a technológiai szektorban történik, jellemzően az USA-ból indul.

A CPU mellé LPDDR5X szabványú (ECC-s) rendszermemóriát tervez az Nvidia, amely ilyen formátumú modulok híján az alaplapra forrasztva kap majd helyet. Az előzetes információk alapján a cég tetemes, processzoronként 500 GB/s feletti sávszélességgel kalkulál. A CPU-CPU, valamint a CPU-GPU adatkapcsolatot egyaránt a házon belül fejlesztett NVLink negyedik generációja biztosítja majd. Mindkét esetben hatalmas sávszélességet ígér a cég: a CPU-CPU link 600, a CPU-GPU pedig 900 GB/s feletti értékkel fog rendelkezni, így az egyes processzorok közötti adatkapcsolat bizonyosan nem jelenthet majd szűk keresztmetszetet.

Az NVLink vélhetően döntő szempont lehetett a Grace mellett. Érthető okokból ugyanis sem az Intel, sem pedig az AMD nem támogatja az Nvidia saját fabricját, mely híján jelenleg az iparági szabványt jelentő, lényegesen lassabb PCI Expressre kénytelen támaszkodni szervereiben a cég. A piacon elérhető legújabb, Gen4 esetében ez legfeljebb 64GB/s sávszélességet jelent, amely töredéke az említett, ugyancsak negyedik generációs NVLink értékének. A tervezőcég saját fejlesztése bár évekkel ezelőtt bekerült az IBM POWER9-be, ma már nyilvánvaló, hogy egyszeri esetről volt szó, a POWER10-ből ugyanis kimaradt a blokk.

Az NVLinknek hála nem csak az elérhető sávszélesség ugrik majd meg jelentősen. Cache-koherens interkonnekt lévén ugyanis az NVLinkkel összekötött CPU-k és különféle gyorsítók (az NVidia esetében GPU-k) elérhetik egymás gyorsítótárait és rendszermemóriáit. A processzorok ezzel folyamatosan monitorozhatják egymás memóriáinak tartalmát, és, ha az egyik olyan adatot módosít, ami egy másiknál gyorsítótárazva van, akkor az inkonzisztencia elkerülése végett érvénytelenítheti az utóbbit, gyorsabb, optimális rendszerműködést eredményezve. Az Nvidia állítja, elméletben akár tízszeres sebességnövekedést is jelenthet a Grace egy kellően nagy neurális hálónál, mely alapján valóban megérheti a befektetést a saját processzor fejlesztése.

Kinek kell ez?

Az Nvidia elsősorban saját, HGX és DGX típusú szervereibe, illetve nagy szuperszámítógépek megrendelőnek szánja processzoros fejlesztését. Az óvatos hozzáállás mögött részben az ARM eddigi szerveres bukdácsolásai állhatnak. Az architektúrát már több nagy szereplő (pl. Qualcomm) is megpróbálta sikerre vinni a kiszolgálós piacon, ám ezek eddig rendre bukásnak bizonyultak a piacot uraló x86-os platformokkal szemben. Azzal, hogy az Nvidiának nem kell (vagy nem minden esetben kell) közvetlenül konkurálnia az Intellel és az AMD-vel, lényegesen könnyebb lehet majd a Grace helyzete.

A processzoros fejlesztéshez kapcsolódóan a vállalat egyúttal bejelentette, hogy két nagy szuperszámítógép már biztosan épül a Grace-re. Az egyik rendszert a svájci CSCS, a másikat pedig a Los Alamos-i LANL rendelte, összeállításukat pedig HPE alá tartozó Cray végzi majd. CSCS állítja, az Alps névre keresztelt rendszert gépi tanulásos munkafolyamatok mellett tradicionális HPC-s számításoknál is kihasználják majd.