Mi állíthatja meg a félvezetős bérgyártás nagyágyúját?

Sínen van a TSMC 3 nanométeres csíkszélessége - állítja a rendszerint megbízható DigiTimes.

A tajvani hírmagazin szerint a munkálatok állapotát látván optimista a piacvezető bérgyártó, mely az első kereskedelmi forgalomba kerülő 3 nanométeres chipeket a korábban megcélzott 2023-as dátum helyett már 2022-ben legyárthatja dedikált vadiúj üzemében. Ezt megelőzően az 5 nanométer kapja a főszerepet, melynek tömegtermelését valamikor a jövő év második negyedévében indítja be a TSMC, minden bizonnyal az Apple és a HiSilicon megrendelései alapján.

A tajvani bérgyártó már korábban közölte, hogy az ügyfelek megkapták a 3 nanométeres lapkák tervezéséhez szükséges alapvető paramétereket. Részletekbe egyelőre nem bocsátkozott a TSMC, így nem lehet tudni, hogy milyen tranzisztorokat alkalmaz majd, illetve a gyártásnál pontosan mekkora szerepet kap az EUV, vagyis a skálázáshoz már elengedhetetlen extrém ultraibolya fényt alkalmazó levilágítás. 3 nanométeren várhatóan már minden adott lesz, hogy a gyártás akár összes fázisában alkalmazható legyen az EUV. Ennél nagyobb kérdés a tranzisztor típusa. Az első számú konkurens Samsung hónapokkal ezelőtt közölte, hogy ilyen alacsony csíkszélességnél már nem éri meg FinFET tranzisztorokat alkalmazni. A dél-koreai vállalat ezért GAA-ra (Gate-All-Around), vagy más néven nanohuzal-tranzisztorra építi 3 nanométeres eljárását, amely a FinFET-nél valamelyest kedvezőbb elektromos tulajdonságokkal rendelkezik, miközben a skálázhatóságot számottevően kitolja.

Jogod van tudni: mankó kirúgáshoz, munkahelyi szkanderezéshez Ezúttal egy mindenki számára kötelező, de laza jogi különkiadással jelentkezünk. Ennyi a minimum, amit munkavállalóként illik tudnod.

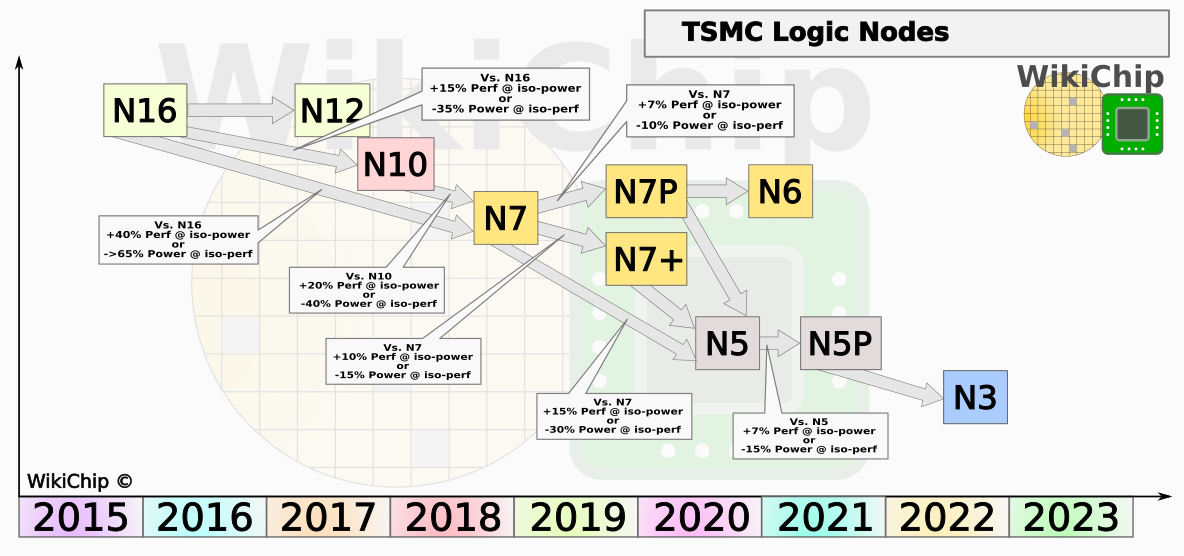

A jövőre érkező 5 nanométer a bérgyártó első "igazi" EUV-s eljárása lesz, mely akár 80 százalékkal növelheti a sűrűséget, ami azonos tranzisztorszámmal kalkulálva akár 45 százalékkal kisebb területű chipeket jelenthet. Disszipáció, illetve a tranzisztorteljesítmény tekintetében már jóval kisebb ugrást ígér a CLN5FF, hisz előbbinél 20, utóbbinál pedig csak 15 százalékos lehet a javulás dizájntól függően. A TSMC vélhetően ezért, vagyis a korábban beígért szerény előrelépések miatt jelentette be augusztusban az N5P finomhangolást, amely a tervezőpartner igényeitől függően a teljesítményt növeli 7 százalékkal, vagy a fogyasztást csökkenti 15 százalékkal az első generációs 5 nanométerhez képest.

Az elmúlt néhány évben látott koreográfiának megfelelően valószínűleg továbbra is az Apple lesz az első, amely meglovagolja a legújabb csíkszélességeket. Ennek megfelelően a jövő őszre datált A14-es rendszerchip lehet a piac első 5 nanométeres lapkája, amit 2021-ben az 5+ (N5P) nanométeren készülő A15, 2022-ben pedig a 3 nanométeres A16 követhet. Az Apple-t a jellemzően szerényebb volumennel dolgozó HiSilicon, majd pedig a Qualcomm követheti néhány hónapos késéssel, az x86-os processzorokat és GPU-kat tervező AMD pedig 9-12 hónappal az Apple után állhat át a kisebb csíkszélességekre, alacsonyabb kockázat, valamint költségek mellett.

Intel: nézzünk a számok mögé!

Bob Swan, az Intel elnök-vezérigazgatója egy pár nappal ezelőtti konferencián kiemelte, hogy a vállalat 7 nanométere könnyedén felveszi majd a versenyt a TSMC 5 nanométerével, az x86-os chipgyártó 5 nanométerét pedig a tajvani vállalat 3 nanométerével lehet majd egy lapon emlegetni. Az elmúlt évek trendjei alapján Swannak könnyen igaza lehet, a bérgyártók ugyanis nagyon szabadon értelmezik a nanométereket, mintegy marketingeszközként alkalmazva a számokat. Swanéknak ugyanakkor rossz hír lehet, hogy a fentiek alapján a TSMC már jövőre bevetheti az 5 nanométert, az annak nagyjából megfelelő 7 nanométerét viszont csak 2021 végére ígéri az Intel, bő 1 éves lemaradással. Amennyiben a bérgyártó képes lesz tartani az ütemet, szűk egy éven belül elkészülhet 3 nanométere, amellyel könnyen visszaveheti a vezető gyártástechnológiai címet az Ázsia legértékesebb vállalatának kikiáltott TSMC.