Komolyabb módosításokat hozhat a Zen 3-mal az AMD

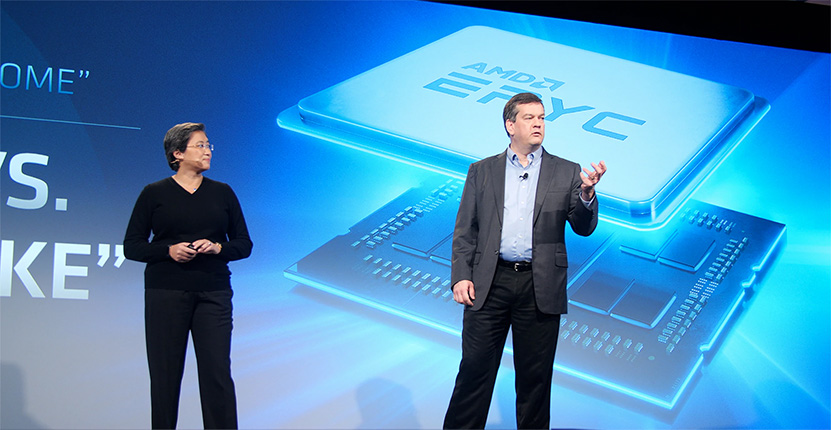

Meglepő kijelentést tett az AMD adatközpontos és beágyazott termékekkel foglalkozó divíziójának vezetője, Forrest Norrod. A felső vezetésben helyet foglaló szakember szavai alapján a jövőre esedékes Zen 3 egy teljesen új mikroarchitektúra lesz, a teljesítménynövekedés mértéke pedig ennek megfelelően alakul majd.

Mindez annak tükrében meglepő, hogy a korábban kiszivárgott információmorzsák alapján sokkal inkább egy inkrementális, szerény javulást kínáló fejlesztésekre lehetett számítani. Norrod nem bocsátkozott további részletekbe, így egyelőre nem tudni, hogy a "vadiúj mikroarchitektúra" pontosan mit takar, mint ahogy az sem, hogy mindez számítási teljesítményben mekkora növekedést hozhat.

A szakemberrel a TheStreet tőzsdei magazin beszélgetett, amely többek között azt próbálta kideríteni, hogy a 2020-ra datált Zen 3 mekkora előrelépést produkál majd az idén megjelent Zen 2-höz képest. Norrod a témát firtató kérdésre azt válaszolta, hogy a fejlődés mértéke összhangban lesz azzal, amit egy teljesen új mikroarchitektúrától várhat az iparág. Utóbbit, vagyis a mikroarchitektúrára vonatkozó szavakat bár több módon is lehet értelmezni, mégsem valószínű, hogy az AMD már jövőre egy nulláról újrarajzolt fejlesztést mutat be. Reálisabbnak tűnik, hogy a 2017-ben megjelent alapokat megtartva végzett kisebb-nagyobb módosításokat a tervezőcég, amelyek összességét Norrod egy vadiúj fejlesztésként értékeli.

USA Tech Hub: ahonnan a passzátszél fúj Minden, ami a technológiai szektorban történik, jellemzően az USA-ból indul.

Utóbbi módszerrel számottevő, átlagosan 13 százalékos IPC növekedést sikerült kihozni a nyáron megjelent Zen 2-ből. A Zen 3-tól eddig szerényebb előrelépést vár a szakma, amely azonos órajel és magszám mellett egy számjegyű, 7-8 százalékos javulásra számít. Norrod szavai alapján viszont akár ennél magasabb, 10 százalék feletti is lehet a gyorsulás, habár a múltban több példa is volt arra, hogy az alapoktól újragondolt mikroarchitektúrák gyakorlati teljesítménye csalódást okozott. Erre jó példa az AMD Bulldozere, amely bár a maga nemében innovatív volt, a újítások mértéke és valós felhasználás mellett tapasztalt előrelépéssel finoman szólva sem volt összhangban. Az alelnök szavai ugyanakkor arról árulkodnak, hogy a Zennel nem esik ugyanabba a gödörbe az AMD, amely az Intel pár éve elhagyott tikk-takk stratégiájának megfelelően az egyik évben a gyártástechnológiai vált, a másikban pedig a mikroarchitektúrális fejlesztéseket helyezi előtérbe. Norrod szerint előbbit a Zen 2-vel sikeresen kipipálták, a jövőre érkező Zen 3-mal pedig a mikroarchitektúra következik.

Még október elején kiderült, hogy az elmúlt hónapokban többször emlegetett SMT4, azaz a magonkénti négy végrehajtószál kimarad a Zen 3-ból. E helyett a processzormagokat tartalmazó lapkához, pontosabban annak felépítéséhez nyúl hozzá az AMD. A Zen első iterációjával bemutatott CCX konfiguráció négy darab magból és ugyanennyi L3-szeletből állt, mely utóbbi szeletek mérete 1 vagy 2 megabájt lehet. A grafikus egységeket nem tartalmazó lapkadizájnokba két CCX-et tervezett az AMD, amelyek adatcseréje egy koherens adatbuszon történik. A kapcsolat nem közvetlen, az egy-egy CCX a Data Fabrichoz kapcsolódik, amely bizonyos esetekben szűk keresztmetszet lehet. Az AMD tervezői a Zen 3-nál változtatnak a rendszeren, a 4+4 magot már az L3 gyorsítótáron keresztül kapcsolják össze, vagyis a harmadszintű cache gyakorlatilag összeolvad. Ezzel egyetlen lapka kétszer 16 megabájt helyett egyetlen egybefüggő 32 megabájtos (vagy akár ennél nagyobb) tárat tartalmaz majd, gyorsítva a lapkán belüli magok adatkommunikációját.

A magok és a cache elrendezése mellett minden bizonnyal egyéb optimalizációkat és módosításokat is eszközölt az AMD, azonban ezek mértéke egyelőre Norrod kijelentése ellenére is homályos. A magszámhoz viszont biztosan nem nyúl a tervezőcég, a szerverprocesszorokat képviselő Epyc szériánál 64 marad a maximális egység. A további növelése a Zen 4-gyel folytatódhat, amelyhez a 7 nanométernél lényegesen nagyobb tranzisztorsűrűségre képes 5 nanométeres csíkszélesség nyújthatja az alapot 2021-ben.