Többszálúsítás helyett felépítésben újít a Zen 3

Elárult pár részletet a jövőre érkező Zen 3-as fejlesztéséről az AMD: SMT4 nem lesz, átrajzolt topológia viszont igen.

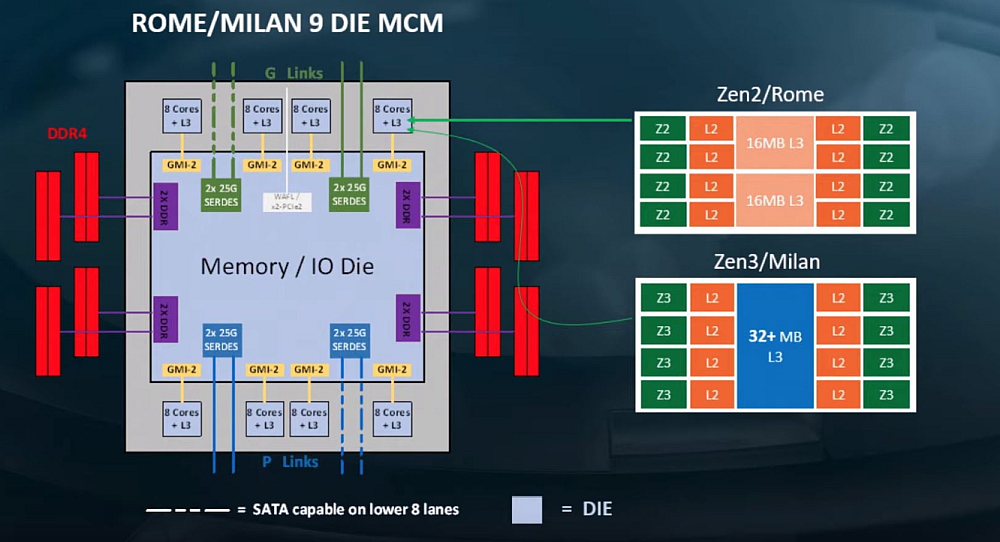

A Leicesterben tartott HPC-AI Advisory Council konferencián a tervezőcég egyik szakembere a közelmúltban megjelent, illetve a következő nagyjából két évben esedékes fejlesztésekről beszélt. Az elhangzottak alapján az AMD egyelőre nem alkalmazza a magonkénti négyszálú végrehajtást, vagyis az SMT4-et, marad a jelenleg is alkalmazott SMT(2). A processzormagokat tartalmazó lapka felépítéséhez azonban hozzányúltak a tervezők. A végrehajtóegységek, illetve az azokhoz kapcsolódó gyorsítótárak elrendezése változik.

Az SMT4 implementálása már hónapok óta szóbeszéd témája. Legutóbb szeptember végén közölte a Hardwareluxx, hogy az AMD jövőre esedékes processzorai támogathatják a magonkénti négyszálas párhuzamos végrehajtást, amellyel bizonyos felhasználási körülmények között számottevő gyorsulás érhető el. A vállalat munkatársa szerint azonban ez nem fog megtörténni, a jövőre érkező Zen 3-nál még biztosan marad a magonkénti legfeljebb kétszálas végrehajtás. Ez azonban még nem jelenti azt, hogy az AMD teljesen elvetette volna a fejlesztés lehetőségét, a következő generációk valamelyiknél még sorra kerülhet az implementáció. Elképzelhető, hogy az AMD a Zen 4-re tartogatja az SMT4 bevetést, amelyhez a 7 nanométerénél lényegesen nagyobb tranzisztorsűrűségre képes 5 nanométeres csíkszélesség nyújthatja az alapot, legkorábban 2021-ben.

Az SMT4-helyett a processzormagokat tartalmazó lapkát, pontosabban annak felépítéséhez nyúl hozzá az AMD. A Zen első iterációjával bemutatott CCX konfiguráció négy darab magból és ugyanennyi L3-szeletből áll, mely utóbbi szeletek mérete 1 vagy 2 megabájt lehet. A grafikus egységeket nem tartalmazó lapkadizájnokba két CCX-et tervezett az AMD, amelyek adatcseréje egy koherens adatbuszon történik. A kapcsolat nem közvetlen, az egy-egy CCX a Data Fabrichoz kapcsolódik, amely bizonyos esetekben szűk keresztmetszet lehet. Az AMD tervezői a Zen 3-nál változtatnak a rendszeren, a 4+4 magot már az L3 gyorsítótáron keresztül kapcsolják össze, vagyis a harmadszintű cache gyakorlatilag összeolvad. Ezzel egyetlen lapka kétszer 16 megabájt helyett egyetlen egybefüggő 32 megabájtos (vagy akár annál nagyobb) tárat tartalmaz majd, gyorsítva az egy lapkán belül lévő magok adatkommunikációját.

Jogod van tudni: mankó kirúgáshoz, munkahelyi szkanderezéshez Ezúttal egy mindenki számára kötelező, de laza jogi különkiadással jelentkezünk. Ennyi a minimum, amit munkavállalóként illik tudnod.

A magok és a cache elrendezése mellett minden bizonnyal egyéb optimalizációkat és módosításokat is eszközölt az AMD, amely a magszámot viszont nem emeli, a szerverprocesszorokat képviselő Epyc szériánál marad a maximális 64 egység. A magszám további növelését a már említett Zen 4-gyel folytathatja az AMD. A rendezvényen kiderült, hogy a Zen negyedik iterációjára alapozó Genoa szerverprocesszorok új tokozást (és foglalatot), valamint DDR5 és vélhetően PCI Express 5.0 támogatást is kapnak.