Pedzegeti a PLC NAND-ot a Toshiba

Elkészítette a PLC (Penta-Level Cell), vagyis a cellánként 5 bit tárolására képes NAND flash első kísérleti verzióját a Toshiba.

A BiCS 4 fejlesztésen alapuló megoldás a QLC-nél 25, a TLC-nél 66 százalékkal több adat tárolására képes egységnyi cellaszám mellett. Az adatsűrűsűég növelésével egységnyi szilíciumból nagyobb kapacitást lehet kinyerni, amely egyenes utat jelenthet az árak további mérséklődéséhez. A Toshiba konkrétumokról egyelőre nem beszélt, ám a korábbi szintek alapján a cellákban tárolható adatbitek növelésével várhatóan tovább csökken a műveletvégzés sebessége, illetve a cellák terhelhetősége, vagyis az élettartam.

A PLC NAND-ok piaci elérhetősége tehát várhatóan még évekre van, a cellánkénti 5 bit miatt ugyanis több kihívással is meg kell birkózni. A NAND cellák bizonyos töltésszint formájában tárolnak adatot. Az SLC esetében (single-level cell) ez roppant egyszerű, vagy van töltés, vagy nincs. Az ilyen cellák nagyon gyorsan írhatóak, pofon egyszerű a felprogramozás. Az MLC (multi-level cell) esetében már több különböző töltésszint van, ami javítja a bitsűrűséget az írási sebesség rovására: a felprogramozás után ugyanis vissza kell ellenőrizni a töltöttség szintjét, és ha az nem sikeres, akkor meg kell ismételni azt. A hiba probléma pedig a tárolt bitek számával exponenciálisan nő: a TLC már három bitet tárol, vagyis nyolc különböző töltési szintet használ, miközben a szélesebb körben idén megjelent QLC már tizenhat szintet kíván.

Jogod van tudni: mankó kirúgáshoz, munkahelyi szkanderezéshez Ezúttal egy mindenki számára kötelező, de laza jogi különkiadással jelentkezünk. Ennyi a minimum, amit munkavállalóként illik tudnod.

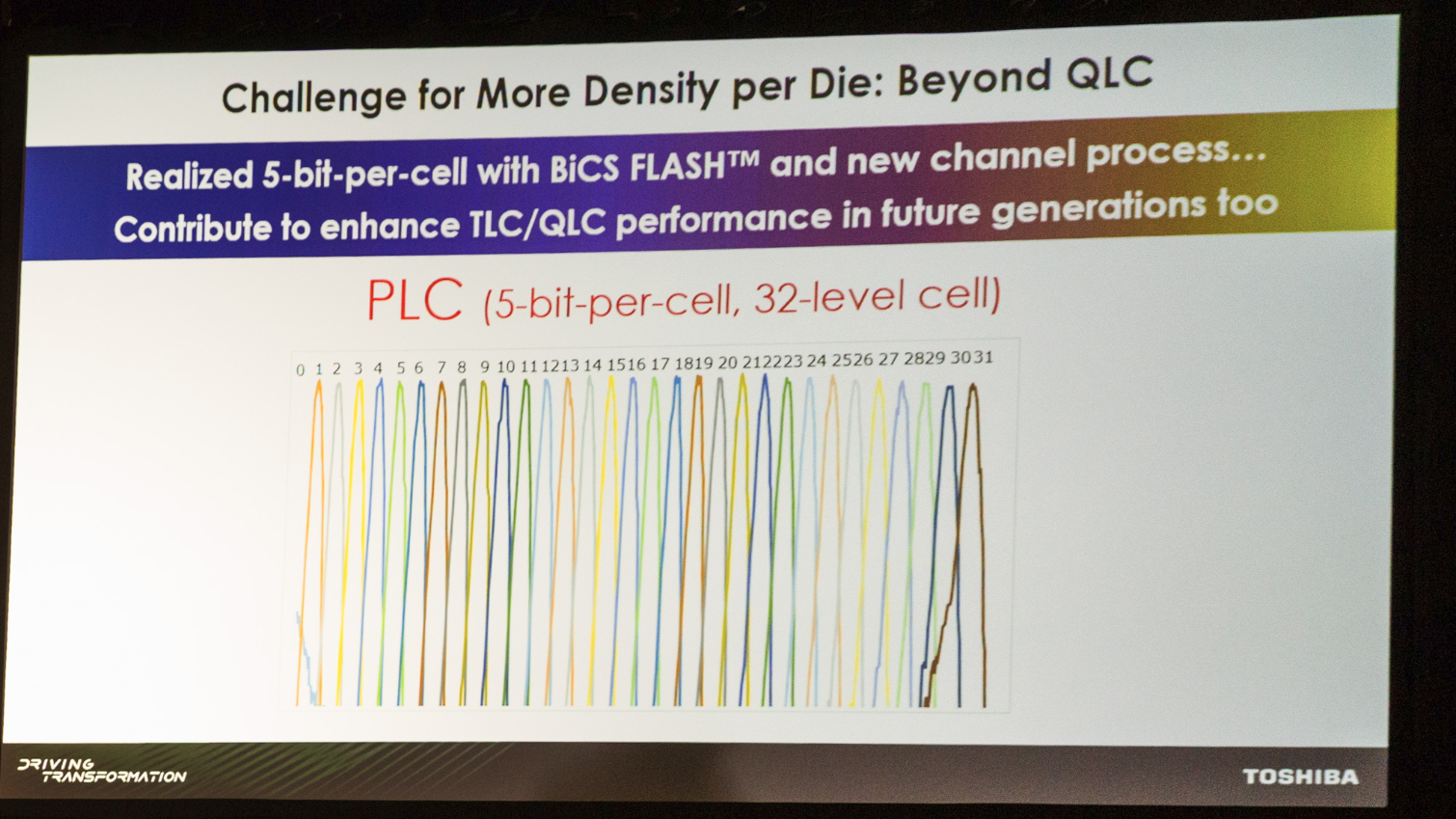

Ennek megfelelően a PLC-hez az utóbbi duplája, azaz harminckét töltési szint szükséges. Mindez még pontosabb feszültségértékeket kíván meg a cellák megfelelő programozásához, illetve az adatok későbbi sikeres és gyors kiolvasásához. A cellák gyorsabban elhasználódhatnak, ugyanis kisebb a feszültségtartományok közötti terület, ahova a szilíciumdioxid réteg "kopása" miatt még hiba nélkül ki tud "futni" a vezérlés. Ezen kívül, ha egy cella 5 bit adatot tárol, akkor a programozási műveletek is gyakoribbak lehetnek benne, hisz egyetlen bit módosítása (pl.: 00000->00001) is épp ugyanazt a műveletet igényli, mintha mindhármat átírná a vezérlés (pl.: 01010->10101).

A cellák programozhatósága ezzel tovább romlik, ugyanakkor bizonyos megoldásokkal kompenzálni lehet a negatív tendenciát. Ehhez a gyártók elsősorban fejlett algoritmusokat, adaptív írási/olvasási technikát, illetve komplex DSP ECC rendszert alkalmaznak. A Toshiba arról egyelőre nem beszélt, hogy pontosan milyen megoldást alkalmaz majd a kihívások kezelésére, azonban ennek megválaszolására még vélhetően legalább 2-3 éve van a gyártónak, 2022 előtt ugyanis nem valószínű, hogy piacra kerülne a PLC NAND.