Rekordgyorsasággal készült el a PCI Express 5.0

Alig vetette meg a lábát a PCI Express 4.0, máris itt az utód. Az 5.0-s fejlesztés ugyanakkor még messze van a piaci megjelenéstől, amire még legalább 1,5-2 évet kell várni.

A korábbi ütemtervnek megfelelően jelentette be a PCI Express 5.0-s verzióját a szabványt felügyelő iparági szervezet, a PCI-SIG. A mindössze másfél év alatt elkészített specifikációk szerint a busz rádupláz az előd 4.0 sávszélességére, melynek hála egy 16 sávos csatoló estében a csúcsérték elérheti a másodpercenkénti (közel) 64 gigabájtot. Mindeközben a visszafele kompatibilitás biztosított maradt, tehát a 5.0-s eszközök működhetnek majd a korábbi, 4.0-t vagy annál korábbi verziót támogató alaplapokban, illetve a 5.0-s slotokban is működnek majd a szabvány régebbi verzióját támogató eszközök. A PCI-SIG szerint a legújabb fejlesztés tovább erősíti a szabvány de facto vezető státuszát a nagy teljesítményű buszok piacán.

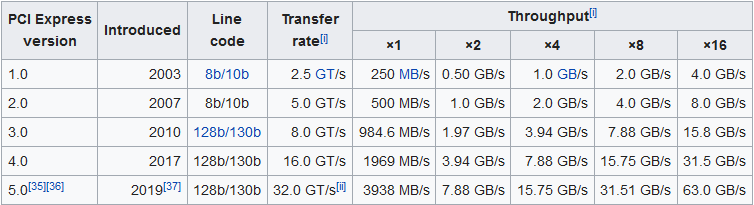

Az előrelépés vitathatatlan: Míg a PCIe 2.0 egyetlen sávon 5 GT/s (500 MB/s) átviteli sebességet kínált, addig a 2011-ben megjelent 3.0 "csak" 8 GT/s-re (985 MB/s) emelte a tempót. Utóbbira a 2017-ben megjelent 4.0 ráduplázott, a PCI Express busz ezen verziója egy sávon 16 GT/s-re (1969 MB/s) növelte az átviteli sebességet, amely a legnagyobb kiépítésű, 16 sávos csatlakozó esetében 31,51 GB/s-os sávszélességet jelent. A most bejelentett 5.0-s verzió tovább folytatja az azt megelőző két kiadás duplázását. A Gen5-re felkészített sávok 32 GT/s (3938 MB/s) tempóra képesek, ami x16-os kiépítés esetében kereken 63 GB/s-os átviteli sebességet eredményez. A PCI-SIG kiemeli, hogy ezt mindössze 18 hónap alatt sikerült elérni, ennyi idő telt el az amúgy szokatlanul lassan elkészült 4.0-s verzió véglegesítése óta. A rekordgyorsasággal elkészült munka háttere, hogy a Gen5 a meglévő fizikai interfészekre épít, a tervezők fel tudták használni a korábbi szabványok implementálásánál már elvégzett munkát.

Jogod van tudni: mankó kirúgáshoz, munkahelyi szkanderezéshez Ezúttal egy mindenki számára kötelező, de laza jogi különkiadással jelentkezünk. Ennyi a minimum, amit munkavállalóként illik tudnod.

Ahogy korábban, úgy jelen esetben is elsősorban szerverekben jöhet majd kapóra a jelentősen megnövekedett sávszélesség. Nem csoda, hogy a PCIe Gen5-öt támogató egyik első platformot az Intel hozhatja el Xeon processzoraira építve, valamikor 2021-ben. A Sapphire Rapids-SP a megújult mikroarchitektúra mellett az egyre több processzormag kiszolgálásához lassan nélkülözhetetlen DDR5-öt, illetve a PCI Express 5.0-t is elhozhatja az Eagle Stream platform alapjain. Ezzel párhuzamosan valószínűleg a konkurens AMD is implementálja a busz legújabb legújabb verzióját, amely kéz a kézben járhat majd a DDR5-ös memóriaszabvánnyal.

Vitán felül áll, hogy a Gen5-ös buszoknak van létjogosultsága, legalábbis a nagyvállalati termékek piacán. Egyre több all-flash tároló érkezik NVMe SSD-kkel, ezekben a rendszerekben pedig komoly előnyt jelentene a vonalankénti kétszeres sávszélesség. Ezt meglovagolva ugyanis egységnyi PCI Express sávra kétszer több SSD ültethető rá úgy, hogy a gazdavezérlő és a meghajtó közötti sávszélesség a 4.0-s rendszerhez képest változatlan marad. Ez azért fontos, mert így viszonylag alacsony felár mellett emelhető az SSD-k száma, az alaplap és a processzor komplexitása ugyanis nem nő jelentősen. Ezt a másik oldalról is meg lehet ülni, egységnyi sávot alapul véve duplázható a sávszélesség, ami egyes, teljesítményre kihegyezett rendszerek esetében jöhet kapóra. A másik, ugyancsak nagyvállalati felhasználási területet a gyorsítókártyák jelentik, melyeknél bizonyos esetekben szűkössé válhat a busz a gazdaprocesszorral való intenzív adatcsere során.