64 maggal licitál rá a 48 magos Xeonra az AMD

Leleplezte jövőre piacra kerülő második generációs Zen mikroarchitektúrájának, illetve Epyc processzorcsaládjának egyes főbb technikai paramétereit az AMD. Az első generációval kitaposott ösvényen tovább haladva egy meglehetően egyedi, "chiplet" felépítéssel próbál előnyre szert tenni a chiptervező, az egészen 64 magig skálázható, "Rome" kódnevű Epyc processzor ugyanis 9 különálló lapkából áll össze, amelyeket ráadásul eltérő gyártástechnológiával készülnek.

Fejlesztéseitől az AMD jobb skálázhatóságot és költséghatékonyabb gyártást remél, amelyre szükség is lesz ahhoz, hogy sikerüljön elérni a jövő évre kitűzött ambiciózus célt, azaz a 10 százalék feletti szerverpiaci részesedést. Az Intel ezt többek között egy 48 magos processzorral próbálja megakadályozni, mely fejlesztés az AMD koncepciójához hasonlóan különálló lapkákat drótoz össze egyetlen tokozáson.

A második generációs Epyc processzorok alapját a Zen mikroarchitektúra második iterációja adja. Bár az AMD egyelőre nem árult el minden részletet fejlesztéséről, annyit már tudni, hogy a tervezőcsapat teljesen újrarajzolta az L1 utasításcache-t, nőtt a micro-op cache kapacitása, fejlődött az elágazásbecslés és az előbetöltés hatékonysága, illetve 128-ről 256 bitesre szélesedett a L1D gyorsítótár és az FPU portja. Mindehhez idomul a módosított futószalag, végül, de nem utolsó sorban pedig a mikroarchitektúra a Spectre sebezhetőségekre gyógyírt jelentő javításokat is kapott.

Jogod van tudni: mankó kirúgáshoz, munkahelyi szkanderezéshez Ezúttal egy mindenki számára kötelező, de laza jogi különkiadással jelentkezünk. Ennyi a minimum, amit munkavállalóként illik tudnod.

Tervezőcég optimális esetben mindettől 25 százalékos IPC növekedést remél, a fejlesztésekből kevesebbet profitáló kódoknál pedig értelemszerűen ennél alacsonyabb lehet majd a gyorsulás mértéke. Az AMD az Zen utódokról is szót ejtett. A korábban beharangozott Zen 3, illetve az arra épülő processzorok 2020-ban kerülhetnek piacra a 7 nanométer második (EUV-s) generációjával, az újdonságnak számító Zen 4 pedig legkorábban egy évvel később, vélhetően 5 nanométeren érkezik. Ezzel immár biztossá vált, hogy a Zennek még jó néhány évig állnia kell a sarat a konkurens fejlesztésekkel szemben.

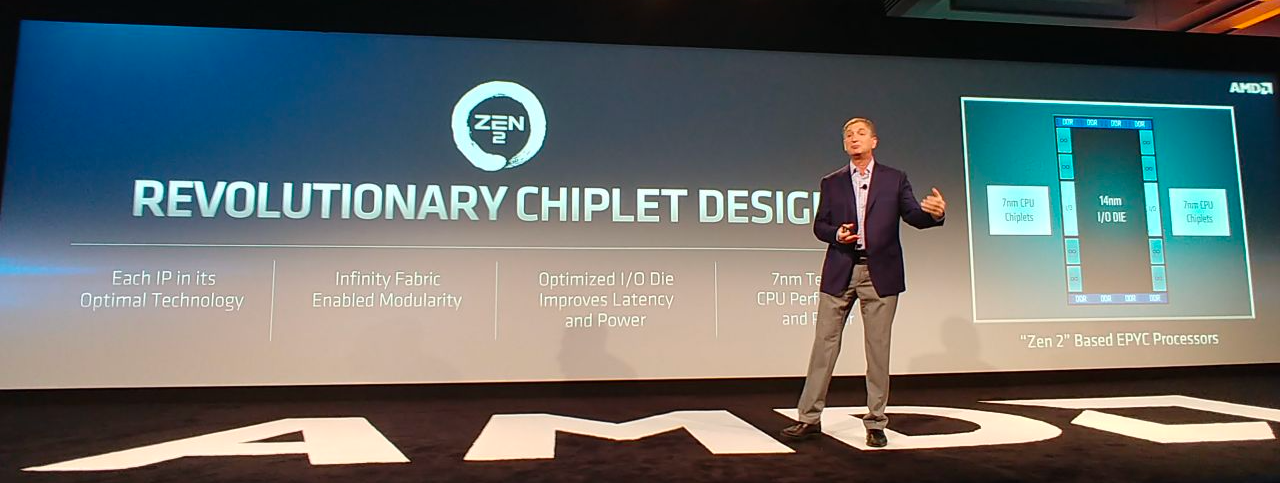

A verseny következő menetét azonban még a Zen 2-vel vívja meg az AMD, melyet piacképes terméknél még nem látott módon implementál az Epyc második hulláma. A "Rome" kódnevű szériához ugyanis két eltérő funkcionalitású lapkát tervezett a cég, melyek együttese adja a komplett, működképes processzort. Az alapot a már bejáratott, jó kihozatallal és relatíve alacsony költségek mellett vásárolható 14 nanométeres (14LPP) technológián készülő I/O chip adja. Ebbe a csíkszélesség szempontjából kevésbé kritikus egységek kerültek, így a lapka tartalmazza a nyolccsatornás memóriavezérlőt, a 128 darab Gen4(!) PCI Express sávot, illetve a további különféle integrált vezérlőket, például a SATA-t vagy az USB-t. A szemre nagyjából 300 mm2-es chip további fontos szerepe, hogy a csillag topológiának megfelelően HUB-ként összefogja és kiszolgálja a hozzá kapcsolt, Zen 2 processzormagokat tartalmazó, apró lapkákat. Ehhez készült az Infinity Fabric interkonnekt második iterációja, amely több mint duplájára, másodpercenként 42,67-ről 100 GB/s-ra emeli a kétirányú adatkapcsolat tempóját, így a lapkák közti sávszélesség vélhetően nem jelent majd szűk keresztmetszetet.

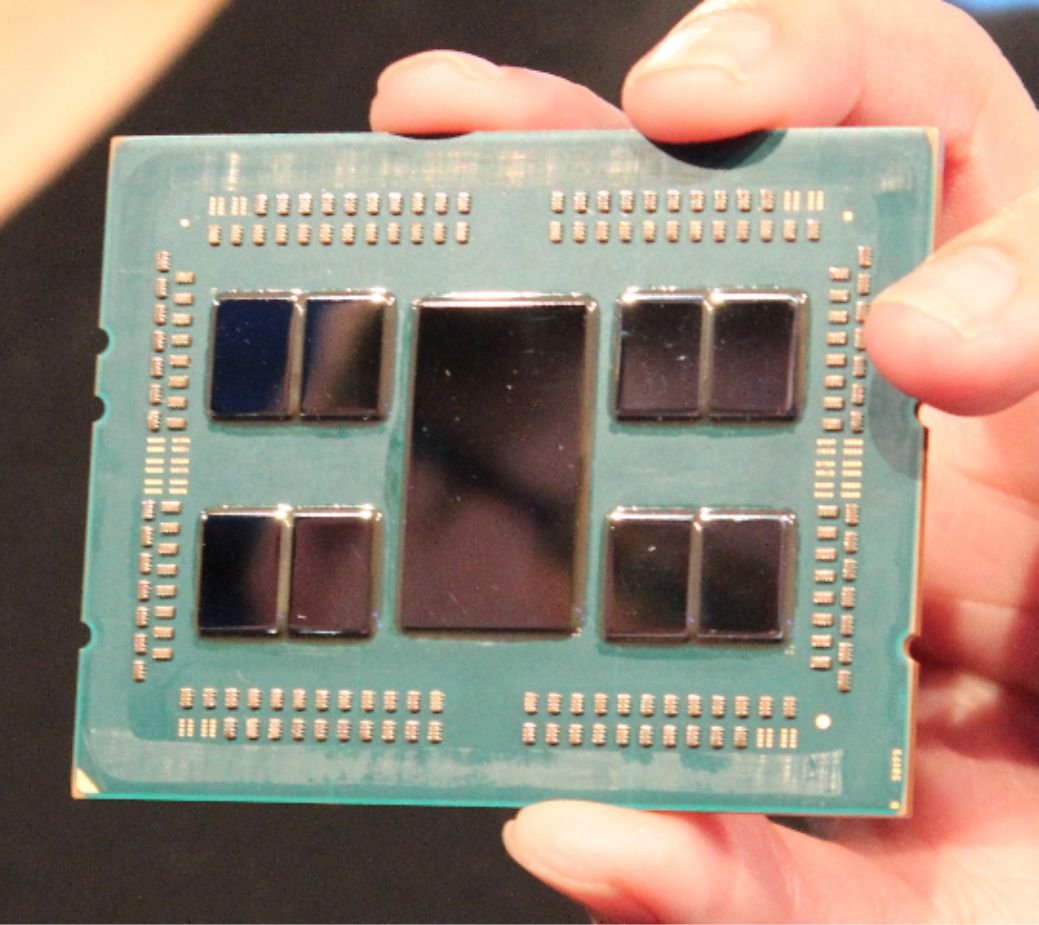

A központi I/O chip mellé szigorúan csak végrehajtóegységeket és gyorsítótárakat (na meg egy Infinity Fabric kontrollert) tartalmazó, nyolcmagos CCX (Core Complex) lapkák kerülnek. Ezek a piacon jelenleg található legfejlettebb, 7 nanométeres TSMC technológián készülnek. Ennek magyarázata, hogy a processzormagok rendkívül sokat profitálhatnak a fejlettebb gyártástechnológiából, a kisebb csíkszélességnek köszönhető alacsonyabb fogyasztáson és/vagy magasabb órajelen állhat vagy bukhat egy processzoros fejlesztés sikere. Bár az AMD nem közölt hivatalos értékeket, a bemutatott mérnöki tesztpéldány alapján mindössze 80 mm2 körül lehet egy nyolcmagos egység területe, amely rendkívül alacsony, alulról súrolja egy felsőkategóriás okostelefonos alkalmazásprocesszor értékét.

A CCX-ekből 8 darab párosítható majd az egyetlen I/O chiphez, de a skálázhatóság jegyében kevesebbel is működni fog a rendszer, így várhatóan lesznek 6 és 4 CCX-szel szerelt processzorok is, 48, illetve 32 maggal. A sok kisebb lapkát felsorakoztató felépítésnek hála jelentősen csökkenthetőek az előállítási költségek, nem utolsó sorban pedig felgyorsítható az egyes újabb gyártástechnológiák bevetése, nem kell megvárni, hogy kihozatal elérje a nagyobb lapkák gazdaságos előállításához szükséges szintet. A megközelítésnek egyetlen hátránya most is a hosszabb vezetékek miatti megnövekedett késleltetés, amely már az első generációban is tetten érhető volt.

Az AMD elvárásai szerint a fejlesztések hatására az Epyc első generációjához képest duplázódik a foglalatonkénti számítási teljesítmény. A pontosan kétszeresére emelkedő magszám fényében ez el is várható, azonban a 64 maghoz társuló fogyasztási keretről egyelőre nem beszélt az AMD, változatlan TDP mellett már jelentős előrelépés lenne a 100 százalék körüli gyorsulás. Emellett a tervezőcég elárulta, hogy lebegőpontos végrehajtás esetén négyszeres lehet az előrelépés, amely minden bizonnyal az AVX utasításkészlet kihasználásával lesz elérhető, melyhez ahogy az Intel esetében, megfelelően optimalizált kódra lesz szükség. Az AMD végül elhintette, hogy a jelenleg piacon lévő legerősebb kétfoglalatos Xeont könnyedén maga mögé utasította egyetlen második generációs Epyc mintapéldány az iparági sztenderd C-Ray benchamrkjában. Ebben a felállásban 64 darab Zen 2 mag szállt szembe 58 darab Skylake-kel, így az AMD előnye annyira nem meglepő.

Az Intel is (majdnem) rádupláz

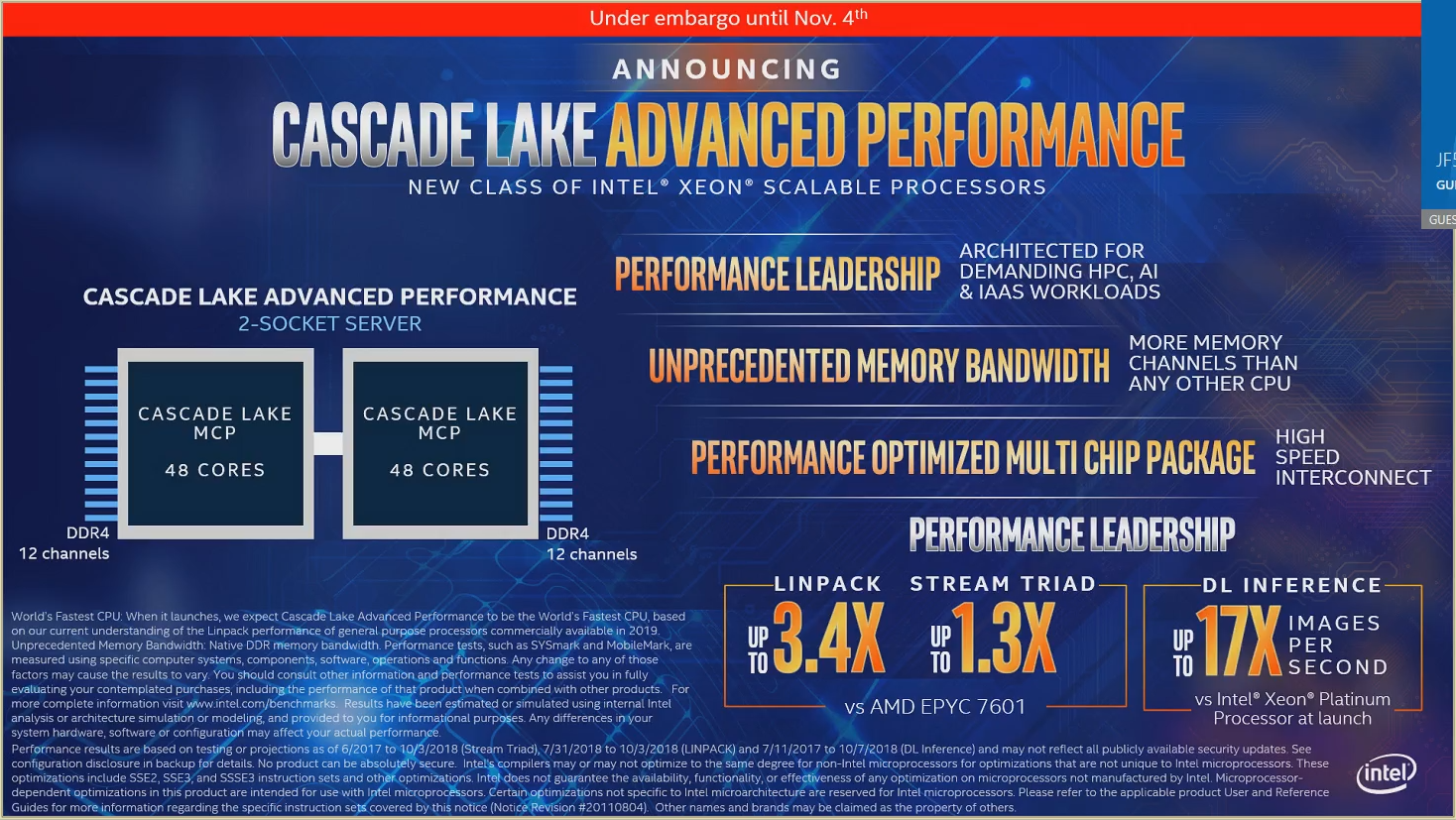

A sötét felhőként közelgő AMD-s magfölénnyel már az Intel is jó ideje tisztában lehet. Ennek fényében nem véletlen, hogy konkurensét pár nappal megelőzve bejelentette Cascade Lake-AP (AP: Advanced Performance) processzorát a gyártó. A napvilágot látott technikai részletek alapján a terméket az AMD fejlesztései inspirálhatták, az Intel ugyanis a tavaly még lesajnált módon két lapkát összedrótozva készítette el 48 magos Xeonját. Bár a gyártó ezt egyelőre nem erősítette meg, vélhetően a már piacon lévő 28 magos lapka enyhén áttervezett variánsából kerül két darab a tokozásra, a változatlan, 14 nanométeres gyártástechnológia korlátai miatt azonban az 56 darab magból le kell tiltani 8 darabot.

A két lapkás felépítés miatt a memóriacsatornák és a PCI Exrepss sávok száma is duplázódik, előbbiből így már nem kevesebb mint 12 darab lesz, ami rekordsávszélességet ígér. Várhatóan nem csak a sávszélesség, de a processzorok és az alaplapok gyártási költségei is új csúcsot állítanak fel, Cascade Lake-AP CPU-k ugyanis egy nem kevesebb mint 5903 darab érintkezőt felvonultató tokozást és foglalatot (LGA5903) kívánnak majd, mely az eddigieknél lényegesen magasabb komplexitást jelent. Az Intel szerint mindezért cserébe egy Epycet agyonverő platform jár majd, a cég a konkurens 32 magosával összevetve tetemes előrelépést ígér. Az AVX-et aktívan használó Linpackban 3,4-szeres, a memória-sávszélességet vizsgáló Stream Triadban pedig 1,3-szoros a csúcs Cascade Lake-AP AMD-hez mért előnye.

Arról egyelőre nincs információ, hogy mindezt mekkora TDP mellett produkálja az Intel fejlesztése, azonban a változatlan csíkszélességet figyelembe véve nem csak a foglalatonkénti számítási teljesítményben, de az ahhoz társuló disszipációban is új rekordok születhetnek. A hiányzó paraméterekre (beleértve az új processzorok árát) várhatóan december elején derül fény, ekkora tartja szerveres rendezvényét az Intel.