Jövőre debütálhat a Tesla saját fejlesztésű AI-gyorsítója

Elon Musk ígérete szerint tízszeres gyorsulást hozhat a házon belül tervezett platform, amely a tervek szerint már jövőre az utakra kerülhet.

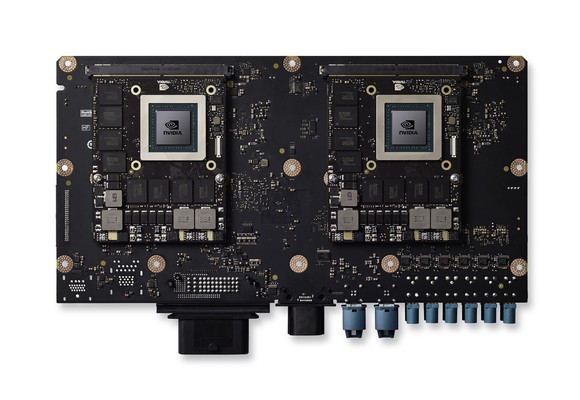

Pedzegeti saját fejlesztésű AI-gyorsítóját a Tesla. A vállalatot vezető Elon Musk szerint házon belül készülő platformjuk tetemes, egy nagyságrendű gyorsulást hoz majd a jelenleg alkalmazott Nvidia Drive PX 2-höz képest, amely előrelépésnek hála magabiztosan kivitelezhető lesz a teljesen önvezető rendszer. A vállalat ígéri, hogy hardverük csereszabatos lesz a jelenleg alkalmazott "hardware 2.0"-val, így a már piacon lévő járművek egy szervizelés keretein belül felfejleszthetőek lesznek. Amennyiben a tervezési folyamat végső fázisa is a tervek szerint halad, úgy a saját AI-gyorsító már jövőre munkába állhat.

A házon belül fejlesztett hardver híre nem új, a Tesla azonban eddig csak egyszer, a tavaly év végi gépi tanulásos NIPS konferencián hozta szóba fejlesztését, akkor is csak pár mondat erejéig. A munkálatok utolsó stádiumához közeledve, a múlt heti negyedéves pénzügyi jelentést taglaló konferenciahíváson ismét napirendre került a hardveres platform, amelynek fejlesztése Musk szerint nagyjából 2-3 éve zajlik. A vezérigazgató által csak "a világ legfejlettebb önvezető rendszerének" titulált hardver tízszer nagyobb tempót ígér a jelenleg alkalmazott, az Nvidia Drive PX 2 termékét takaró "hardware 2.0"-höz képest.

A Drive PX 2

A Drive PX 2

Introvertáltak az IT-ban: a hard skill nem elég Már nem elég zárkózott zseninek lenni, aki egyedül old meg problémákat. Az 53. kraftie adásban az introverzióról beszélgettünk.

Ennél konkrétabb számokról egyenlőre nem beszélt a Tesla. A tízszeres javulás alapján viszont a fejlesztés 240 teraops (TOPS) körüli számítási teljesítményt nyújthat 8 bites egészszámos utasítások végrehajtásánál, amely utóbbi a mélytanulásos rendszerek teljesítményének kvázi szabványos iparági mutatója. Amennyiben a kalkuláció helytálló, úgy a házon belül fejlesztett chip az Nvidia Tesla V100 szerveres gyorsító tempójának közel dupláját produkálhatja, amely számítási teljesítmény valóban elég lehet egy akár teljesen önvezető (level 5) rendszer működtetéséhez is.

A bő két éves Drive PX2-höz képest tehát igen jelentős előrelépésről van szó, de közben az Nvidia sem ült karba tett kézzel, a Drive PX platform tavaly bejelentett verziója, a Pegasus már 320 TOPS sebességet ígér, hasonló, level 5-ös önvezető képesség mellett. A Tesla azonban az "off-the-self" megoldás helyett inkább sajátot gründolt, a lépéstől feltételezhetően versenyelőnyt remélve.

A gépi tanulásos modellek végrehajtásra szabott processzor ötlete egyébként már nem számít újnak. A Google adatközpontokhoz tervezett TPU-ja már második generációját tapossa, miközben a Fujitsu és az Intel is dolgozik saját, dedikált chipjén. Az, hogy az egyre bővülő listán a Tesla neve is szerepel, nem meglepő. Ezzel Musk és cége még inkább differenciálhatja magát, az autógyártók döntő többsége ugyanis az Nvidia vagy a MobilEye (Intel) egyenplatformjára épít. Ezzel optimális esetben előnyre tehet szert a Tesla, amelynek legfőbb célja a piac első teljesen önvezető (level 5) rendszerének piacra dobása lehet.

GPU helyett ASIC

Kissé rendhagyó módon a munkálatok kezdeti stádiumáról is szó esett az alapvetően pénzügyi vonatkozású konferenciahíváson. A projekthez több más ex-Apple mérnök (pl. Doug Field, Rich Heley) mellett az iPhone 5 processzorát tervező Pete Bannon is részt vett, akinek szavai alapján egy kifejezetten AI-hoz tervezett ASIC-ról van szó, vagyis az Nvida fejlesztésével szemben nem egy CPU-GPU hibrid mellett tette le voksát a Tesla. A lapka tervezését nulláról kezdte egy nagyjából 50 fős csapat, amelynek élére az AMD-től igazolt (és azóta már az Intelnél dolgozó) Jim Kellert állította a Elon Musk.

A tervezésnél az egyik legfontosabb szempont volt, hogy az egyes számításokat a lehető legkisebb overheaddel, bármiféle szoftveres réteg vagy emuláció nélkül, az elérhető legnagyobb hatékonysággal hajthassa végre a chip. Musk szerint ezért is vetették el a komplikáltabb CPU+GPU dizájnt, amelynél a két jelentősen eltérő architektúra közötti kommunikáció számottevően korlátozza a rendszer számítási kapacitását.