Western Digital: hozzuk az első QLC NAND-os SSD-t

Elkészült a fejlesztés első verziója, augusztusban már arra épülő SSD-t mutat a cég.

Bejelentette QLC NAND fejlesztését a Western Digital. A cellánként négy bitet tároló, 3D NAND-dal ötvözött megoldásra a BiCS3 X4 jelölést aggatta a cég, az erre épülő NAND lapkák maximális kapacitása pedig elérheti a 768 gigabitet (96 gigabyte). Utóbbi érték 50 százalékkal múlja felül a TLC elven, azaz cellánként 3 bitet tároló korábbi fejlesztés 512 gigabites kapacitását. Ezzel tovább növelhető a bitsűrűség, ami az egységnyi tárkapacitás olcsóbb előállításához vezető út első lépcsője. Az első BiCS3 X4 NAND-ra épülő SSD-t már a következő hónap elején megmutatja a WDC.

A Toshibával közösen készített fejlesztés egységnyi lapkaterületet alapul véve a TLC-hez képest harmadával növelheti a bitsűrűséget, hisz egyetlen cellában három helyett már akár négy bitet is képes tárolni a rendszer. Mindez első hallásra egyszerűnek hangozhat, ugyanakkor a gyakorlati megvalósítás komoly kihívás elé állítja a mérnököket, a megbízható működés ugyanis még pontosabb feszültségértékeket kíván meg.

A NAND flash cellák ugyanis töltésszint (pontosabban elektronok) formájában tárolják az adatokat, konfigurációtól függően egy cella egy (SLC), kettő (MLC), vagy három (TLC) bit információt hordozhat. Minden egyes újabb bittel duplázódik a tároláshoz szükséges töltésszintek száma, például a QLC esetében már 16 különféle értéket kell üzembiztosan megkülönböztetni. Ennek velejárója, hogy az egyes műveletek elvégzéséhez hosszabb időre van szükség, miközben a cellák hamarabb elhasználódhatnak, ugyanis kisebb a feszültségtartományok közötti terület, ahova a cella szilíciumdioxid rétegének "kopása" miatt még hiba nélkül ki tud "futni" a vezérlés. Ezen kívül, ha egy cella 4 bit adatot tárol, akkor a programozási műveletek is gyakoribbak lehetnek, hisz egy bit módosítása (pl.: 0000->0001) is épp ugyanazt a műveletet igényli, mintha mind a négyet átírná a vezérlés (pl.: 0101->1010).

TLC-szintű élettartam?

Jogod van tudni: mankó kirúgáshoz, munkahelyi szkanderezéshez Ezúttal egy mindenki számára kötelező, de laza jogi különkiadással jelentkezünk. Ennyi a minimum, amit munkavállalóként illik tudnod.

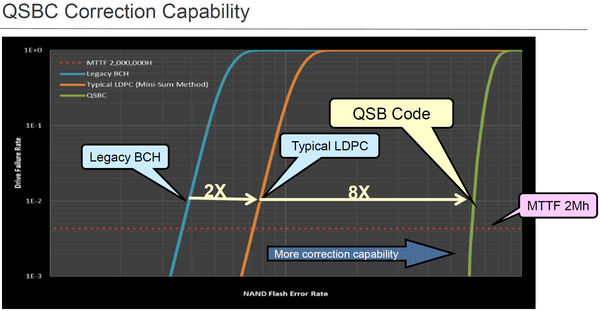

Ennek fényében a NAND gyártók komoly erőforrásokat fektetnek a különféle, a problémát kezelő eljárások kifejlesztésébe. Ez dióhéjban fejlett algoritmusokat, adaptív írási/olvasási technikát, illetve különféle DSP ECC rendszereket. A Toshiba például egy külön, QSBC (Quadruple Swing-By Codes) névre keresztelt eljárást fejlesztett, amely a cég szerint a sztenderdnek számító BCH ECC-nél tízszer, az LDPC ECC-nél pedig nyolcszor nagyobb kapacitású, azaz lényegesen több hibát képes kezelni.

Talán épp erre alapozza magabiztosságát a Western Digitallal vegyesvállalatban fejlesztő és gyártó cég, miszerint QLC NAND-ja a TLC-hez hasonló terhelés is elviselhet. Az AnandTech megkeresésére a Toshiba közölte, hogy fejlesztésével 1000 P/E, azaz programozási/törlési ciklust céloz, amely nagyjából egyezik az első TLC-s fejlesztések értékével. Ez a szakemberek által várt 100-150 ciklushoz képest lényegesen nagyobb lenne, amivel egy csapásra változhatna meg a felhasználási terület. A QLC-t ugyanis inkább a WORM-szerű (Write Once Read Many), olvasás intenzív környezetbe várták, 1000 ciklussal viszont lényegesen szélesebb körben lehetne bevetni a fejlesztést, amivel a Toshiba és a WDC előnybe kerülhetne a legnagyobb rivális Samsunggal szemben.