Ráfeküdt az SSD-s fejlesztésekre a Western Digital

Nagy léptekkel növelné tovább a NAND lapkák kapacitását a Western Digital, amihez a rétegek mellett a cellákban tárolható adatmennyiséget is feljebb srófolja a cég.

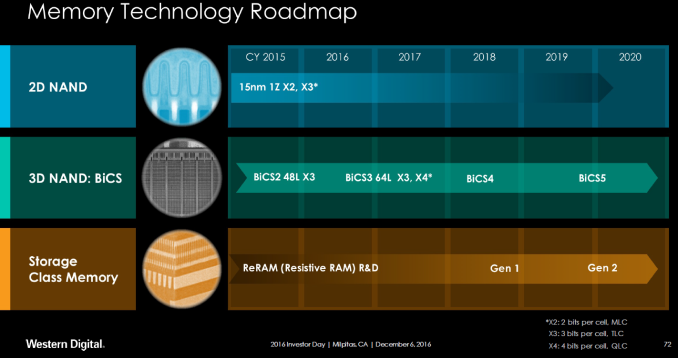

NAND-os fejlesztéseiről beszélt a Western Digital, a SanDisk felvásárlásával kompetenciát szerzett gyártó bejelentette a 96 rétegű NAND lapkáját, illetve a cellánként négy bitet tartalmazó, QLC fejlesztését. Mindkét megoldás a bitsűrűség növelését, illetve ezzel együtt adott kapacitás költséghatékonyabb előállítását célozza. A két fejlesztésnek hála komolyan megugorhat az SSD-k maximális kapacitása, az adatközpontokhoz tervezett meghajtók akár a 100 terabájtos kapacitást is elérhetik majd.

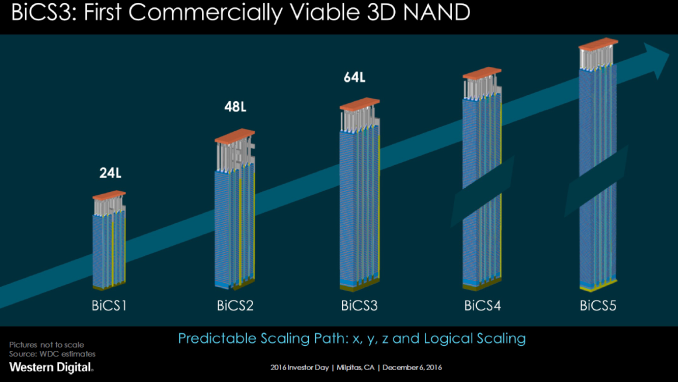

A 96 rétegű 3D NAND bejelentése várható volt, vegyesvállalatban fejlesztő WDC partnere ugyanis a közelmúltban dobta piacra az első 64 rétegű NAND-ra épülő SSD-jét. A BiCS4 fantázianévre keresztelt fejlesztés tehát 50 százalékkal növeli a rétegek, illetve ezzel együtt az egységnyi területre levetített kapacitást. A 64 rétegű BiCS3-hoz képest további előrelépés lesz, hogy az új NAND család 256 gigabittől 1 terabitig kínál majd kapacitást TLC, illetve QLC cellákkal. Ezekből természetesen több, jellemzően nyolc pakolható egyetlen NAND chipbe, ily módon a legnagyobb kapacitású lapkával akár 1 terabájtos chipeket is piacra dobhat majd a cég.

A cellánként 4 bitet tároló NAND-ról tavaly beszélt először a Western Digital partnere. A fejlesztéssel egységnyi lapkaterületet alapul véve harmadával növelhető a TLC-hez viszonyítva, ugyanakkor ezzel tovább csökkenhet a cellák élettartama. A NAND-ok ugyanis bizonyos töltésszint formájában tárolják az adatokat, a konfigurációtól függően egy cella egy (SLC), kettő (MLC), vagy három (TLC) bit információt hordozhat. Minden egyes újabb bittel duplázódik a tároláshoz szükséges töltésszintek száma, például a QLC esetében már 16 különféle értéket kell üzembiztosan megkülönböztetni.

Mindez még pontosabb feszültségértékeket kíván meg, aminek velejárója, hogy az egyes műveletek elvégzéséhez hosszabb időre van szükség, miközben a cellák hamarabb elhasználódhatnak, ugyanis kisebb a feszültségtartományok közötti terület, ahova a cella szilíciumdioxid rétegének "kopása" miatt még hiba nélkül ki tud "futni" a vezérlés. Ezen kívül, ha egy cella 4 bit adatot tárol, akkor a programozási műveletek is gyakoribbak, hisz egy bit módosítása (pl.: 0000->0001) is épp ugyanazt a műveletet igényli, mintha mindhármat átírná a vezérlés (pl.: 0101->1010). A cellák programozhatósága ezzel tovább romlik, ugyanakkor bizonyos megoldásokkal kompenzálni lehet a negatív tendenciát, amihez a gyártók elsősorban fejlett algoritmusokat, adaptív írási/olvasási technikát, illetve DSP ECC rendszert alkalmaznak.

Tavaszi mix a 2025-ös IT pangástól az interjúk evolúciójáig Ezúttal öt IT karrierrel kapcsolatos, érdekes és aktuális témát érintettünk.

Ezért várhatóan az első QLC NAND-os meghajtókat majd inkább WORM-szerű (Write Once Read Many), olvasás intenzív környezetben alkalmazzák majd. Egyelőre sem a Toshiba, sem pedig a Western Digital nem közölte, hogy QLC fejlesztés mekkora terhelhetőséget nyújt majd, de iparági szakemberek szerint az első lapkák legfeljebb 100-150 programozási ciklust viselnek majd el, ami a TLC 1000 ciklusának töredéke. A technológia fejlődésével ugyanakkor idővel nőhet az érték, ami utat nyithat a szélesebb körű felhasználás felé.

Arról egyelőre nincs pontos információ, hogy az első piacképes QLC megoldás bevetését mikorra tervezi a Western Digital, a 96 rétegű NAND viszont már jövőre megjelenhet, tehát várhatóan legkésőbb 2019-ben már a négybites cellákat tartalmazó chip, illetve az arra épülő első SSD-k is piacra kerülhetnek.