Háromféle gyártástechnológiát keverne az Intel

A heterogén chipdizájnban szinte csak a végrehajtóegységek készülnének a legfejlettebb node-on, így gyorsítva az újabb gyártástechnológiák adaptációját.

Részletezte jövőbeni, heterogén processzorfelépítését az Intel. Az új irány a komponensektől függően más-más gyártástechnológiát alkalmazna, az így elkészült különálló lapkákat pedig a processzor nyomtatott áramkörében "drótozná" össze a gyártó. A megközelítéssel jelentősen csökkenthetőek az előállítási költségek, nem utolsó sorban pedig felgyorsítható az egyes újabb gyártástechnológiák bevetése, nem kell megvárni, hogy kihozatal elérje a nagyobb lapkák gazdaságos előállításához szükséges szintet.

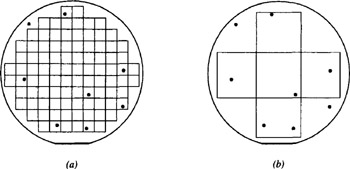

Ugyanaz a hibaarány kis chipeknél kevésbé problémás

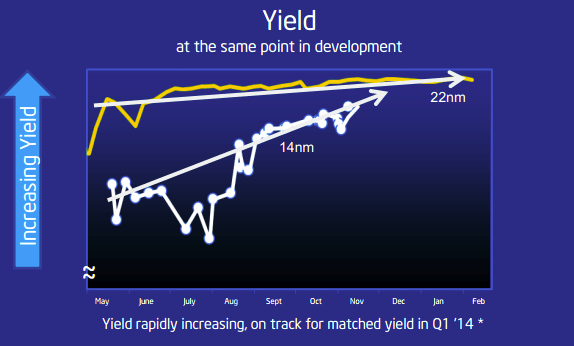

Az új stratégiának egyik legfontosabb hozadéka lenne, hogy a jövőben megjelenő újabb csíkszélességeket mobil és asztali processzorok előállítása helyett először a leginkább jövedelmező szerverprocesszoroknál veti majd be az Intel. A cég eddig a sokmagos, hatalmas méretű Xeonokat hagyományosan az utolsók között migrálta a legújabb eljárásokra, mivel a kiforratlan, éretlen, kihozatali problémákkal küzdő gyártástechnológiákkal ezek előállítása nem gazdaságos. Emiatt hagyományosan a legkisebb méretű chipek gyártása indult meg először, amelyeknél még a waferenkénti néhány hiba is elviselhető selejtarányt jelent, majd egy-másfél év múlva, a gyártósorok finomhangolásával, a gyerekbetegségek elhárításával indult a nagyobb lapkák termelése.

Jogod van tudni: mankó kirúgáshoz, munkahelyi szkanderezéshez Ezúttal egy mindenki számára kötelező, de laza jogi különkiadással jelentkezünk. Ennyi a minimum, amit munkavállalóként illik tudnod.

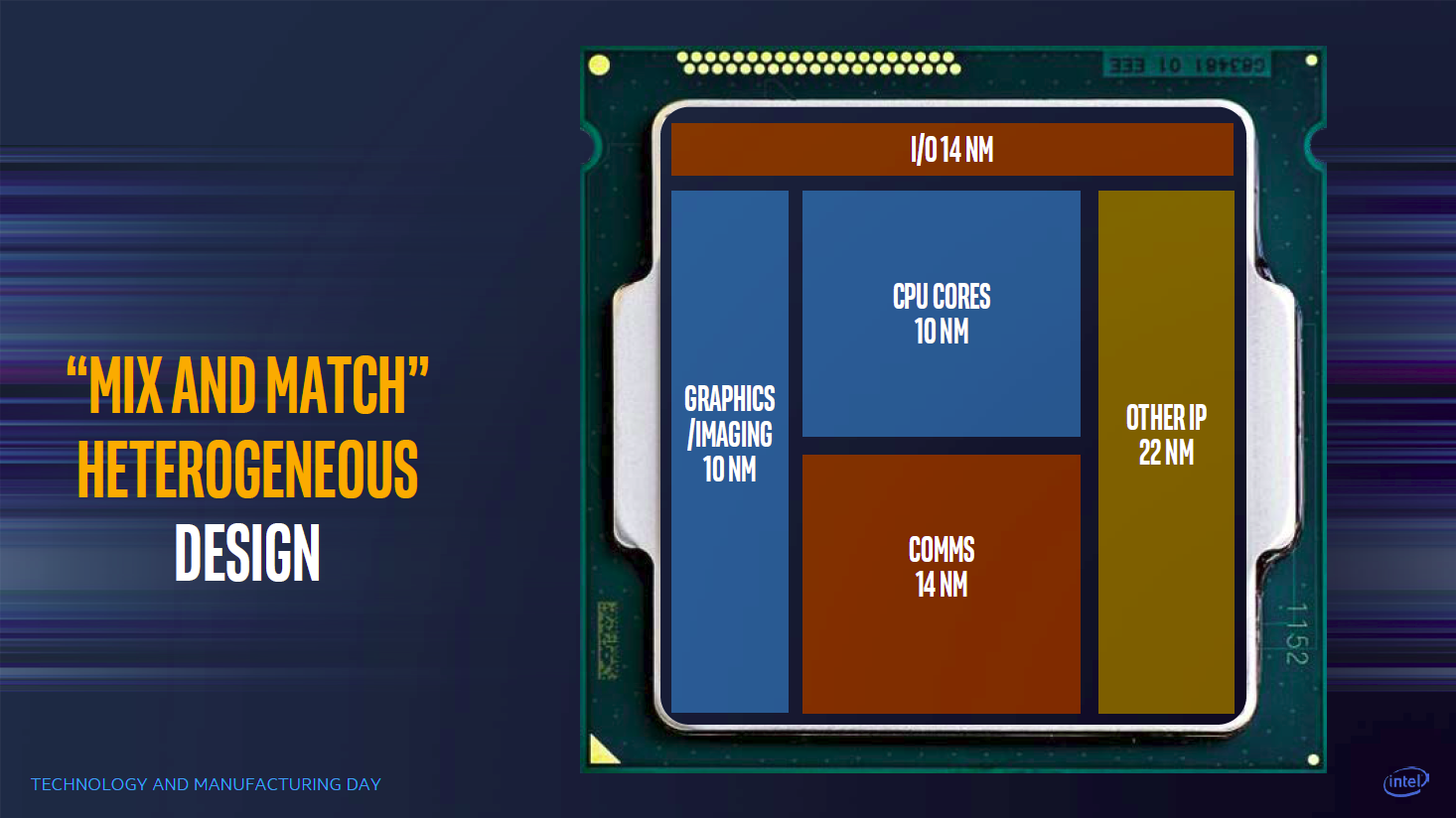

Az Intel új, heterogén megközelítésével már csak a kritikus, a gyártástechnológiára érzékeny, tehát abból leginkább profitálni képes részeket, például a CPU magokat és a GPU-t gyártaná a mindenkori legfejlettebb, kevésbé kiforrott, nem utolsó sorban pedig legdrágább technológián. A csíkszélesség szempontjából kevésbé fontos részegységeket (pl. I/O vezérlő) korábbi megoldásokon, például 14, vagy akár 22 nanométeren készülnének, majd azokat saját, EMIB technológiájával drótozná össze a processzor tokozásában az Intel. A megközelítésnek egyetlen hátránya a hosszabb vezetékek miatti megnövekedett késleltetés lehet, így valószínűleg csak az ebből a szempontból kevésbé kritikus egységek kerülnek ki a processzormagok mellől.

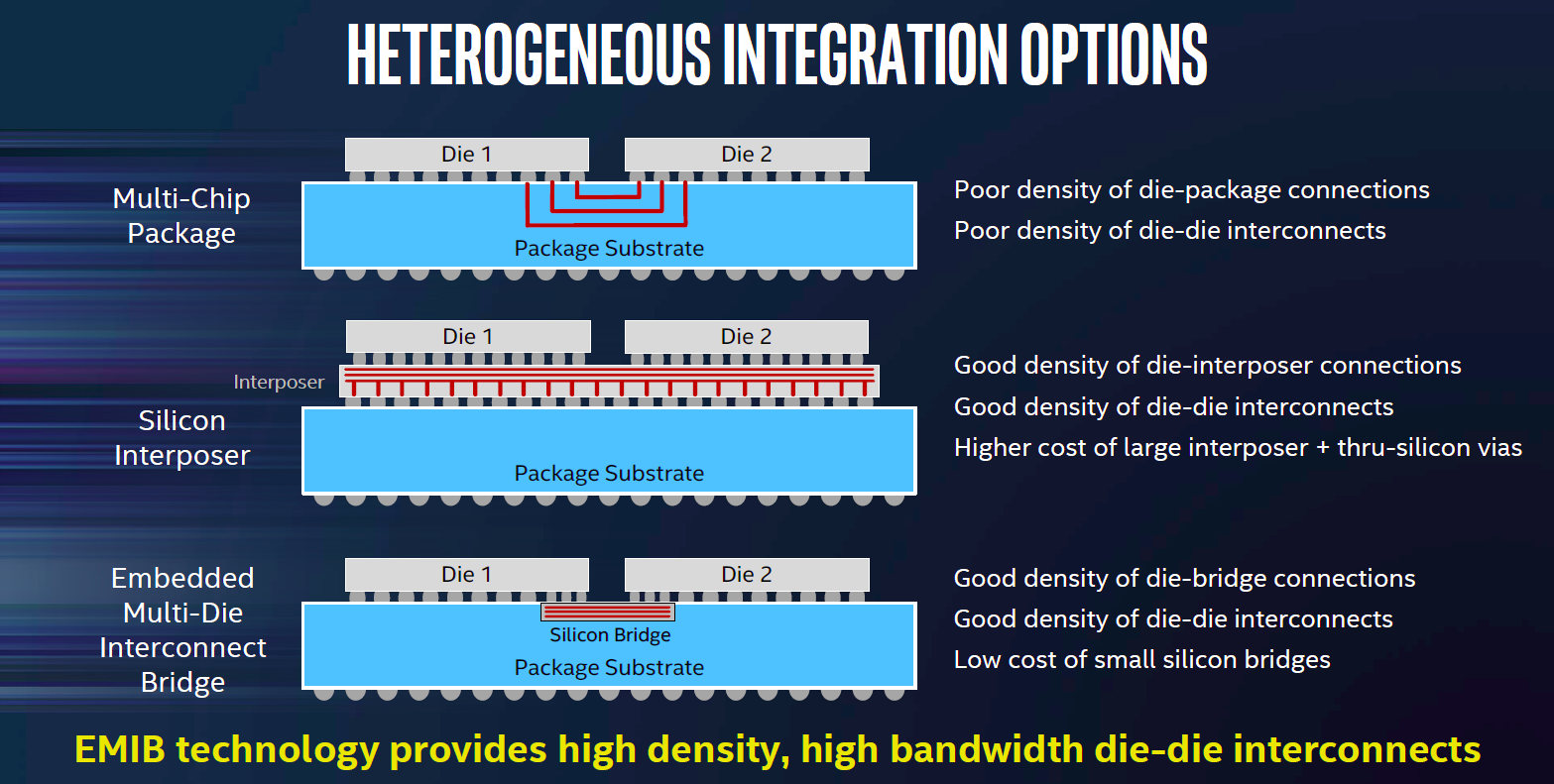

A koncepció megvalósításában nagy segítséget nyújt a már említett EMIB (Embedded Multi-die Interconnect Bridge). A vállalat szerint ez egyszerűbben és olcsóbban oldja meg az egyes lapkák közötti összeköttetést, ugyanis míg a klasszikus 2.5D felépítés esetében az interpózer szerepét betöltő szilíciumlapka területének olykor akár nagyobbnak is kell lennie az azon elhelyezkedő lapkákénál, addig az EMIB több apró, az áramkörbe beágyazott szilícium szeletekre (hídra) épít, ami jelentősen csökkenti a gyártási költségeket. Az Intel szerint nem csak azért, mert így elhagyható a nagy méretű és drága, a huzalozásnak helyet adó lapka, hanem mert ennek hiányában a gyártás is egyszerűbb, például nem kell átvezetéseket (TSV) létrehozni az interpózerben, a kevésbé komplex eljárásnak köszönhetően pedig csökken a selejtarány. További előny, hogy az EMIB-bel csökkenthető az összeköttetésekhez szükséges vezetékek hossza, minek hála végső soron növelhető a kapcsolat sebessége.

Az Intel arról egyelőre nem beszélt, hogy konkrétan milyen termékeknél alkalmazza majd először az új megközelítést, de amennyiben az elsődleges cél a szerver processzorok gyorsabb átállítása, úgy akár már jövő év első felében megjelenhet az első heterogén megoldás. A korábban pletykált Intel CPU és AMD Radeon GPU öszvér is ezzel az eljárással születhet meg, hisz az EMIB-bel jóformán bármilyen IP-ket össze lehet kapcsolni, amennyiben azok megfelelő busszal (pl. PCI Express) rendelkeznek.