Nem adja fel a szervereket az ARM

Kigyúrta új cache-koherens belső buszrendszerét és memóriavezérlőjét az ARM. A fejlesztéseket kifejezetten a szerveres chipekhez tervezte a cég, ugyanakkor még így sem biztos, hogy sikeresek lesznek a megoldások.

Két új IP-vel, azaz szilíciumon implementált áramköri egységgel rukkolt elő az ARM. A fejlesztések egy interkonnektet és egy memóriavezérlőt takarnak, melyeket szerveres lapkákhoz szán a tervezőcég. Kérdéses, hogy ezek valaha felbukkannak-e végleges termékek formájában, hisz a gyártók ARM-os próbálkozásai eddig rendre kudarcba fulladtak, és nem biztos, hogy az új fejlesztések ezen tudnak változtatni.

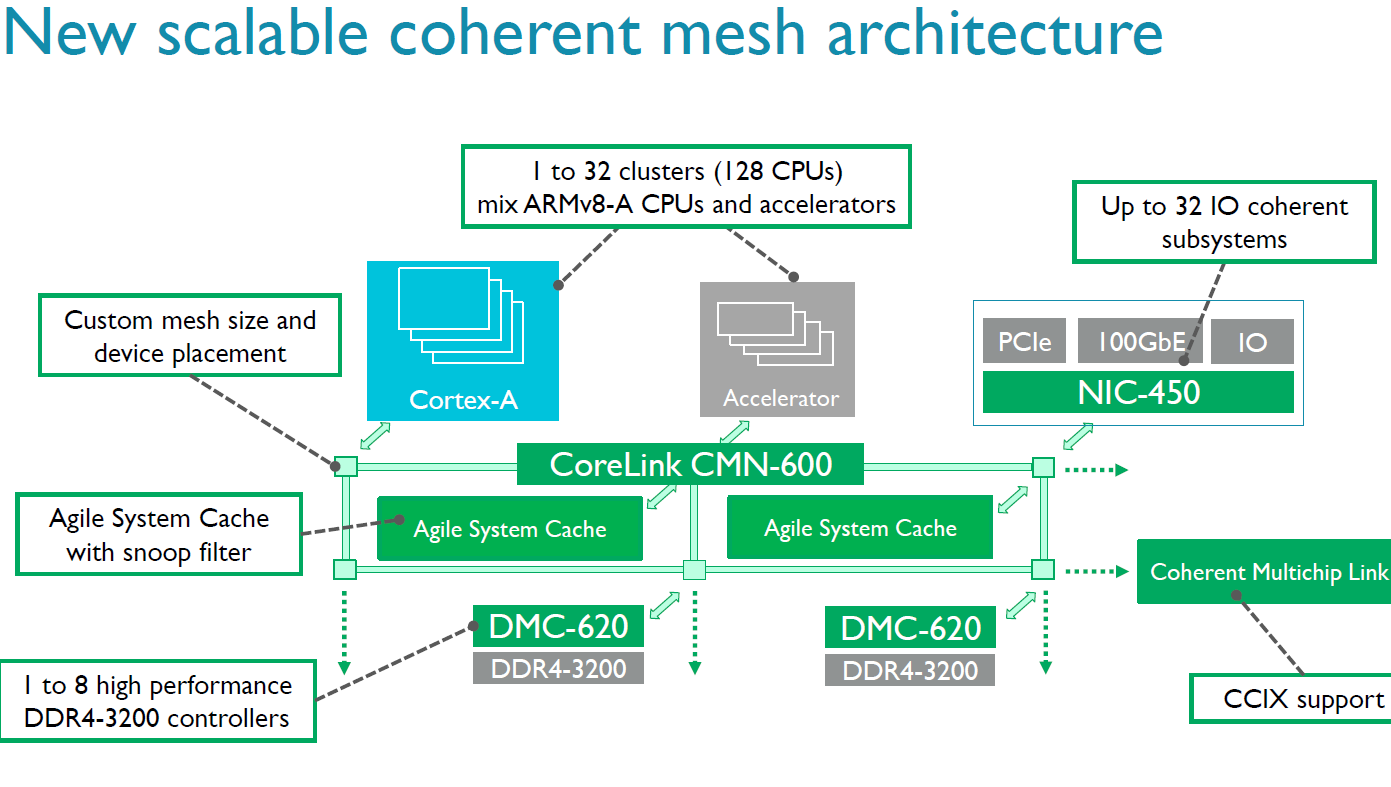

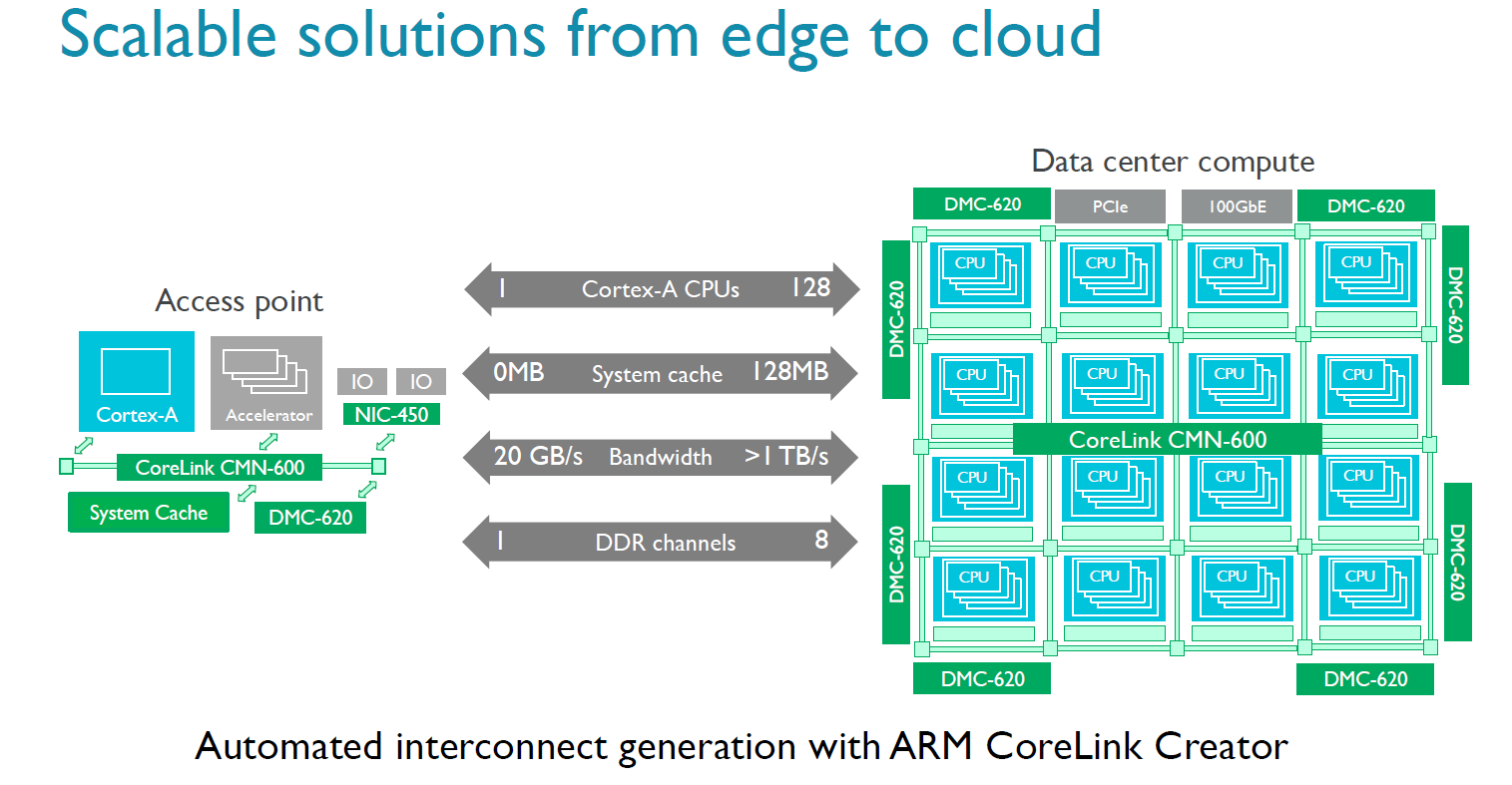

Az egyik új IP a CMN-600 jelölésű koherens interkonnekt, mely a korábbi CCN-500 leváltására született. Az egyik nagy előrelépést a támogatott klaszterek, illetve magok száma jelenti, hisz míg az előd csak 12 négymagos klasztert támogatott (48 mag), addig a CMN-600 már 32 darab négymagos klasztert is képes kezelni, ami egyetlen lapkában legfeljebb 128 magot jelenthet.

Természetesen nem csak CPU magokat képes összekötni az interkonnekt, különféle gyorsítók (pl. GPU), vagy akár hálózati vezérlők is összekapcsolhatóak vele, illetve a multichip megoldás, tehát a többprocesszoros konfiguráció is támogatott. Emellett egy extrának tekinthető az Agile System Cache gyorsítótár, melyen keresztül különféle I/O eszközök tudnak maguknak területet allokálni a harmadszintű gyorsítótárban a magok érintése nélkül, ami csökkenti a késleltetést.

Ahogy a nevében is szerepel, a CMN-600 koherens, így a rendszerben összekötött egyes feldolgozók (pl. CPU-k, GPU-k) elérhetik és monitorozhatják egymás memóriáinak (cache) tartalmát. Amennyiben az egyik feldolgozó olyan adatot módosít, ami egy másiknál gyorsítótárazva van, akkor az inkonzisztencia elkerülése miatt érvényteleníti az utóbbit.

Tavaszi mix a 2025-ös IT pangástól az interjúk evolúciójáig Ezúttal öt IT karrierrel kapcsolatos, érdekes és aktuális témát érintettünk.

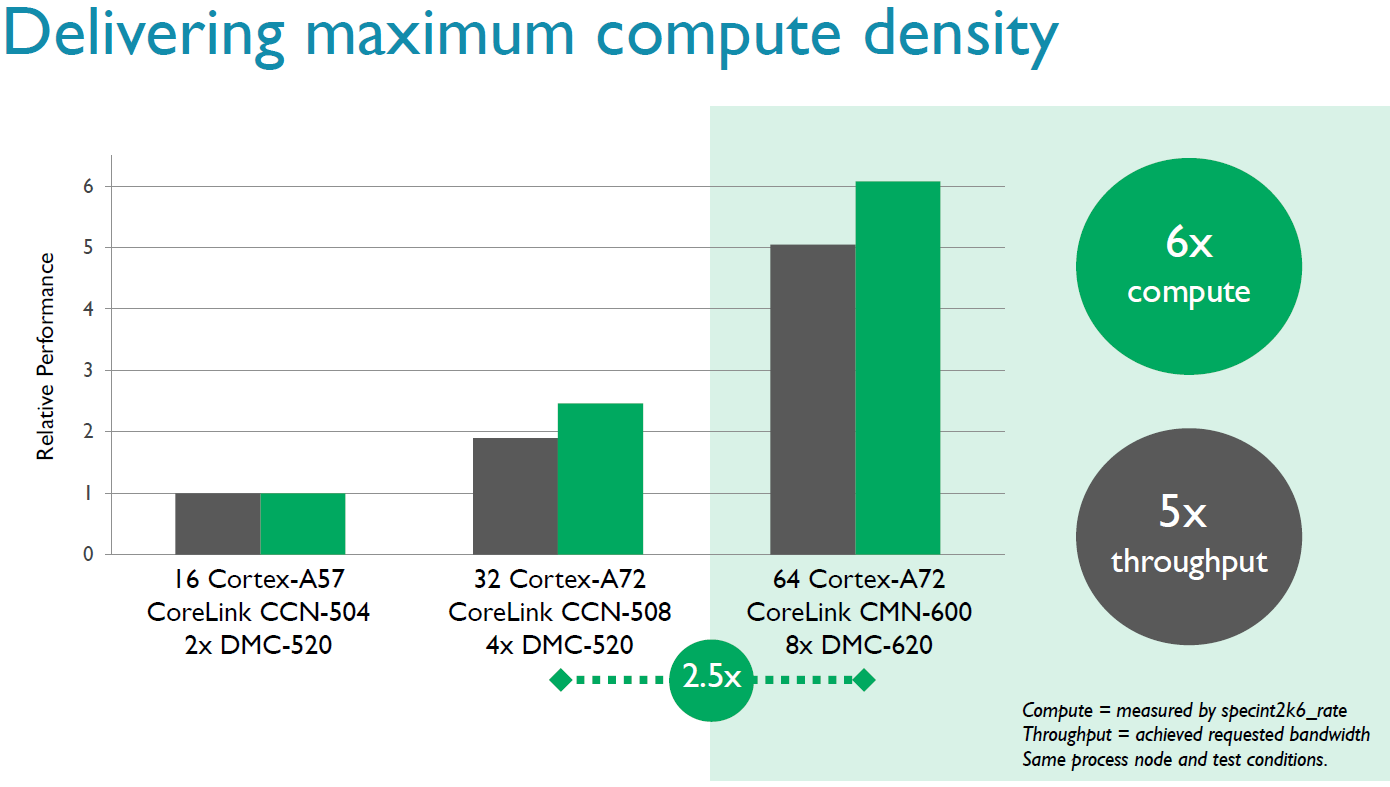

Ugyancsak az interkonnekthez kapcsolódik a másik újdonság, a DMC-620 jelzésű memóriavezérlő. Ez az előd DMC-520-at minden szempontból túlszárnyalja, a csatornák maximális számát négyről nyolcra növeli úgy, hogy közben mindegyik képes 1 terabájt memória kezelésére, tehát a processzoronkénti csúcskapacitás akár 8 terabájt is lehet. Mindezt már DDR4-es modulokból lehet összerakni, melyek DDR4-3200 szabványúak is lehetnek.

Ez alapvetően négyszeres gyorsulást jelentene a DDR3-1600-as modulokat támogató négycsatornás DMC-520-hoz képest, de az ARM mérése szerint akár ötszörös is lehet az előrelépés, ugyanis a memóriavezérlő a hatékonyságon is javít. A tervezőcég SPEC int2006_rate alapján az A72-es magok számának duplázásával (32->64) kettő és félszeresére nőtt az eredmény, négyszer több maggal pedig már hatszor kedvezőbb eredmény született.

Bár a CMN-600 és a DMC-620 papíron jól hangzik, nagy kérdés, hogy melyik gyártó fogja élesben is bevetni a fejlesztéseket. Az adatközpontokban eddig nem sok babér termett az ARM-alapú megoldásoknak, és jelen állás szerint nem utal semmilyen jel arra, hogy ez a közeljövőben megváltozna. Ennek kizárásával már csak a HPC lehet az egyik potenciális terület, a Fujitsu például ARM processzorokra építi az évtizedfordulón esedékes szuperszámítógépét, ugyanakkor a japán cég korábban azt nyilatkozta, hogy ehhez a K Computerben is alkalmazott Tofu (Torus fusion) interkonnekt viszik tovább, ami nem jó ómen az ARM fejlesztése számára.