Az Azure-t is elérte az FPGA-láz

A hálózati forgalom hatékony kezelésére veti be az újrahuzalozható chipeket a Microsoft. Hamarosan a teljes rolloutra sor kerülhet.

Tovább bővítheti az FPGA-k szerepét adatközpontjaiban a Microsoft. A Bing keresőnél tapasztalt, az előzetes várakozásokat felülmúló sikerek után az Azure is profitálhat a programozható logikai kapumátrixok egyedülálló képességeiből, a felhős adatközpontokban a hálózati forgalom gyorsításáért, optimalizálásáért felelhetnek majd a chipek, a kísérleti fázis eddig az elvárásoknak megfelelően alakult.

A Microsoft megfigyelte, hogy a fizikai és a virtuális hálózati adapterek közti adatforgalom lebonyolítása és szabályozása (load-balancing, traffic routing, stb.), illetve az azt végző hypervisor több gigabites sávszélesség mellett számottevő CPU időt, bizonyos esetekben már komplett magokat emésztett fel. Ezzel a virtuális gépeknek jutó erőforrások csökkentek, ergo a rendszer kevesebb VM-et tudott futtatni, a teljes kapacitás kisebb lett, mely probléma kezeléséhez végül egy egyedi megoldást dolgozott ki a cég, ahol kapóra jött a Bing-FPGA házasításánál megszerzett tapasztalat.

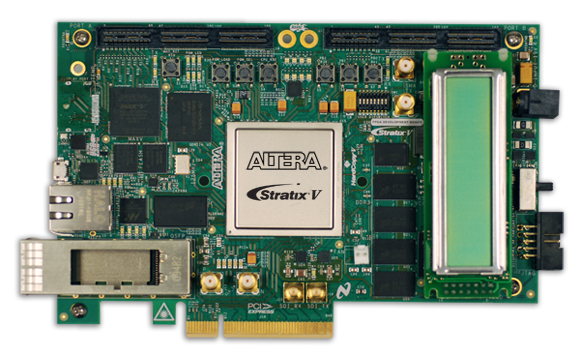

A probléma kezeléséhez elsőként némileg át kellett szabni a Bingnél alkalmazott FPGA-kat, hisz a keresőalgoritmusok gyorsításához nem kellett hálózati adatforgalmat "átfolyatni" a gyorsítókon. A Microsoft egységes hardverben gondolkozott, mely Bing és Azure igényeihez egyaránt megfelel, így az átszabott kártyák dedikált csatlakozást kaptak, mellyel beilleszthetőek az Azure hálózati architektúrájába is, ezzel pedig a FPGA-kon átvezethető a hálózati adatforgalom úgy, hogy a gazdarendszer, illetve ezzel a CPU kihagyható a folyamatból.

A gyakorlatban ehhez a PCI Express interfészt használják a virtuális gépek, melyen keresztül közvetlenül kommunikálhatnak, illetve bonyolíthatnak hálózati adatforgalmat a buszon ülő FPGA-kkal. A Microsoft szerint ezzel egyetlen VM akár másodpercenkénti 25 gigabites sebességet is megkaphat, 100 mikroszekundumos (0,1 milliszekundum) késleltetés mellett. Utóbbi tízszer kedvezőbb a korábban CPU-kkal elért értékhez képest.

USA Tech Hub: ahonnan a passzátszél fúj Minden, ami a technológiai szektorban történik, jellemzően az USA-ból indul.

Bár a direkt hozzáférés és a teljesítmény megfelelő ASIC-kal (hálózati adapter) is kivitelezhető lenne, ezek a megoldások rendszerint különféle limitációkkal rendelkeznek, például egy adaptert legfeljebb 4 VM-hez lehet hozzárendelni. Ennél az FPGA-k lényegesen nagyobb rugalmasságot biztosítanak, az üzemeltetők később a különféle vezérlési folyamatokat (pl. terheléselosztás) is könnyen újraprogramozhatják, mindezt pedig akár használat közben, a hardver cseréje nélkül.

A Microsoft egyelőre csak amolyan kísérleti, bemutató jelleggel beszélt a FPGA-k hálózatos szerepéről, de ahogy a Bingnél, úgy az Azure esetében is az éles bevetés a cél, a vállalat idővel szeretné a teljes felhős adatközpontjára kiterjeszteni a technológiát. Emellett a Microsoft nem csak a hálózati forgalom optimalizálását bízná FPGA-kra, a cég elképzelése szerint más algoritmusokat is gyorsítana kapumátrixokkal. Erre a mintázatfelismerés mellett a gépi tanulás lehet egy jó példa, hosszabb távon pedig az ügyfelek számára egyedileg programozott FPGA-k lehetősége sincs kizárva.

Hogy bizonyos feladatokra mennyire hatékonyan használható az FPGA, arra a Microsoft héten zajló üzemeltetői rendezvényének egyik demonstrációja lehet jó példa. A bemutató keretein belül az angol nyelvű Wikipedia 3 milliárd szavát fordították le egy tizedmásodperc alatt mindössze 1000 darab FPGA segítségével.