Úton az Intel-Altera első közös fejlesztése

Sínen van az első Intel-Altera fejlesztés, az EMIB tokozási technológiának hála, versenytársainál olcsóbb implementálhatja a rétegzett HBM memóriákat az Altera.

Legújabb FPGA-jának részleteiről beszélt az Altera. A Stratix 10 MX legnagyobb húzása a rétegezett memória bevezetése lesz, melynek hála másodpercenkénti 1 terabájtra nő a maximális sávszélesség. A kivitelezéshez az Intel EMIB technológiájára választotta az Altera, melyhez a tavalyi felvásárlás után már kvázi ingyen juthat hozzá cég.

A Stratix 10 MX család tagjai SiP-k (System-in-Package) lesznek, tehát a rendszer alapvető komponensei egy közös tokozáson kapnak helyet. A központi lapka legfeljebb 2 005 000 LE-t (Logic Element) és 679 680 ALM-et (Adaptive Logic Modules) vonultathat fel, melyek maximális órajele 1 GHz lehet. Ezekkel közös lapkába került négy darab, 1,5 GHz-es ARM Cortex-A53 mag.

Mindez önmagában nem jelentene előrelépést az előd, Stratix 10 sorozat egyes tagjaihoz képest, a központi lapkához viszont már rétegzett HBM2 memóriákat társítottak a tervezők. A fejenként 256 GB/s sávszélességre képes, 4 gigabájtos lapkákból négy darab került a Core Fabric mellé, amivel a sávszélesség elérheti az 1 TB/s-ot.

Az Altera szerint ez nagyjából tízszer több mint amit DDR4-es chipekkel elért, ráadásul a fogyasztás is alacsonyabb, azonos sávszélességet feltételezve körülbelül 26 százalék a HBM2 előnye. További pozitívum, hogy a tokozásra helyezett memóriáknak köszönhetően csökken a NYÁK komplexitása, a rendszer kisebb helyet foglal mintha a chipek az FPGA-n kívül kapnának helyet.

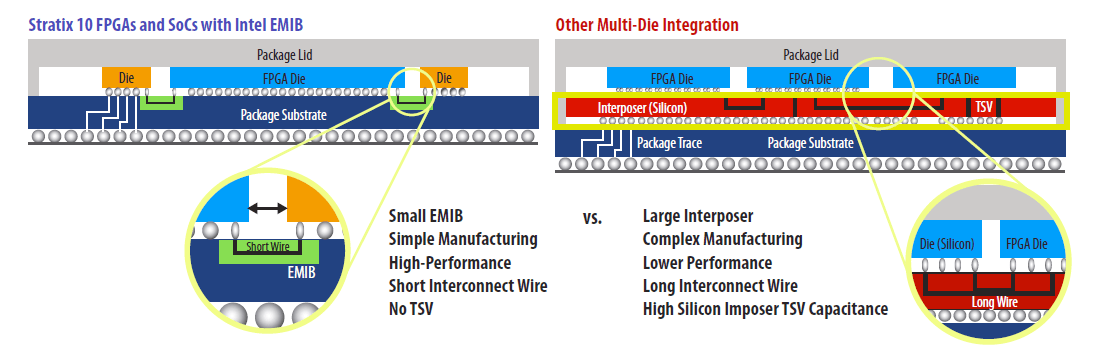

A megoldás hátulütője, hogy bonyolultabb tokozást kíván, ugyanakkor az Intelnek hála az Alterának könnyebb dolga lehet mint például az ugyancsak HBM memóriákat implementáló AMD-nek vagy Nvidiának. Míg utóbbi két cég jobb híján kénytelen interpózert, azaz egy extra, nagy méretű szilíciumlapkát alkalmazni a központi lapka és a memóriák közötti átvezetések kiépítéséhez, addig az Alterának egy kedvezőbb alternatíva miatt erre nincs szüksége.

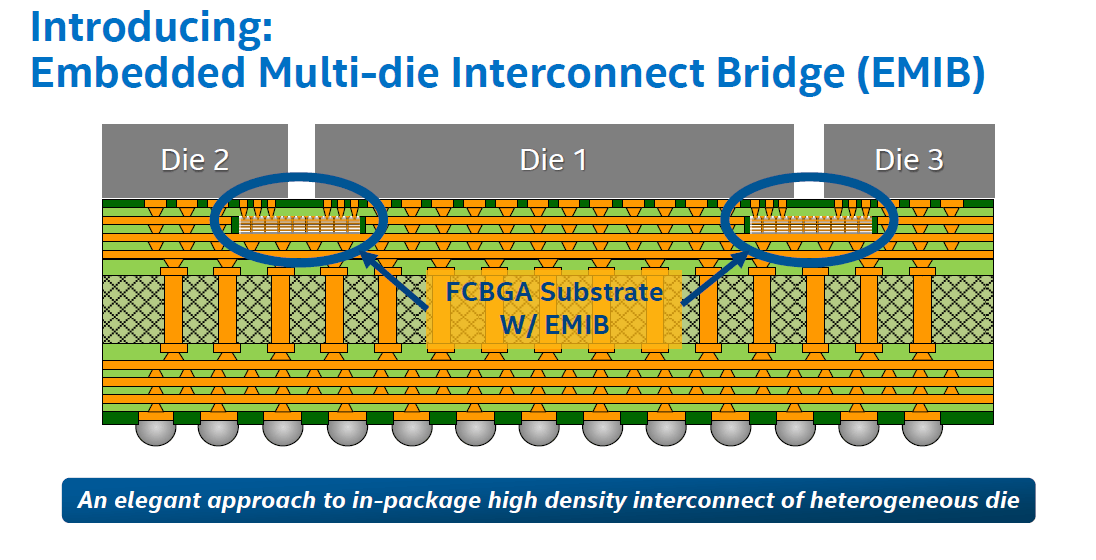

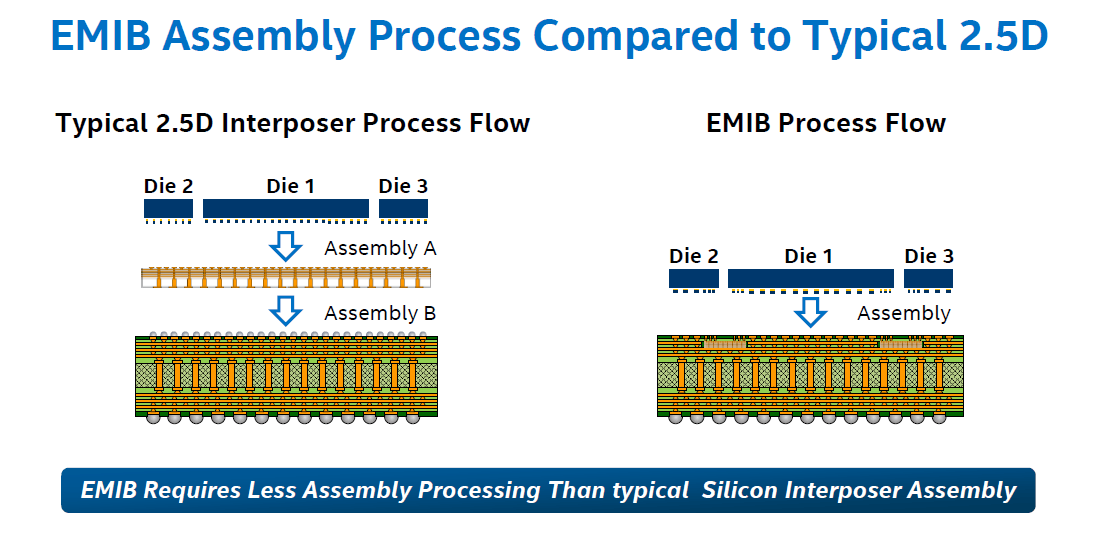

A megoldást az Intel EMIB (Embedded Multi-die Interconnect Bridge) technológiája jelenti, mely egyszerűbben és olcsóbban oldja meg az egyes lapkák közötti összeköttetést. A klasszikus 2.5D felépítés esetében az interpózer szerepét betöltő szilíciumlapkának nagyobbnak kell lennie az azon elhelyezkedő lapkáknál. A EMIB esetében erre nincs szükség, az összeköttetést több, kis méretű, a tokozásba épített híd biztosítja, ami már önmagában jelentősen csökkenti a gyártási költségeket.

Az Intel szerint nem csak azért, mert elhagyható a nagy méretű, drága interpózer, hanem mert ennek hiányában a gyártás is egyszerűbb, a kevésbé komplex eljárásnak köszönhetően például csökken a selejtarány. További előny, hogy az EMIB-bel csökkenthető a vezetékek hossza, ami alacsonyabb ellenállást eredményez, minek hála tovább növelhető az órajel.

Jogod van tudni: mankó kirúgáshoz, munkahelyi szkanderezéshez Ezúttal egy mindenki számára kötelező, de laza jogi különkiadással jelentkezünk. Ennyi a minimum, amit munkavállalóként illik tudnod.

Az Altera szerint jelenleg a HBM memóriák implementálása EMIB-bel oldható meg a legegyszerűbben, ugyanakkor a technológia nem csak erre jó, segítségével más lapkákat is össze lehet kötni, a szóban forgó Stratix 10 MX-en található XCVR (transceiver) chipek is hasonló módon kapcsolódnak a központi lapkához.

Jordan Inkeles, az Altera FPGA-s termékmarketing igazgatója elmondta, hogy az új termékek nagyot léphetnek előre a HBM memóriáknak hála. Az 1 TB/s-os sávszélességből az adatközpontok mellett a telkók és az internetszolgáltatók is sokat profitálhatnak majd, utóbbiaknál például a traffic routing jellemzően rendkívül sávszélesség igényes folyamat, amelyet sokszor FPGA-alapokon oldanak meg.

A Stratix 10 MX FPGA-család megjelenésére jövő év közepén lehet számítani.