Intel: ez váltja a tikk-takk stratégiát

Leleplezte új termékfejlesztési stratégiáját az Intel. A "Process-Architecture-Optimization" (PAO) három állomása meghosszabbítja a gyártástechnológiák életútját. Több profitot és lassabb fejlődést hoz az új megközelítés.

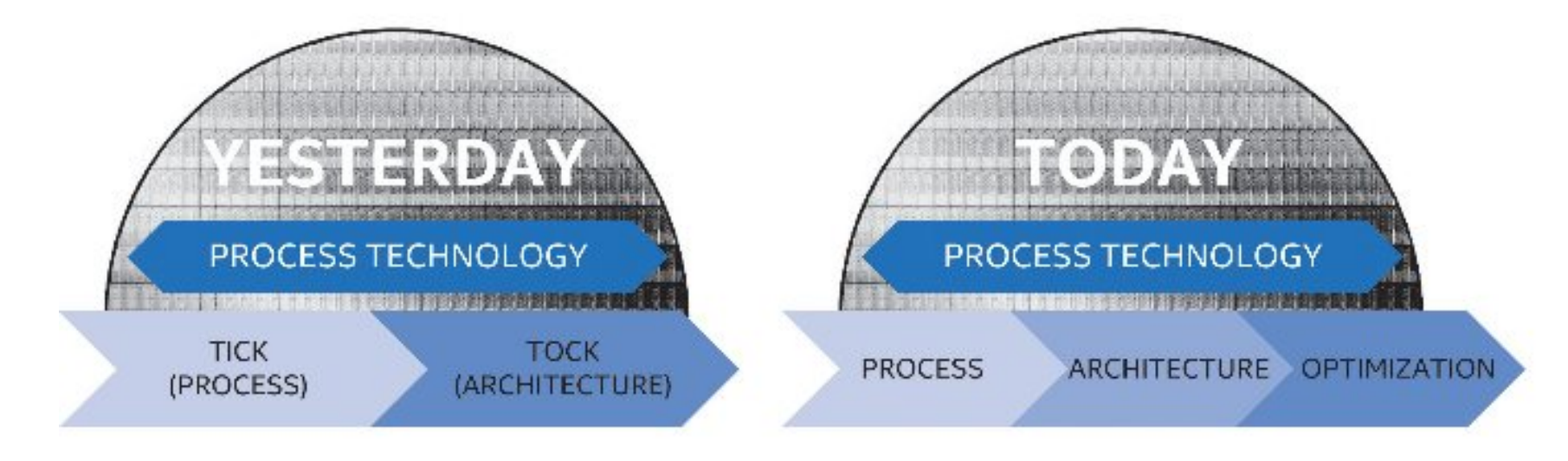

Immár teljesen hivatalos: az Intel felhagy a 2006 óta követett tikk-takk stratégiával, melynek helyét egy új, három lépcsős fejlesztés, a "Process-Architecture-Optimization" (rövidítve PAO) veszi át. Mindez röviden annyit jelent, hogy a jövőben egyetlen gyártástechnológián három generációt készít majd a cég, körülbelül 50 százalékkal meghosszabbítva az újabb csíkszélességek életciklusát.

Tikk-takk helyett PAO

Az új stratégiára az Intel éves jelentéséből derült fény, melyben a vállalat megmagyarázza az új irányt, mely a tikk-takk kibővítésének tekinthető. Utóbbival a gyártó két lépcsőben innovált: előbb a meglévő mikroarchitektúrát költöztette kisebb csíkszélességre, majd a következő generációnál a gyártástechnológiát megtartva új mikroarchitektúrát fejlesztett. A megközelítés előnye volt, hogy a cég egyszerre csak egy lovat cserélt a szekér előtt, a chipgyártás két nagy kockázatát, a mikroarchitektúra és a csíkszélesség cseréjét időben szétválasztotta a cég.

Legalábbis elméletben. A gyakorlatban azért a csíkszélesség-váltással bevezetett új processzorok is kaptak némi mikroarchitektúra-optimalizálást, a processzormagokat kisebb, míg a grafikus egységeket jellemzően nagyobb mértékben fejlesztette. Azt egyelőre nem tudni, hogy ez a jövőben megmarad-e, vagy a három lépcsősre nyúlt stratégia első állomása mostantól kizárólag egyszerű die shrink lesz, azaz csupán a korábbi megoldást fogják legyártani kisebb csíkszélességgel, szinte bármilyen módosítás nélkül.

A PAO második lépcsője a korábbi "takk" megfelelője lesz, ahol az előzőleg bevetett gyártástechnológián egy jelentősen módosított mikroarchitektúrát gyártanak majd le. Nagy kérdés, hogy az Intel milyen fejlesztéseket tervez, ugyanis a legutóbbi "takk" keretein belül született Skylake csupán kismértékben fejlődött az előd Broadwellhez (vagy Haswellhez) mérten, ami a csalódást keltő teljesítményeredményekben is tükröződik.

Az utolsó lépcsőt az új logikában az optimalizálás jelenti, ahol a korábban bemutatott gyártástechnológiát és mikroarchitektúrát tökéletesítik tovább, de a részletekről még itt is csak találgatni lehet. Magasabb órajel és/vagy alacsonyabb fogyasztás borítékolható, de akár még kisebb mikroarchitektúrális fejlesztések is beleférhetnek. Ezt az állomást a konkurens AMD már jól ismeri, alternatíva híján a vállalat évekig volt kénytelen egyazon csíkszélességet és mikroarchitektúrát alkalmazni, így maradt az optimalizálás mint fejlesztési lehetőség (pl. Richland, Godaveri).

Az új stratégia érvényes lesz a jövőre érkező 10 nanométeres Cannonlake-re is, ami az Intel ígérete szerint valamikor a jövő év második felére várható. Ezt egy évvel később az Icelake követi, az utolsó lépcső optimalizációját pedig a Tigerlake viszi véghez, valamikor 2019-ben. Mindez egyben azt is jelenti, hogy 2020 előtt már biztosan nem láthatunk 7 nanométeres Intel processzort a piacon.

Több profit, lassabb fejlődés

A tikk-takk még a Broadwell gyártási problémáinál kezdett akadozni, emiatt pedig az Intel ütemterv módosításra kényszerült. A modernebb gyártástechnológiák fejlesztésének és a kapacitás kiépítésének költségei ugyanis rendkívül gyorsan emelkednek - sokkal gyorsabban, mint legyártott lapkák iránti kereslet.

Ennek eredője, hogy a gyártó választási lehetőség elé kerül: vagy árat emel és így a magasabb fajlagos költséget a vásárlókkal fizetteti meg, vagy tovább tartja működésben a felépített kapacitást, tehát hosszabb időt hagy a befektetés megtérülésére. Mivel az Intel nem foglalkozik nagy volumenű bérgyártással (tehát a versenytársak számára nem készít lapkákat), a cég végül az áremelést és a megnyújtott technológiai ciklusokat is bevetette. A drágításban persze szerepet játszik, hogy a cég előbb a szerveres, majd a PC-s piacon is kvázi egyeduralkodóvá vált, valódi versenytárs nélkül pedig könnyedén emelhetett az árakon.

Jogod van tudni: mankó kirúgáshoz, munkahelyi szkanderezéshez Ezúttal egy mindenki számára kötelező, de laza jogi különkiadással jelentkezünk. Ennyi a minimum, amit munkavállalóként illik tudnod.

A gyártástechnológiák hosszabb életútjának hátulütői is lehetnek, ezzel akár még az Intel vezető gyártástechnológiai címe is veszélybe kerülhet. A Samsung és a TSMC egyaránt jövőre ígéri saját 10 nanométeres eljárását, amit a tervek szerint nagyjából két évvel később, 2019-ben követhet a 7 nanométer. Ennek fényében nem csoda, hogy az Intel már nem kommunikálja a gyártástechnológiai úttörő címet, a cégnek mára egyértelműen fontosabbak a gazdasági szempontok.

Az Intel szerint a PAO előnye, hogy az adott mikroarchitektúrára a korábbi egy helyett már legalább két évig számíthatnak a vásárlók, miközben a foglalatok élettartama is nőhet. A vállalat két évente előszeretettel váltotta le LGA típusú socketjeit, a három lépcsős megoldással ez jó esetben egy év pluszt jelent majd. Kérdés, hogy ehhez mit szólnak majd az alaplapok gyártói, akik üzleti modellje a korábbi stratégiára épülnek. Persze az Intel akár folyamodhat szoftveres barikádhoz is, mint például az LGA1150 esetében. Ebben az esetben a foglalat nem változott, ugyanakkor az Intel hivatalosan csak az új, 90-es sorozatú lapkakészletek mellé nyújtott Broadwell támogatást, mely gyakorlatilag a korábbi széria átnevezése volt.