Komoly előrelépés GDDR5X memóriaszabvány

Nagy előrelépést kínál az okosan fejlesztett GDDR5X grafikus memória, ami így akár még a HBM térhódítását is lassíthatja. A duplázott sávszélesség mellett csökkenhet a fogyasztás, ráadásul az implementációhoz csak kisebb módosítások szükségesek.

Végleges a GDDR5X specifikációja, jelentette be a különféle memóriák szabványosításával foglalkozó JEDEC. A GDDR5X az előd által kitaposott ösvényt követi, az új megoldás gyakorlatilag a GDDR5 kiterjesztésének tekinthető, így a partnerek részéről relatíve egyszerű lehet az implementáció. A fejlesztések eredményeképp duplájára nőtt a maximálisan elérhető sávszélesség, miközben a fogyasztás valamelyest csökkent. Az új grafikus memóriák elsősorban különféle videokártyákon, GPU-k mellett köszönhetnek majd vissza.

Jogod van tudni: mankó kirúgáshoz, munkahelyi szkanderezéshez Ezúttal egy mindenki számára kötelező, de laza jogi különkiadással jelentkezünk. Ennyi a minimum, amit munkavállalóként illik tudnod.

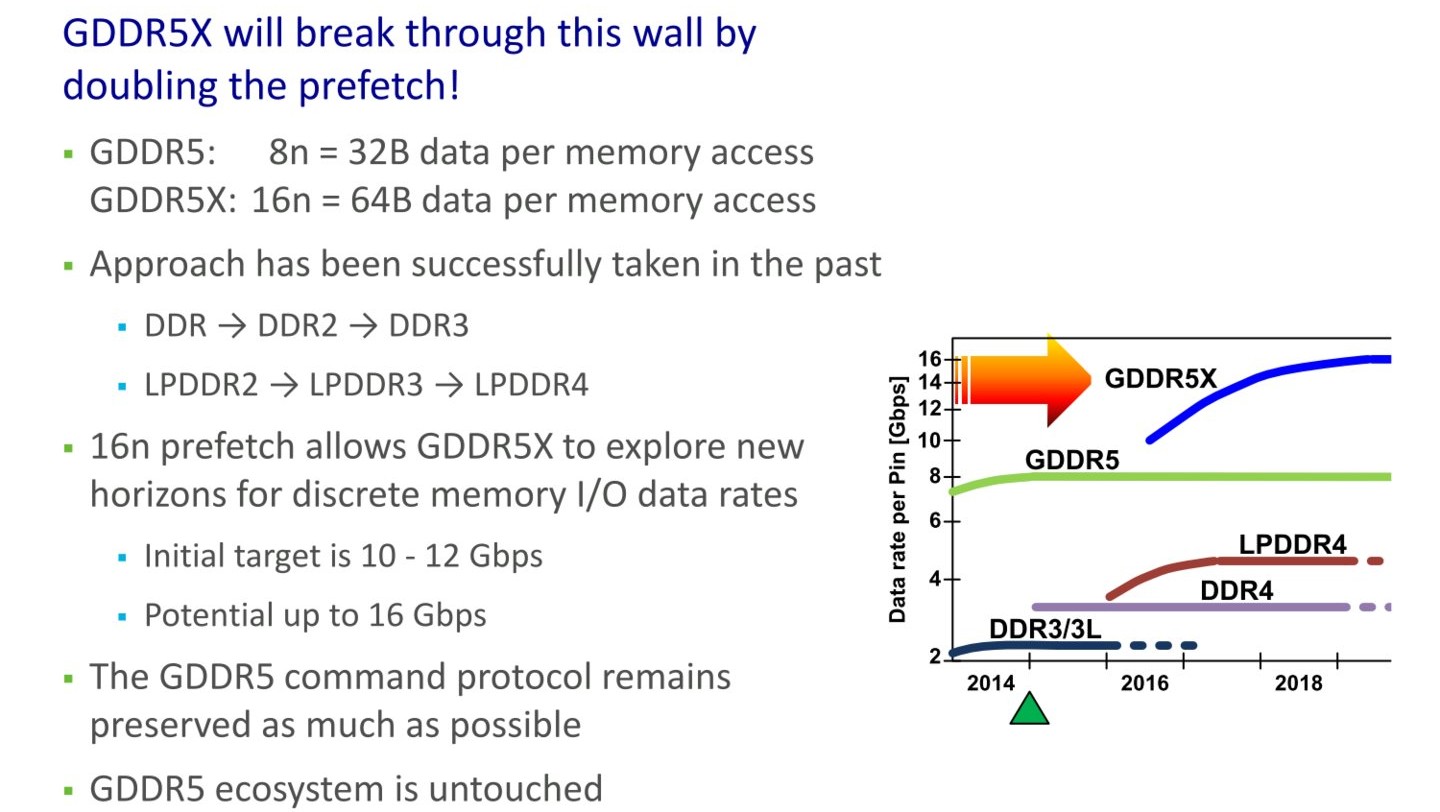

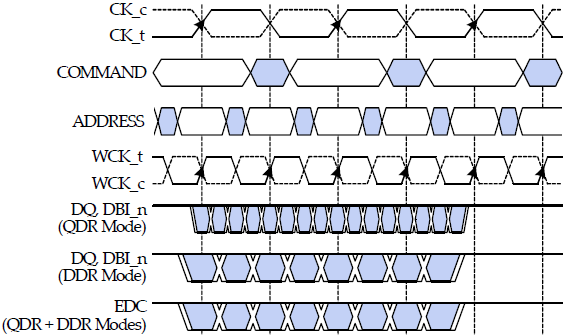

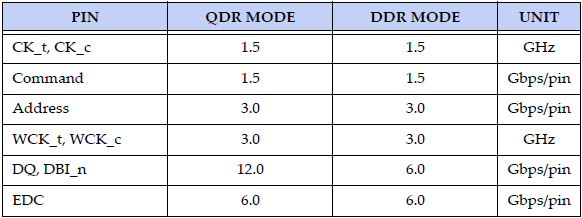

A GDDR5X szabvány a DDR memóriák evolúciós irányát követi, a tervezők a belső adatbusz sebességét duplázták meg, ezzel megkerülve a magórajel, illetve a disszipáció további emelését. Az adatírások és olvasások sebességét meghatározó, a CK órajel (command clock) dupláján működő két differenciált műveleti frekvenciához (WCK_t és WCK_c) rendelt két-két adatszó már QDR (Quad Data Rate) üzemmódban is működhet. Ehhez az összesen négy DQ/DBI_n adatszót egy külön, a WCK-ból származtatott órajelre ülteti a rendszer, így egyetlen CK ciklus alatt négy egységnyi adat továbbítható. Ezzel a GDDR5-höz mérten kétszer annyi, már összesen négy darab 32 bites adatszó (data word) forgalmazható az IO-puffer relációjában.

Emellett az előd GDDR5 8N-prefetch értékét a duplájára, 16N-re emelték. Ennek megfelelően a memória magján belüli írási vagy olvasási művelet mérete már 512 bites (64 byte) lehet, mely két CK órajelciklus alatt megy végbe. Ugyanennyi idő alatt tizenhat darab 32 bites adat mozgatható az IO-puffer viszonylatában. Mindkét érték pontosan duplája a GDDR5 esetében meghatározottaknak, ennek megfelelően pedig azonos magórajelet alapul véve kétszeresére nőtt a GDDR5X effektív órajele.

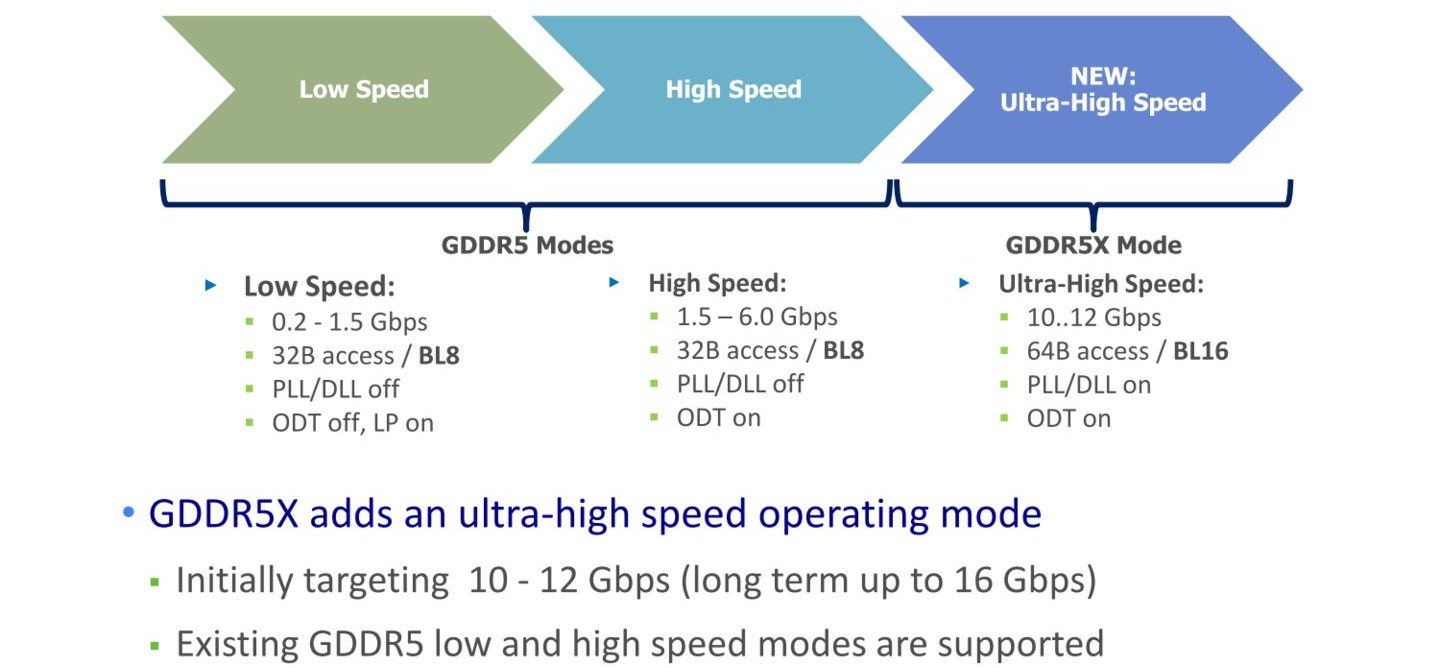

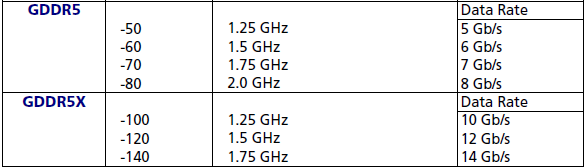

A fenti, a Micron által "ultra-high speed" elnevezésű mód alkalmazása nem kötelező, a GDDR5X szabvány a GDDR5 működési módjait is magában foglalja, aminél a négy DQ/DBI_n adatszó DDR (Double Data Rate) módban, gyakorlatilag a WCK órajelére ültetve operál, 8N-prefetch mellett. Ennek célja a kompatibilitás megőrzése volt, így az új szabványú chipek a GDDR5X-re még nem felkészített memóriavezérlőkkel is működhetnek.

A GDDR5 lassan nyolc éve a piacon van, ez idő alatt pedig rengeteget fejlődött a gyártástechnológia. A JEDEC előtt ez utat nyitott az üzemi feszültségek csökkentésére, így a GDDR5X chipek magfeszültsége (Vdd) 10 százalékkal, 1,35 voltra csökkent. Az előd esetében két feszültségi értéket (1,5 és 1,35 volt) határozott meg a szabvány, a végső választás a gyártókra volt bízva, akik rendszerint a magasabb értékkel terveztek, mostantól erre már csak nem szabványos keretek között lesz lehetőség.

Emellett a chipek aktiválásához szükséges Vpp (Pump Voltage) is csökkent, ami jelentősen, 3,3-tól 1,8 voltra esett, bár ez jóval kevésbé redukálja a fogyasztást mint a kisebb magfeszültség. Ugyan a fogyasztást befolyásoló legfőbb értékek csökkentek, a szabvány immáron kötelezően leírja a beépített hőmérő alkalmazását, mely az üzembiztonságot hivatott növelni. Amennyiben bármelyik chip túllépi a gyártó által meghatározott kritikus szintet, a memóriavezérlő csökkentheti a disszipációt (pl. az időzítések növelésével), ezzel óvva azt egy esetleges károsodástól.

Az effektív órajel mellett a chipek kapacitása is változott. A GDDR5 specifikációjában a legkisebb chip 512 megabites (64 megabájt), míg a legnagyobb 4 gigabites (512 megabájt). A GDDR5X esetében mindkét léc jóval feljebb került, így a korábbi maximumból minimum lett, amivel a legkisebb chip már 4 gigabites (512 megabájt), a legnagyobb kapacitású pedig 16 gigabites (2 gigabájt). A köztes 8 gigabites chip mellett még további lépcsőt iktatott be a JEDEC, az új 6 és 12 gigabites (768 és 1536 megabájt) modelleknek köszönhetően kisebb ugrásokkal növelhető a termékek memóriamérete.

A belső felépítés változásai a tokozást is befolyásolták. Pozitívum, hogy a chipek fizikai mérete kisebb lett a GDDR5-höz képest, a korábbi szabvány 12x14-es értéke 10x14 milliméterre csökkent, így egy memória területe 168-ról 140 mm2-re zsugorodott. Kevésbé jó hír, hogy ezzel párhuzamosan az érintkezők száma 170-ről 190-re kúszott fel, mely változás több vezetéket kíván meg a chipek alapjául szolgáló nyomtatott áramkörön.

HBM ellenfél vagy sem?

A GDDR5X úgy lépett előre nagyot, hogy a lehető leginkább próbálta megőrizni az előd tulajdonságait. Ezzel a szabványra épülő memóriákat alkalmazó gyártóknak csupán kisebb módosításokat kell eszközölniük az implementációhoz, ami költségtakarékossá teszi a megoldást. Emellett ütős érv, hogy az effektív órajel és a kapacitás együttes növelésével fele annyi chipből összerakható a korábban GDDR5-tel elért sávszélesség és memóriakapacitás. Hab a tortán, hogy ehhez a memóriavezérlő felől elég egy kisebb, fele akkora buszszélesség (pl. 256->128 bit) ami a GPU tervezésének oldaláról nagy könnyedség, a jóval egyszerűbb NYÁK-ról nem is beszélve, amivel bőven kompenzálja a chipeken található 20 többlet érintkező apró problémáját.

A Micron aktuális GDDR kínálata

Természetesen a gyártók dönthetnek ellenkezőleg, a korábbi buszszélesség, illetve komplexebb nyomtatott áramkör megtartása mellett ily módon egyszerűen duplázható a maximális sávszélesség. Például egy GeForce Titan X kártyán a chipeket azonos magórajelű GDDR5X-re cserélve a 336,5 GB/s-os sávszélesség könnyen 673 GB/s-ra duplázható lenne. Persze ennél azért több fejlesztést kíván meg az új memória alkalmazása (hiszen a memóriavezérlőt is át kell dolgozni), ugyanakkor a HBM implementálásánál még így is lényegesen egyszerűbb lesz a tervezők dolga.

A közelmúltban már második generációjába lépett nagy sávszélességű rétegzett memória (HBM) a maximális sávszélességet és kapacitást, az alacsony fogyasztást, illetve a kis helyigényt tekintve azonban továbbra is vezet. Mindezért ugyanakkor komoly árat kell fizetni, ugyanis a HBM-hez szükséges, a processzorral való összeköttetést biztosító interposer szilíciumlapka kifejlesztése bonyolult és költséges folyamat, ráadásul a memóriachipek ára is magasabb mint a már alaposabb bejáratott GDDR szabványok egyes tagjaié. Ennek fényében rövidtávon (1-2-3 év) remek alternatíva lehet a GDDR5X, mely jóval kisebb plusz költséget és kockázatot hordoz mint az innovatív rétegzett memória. Az új szabvány miatt nem kizárt, hogy a HBM idén sem mozdul lejjebb az abszolút csúcskategóriából, ezt látva pedig a Micron mellett a HBM-et kifejlesztő és propagáló Hynix, illetve a szintén dél-koreai a Samsung is beszállhat a GDDR5X chipek tömegtermelésébe, melyek valamikor az év második felében kerülhetnek piacra.