Végre új szabványt kapott a rétegzett memória

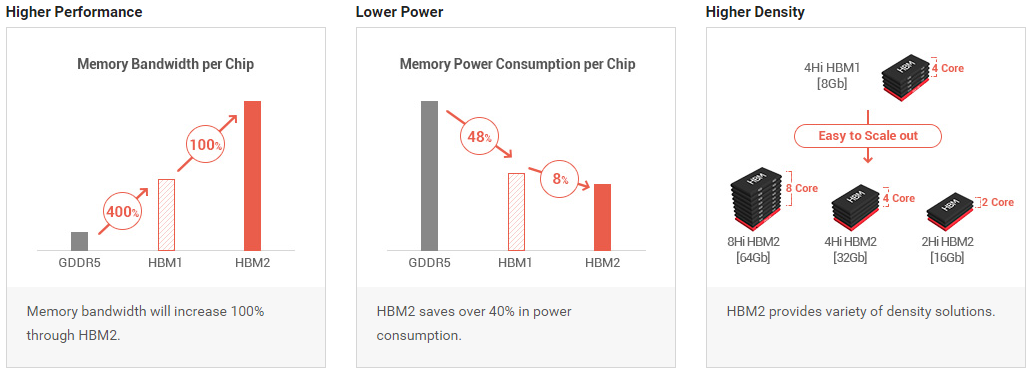

Szabványt és specifikációt kapott a rétegzett memória második generációja. Az új HBM-szabvány duplázza az elérhető sávszélességet, miközben jelentősen növeli a chipek maximális kapacitását.

Véglegesítette a HBM, azaz a nagy sávszélességű rétegzett memória második generációjának specifikációit a JEDEC. Az új memóriatechnológia már tavaly elkezdte hódító útját az AMD GPU-kkal, idén pedig az Nvidia is piacra dobja első HBM-mel szerelt grafikus egységeit. A JEDEC, a memóriatechnológiák (például DDRx vagy GDDRx) szabványosításával foglalkozó iparági testület most lefektette a következő generáció sarokköveit.

USA Tech Hub: ahonnan a passzátszél fúj Minden, ami a technológiai szektorban történik, jellemzően az USA-ból indul.

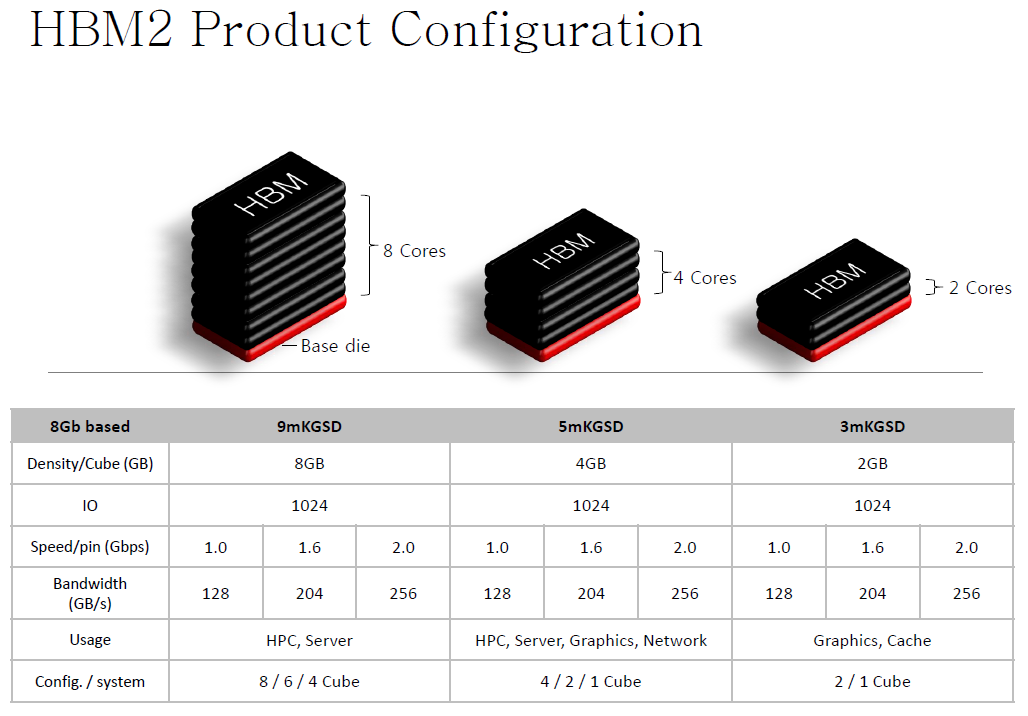

A testület mind átviteli sebességben, mind pedig kapacitásban jelentős előrelépést ért el a néhány helyen csak HBM2-ként emlegetett szabvánnyal. A második generációs HBM 1 GHz-re emeli az 1024 bit széles csatornával rendelkező chipek maximális órajelét, illetve azok sávszélességet, ami ezzel már legfeljebb 256 GB/s lehet. Emellett megmarad az 500 MHz-es verzió, és készült egy köztes 800 MHz-es variáns is, mely chipenként 204 GB/s-os sávszélességet kínál. Az egymásra helyezett lapkák számától függően változik a chipek kapacitása, mely így már 8, 4, vagy 2 GB lehet, illetve igény szerint akár 1 GB-ig is lemehetnek a gyártók.

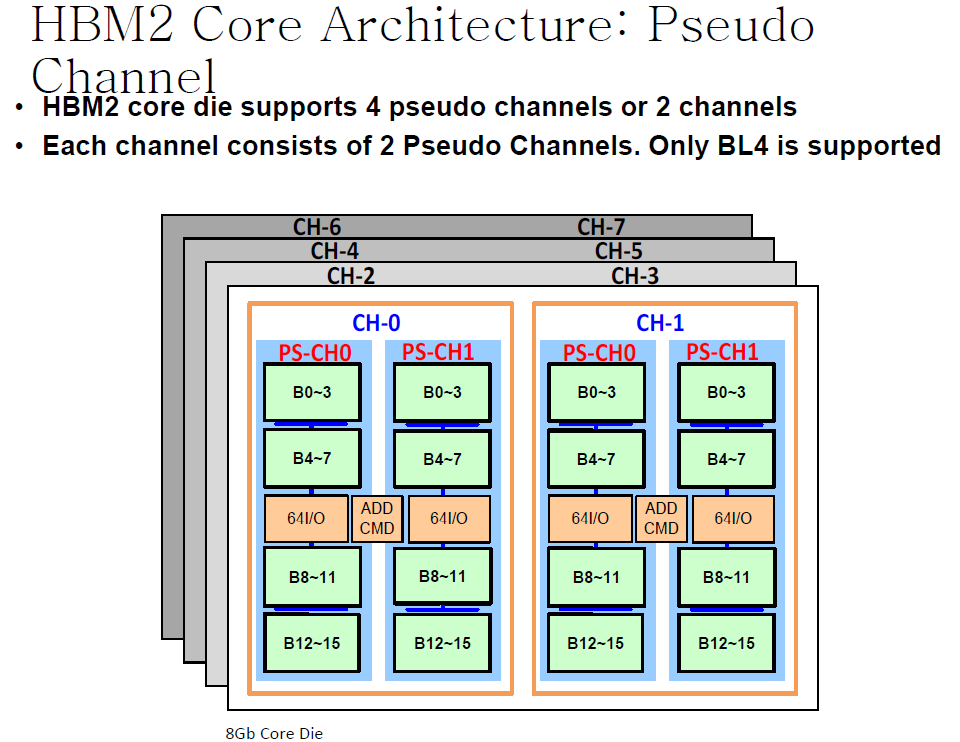

Ezen felül két lényeges újítást is dokumentált a JEDEC. Az egyik az úgynevezett álcsatornák (pseudo channel) használata. Ezzel a lapkánkénti két darab, egyenként 128 bites fizikai csatorna összesen négy, fejenként 64 bites álcsatornára bontható szét. Így a csatornánkénti kapacitás 4-ről 8 gigabitre emelhető, miközben bizonyos esetekben hatékonyabban aknázható ki a sávszélesség. A logika némiképp hasonlít a Hyper-Threadingre - az álcsatornák révén növelhető a fizikai csatornák kihasználtsága és ezzel a hatékonyság.

Az üzembiztonság növelése érdekében a hőmérsékleti értékek monitorozásán is fejlesztett a JEDEC, melynek alkalmazása a 4 GB-os vagy annál nagyobb lapkák esetében kötelező. A Catastrophic Temperature Sensor nevű egység az összes lapka hőmérsékletét nyomon követi, amennyiben pedig bármelyik túllépi a gyártó által meghatározott kritikus szintet, a memóriavezérlő csökkenteni a disszipációt, vagy akár ideiglenesen le is kapcsolja a lapka működését, ezzel megóvva azt a végzetes károsodástól.

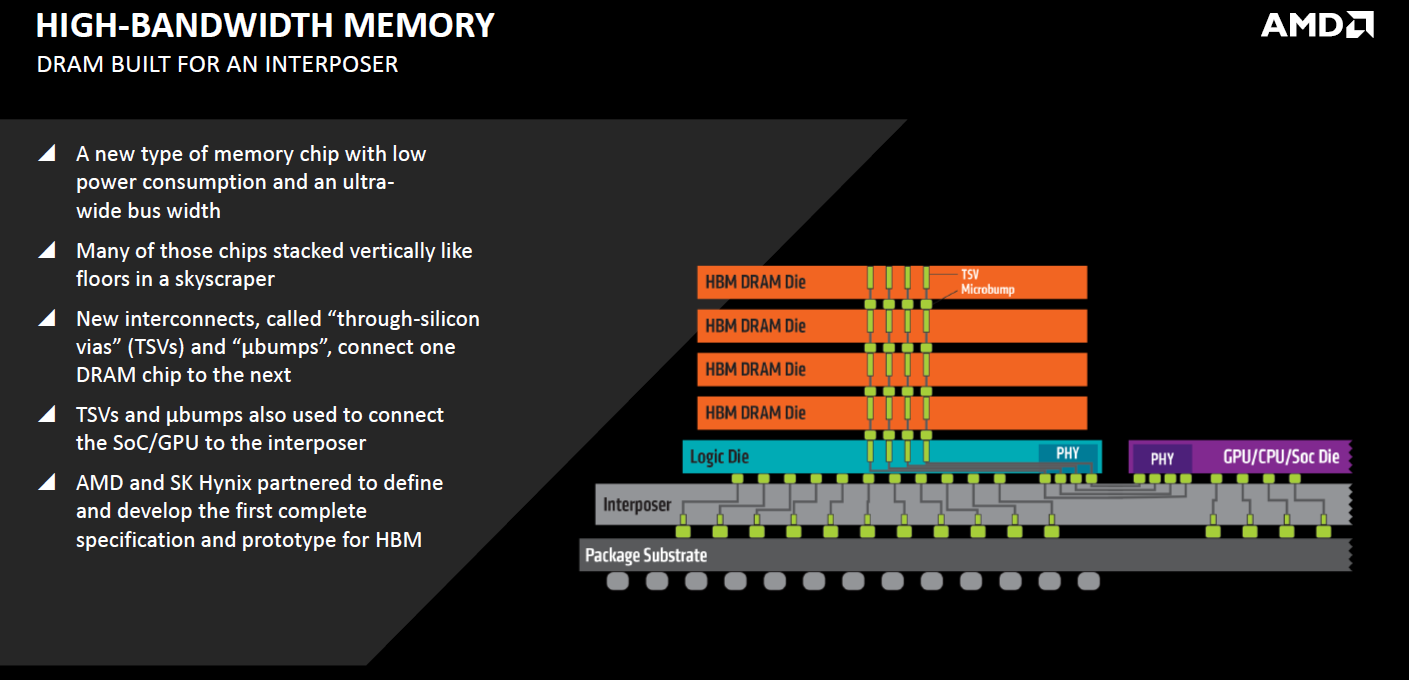

A módosítások miatt a chipek fizikai mérete is változik, a második generációs memóriák kissé meghíztak. A chipek alapterülete 5,48x7,29-ről 7,75x11,87 milliméterre nőtt, magasságuk pedig 0,49-ről 0,72 milliméterre változott. Az egyes lapkák közti összeköttetéshez továbbra is a TSV (through silicon) technológiát alkalmazzák. Ezzel az egymásra rétegzett szilíciumlapkákon belül kialakított több száz járaton keresztül futnak végig a vezetékek, így elhagyható a relatíve vastag elválasztóréteg, illetve a huzalok hossza is számottevően redukálható.

Második generációs HBM chipek a Hynix és a Samsung műhelyéből várhatók. A nagy sávszélesség mellett alacsony fogyasztással kecsegtető új memóriák a magas költségek miatt elsőként az AMD "Vega" és az Nvidia "Pascal" felsőkategóriás grafikus kártyáin köszönhetnek vissza, jövőre pedig akár processzorokon is feltűnhetnek.