Az Intel és a Toshiba is 3D NAND-dal támad

Az Intel-Micron és a Sandiskkel karöltve dolgozó Toshiba is bejelentette első 3D NAND technológiás tárolóit. Az első minták kiszállítását már mindkét páros megkezdte, a végleges termékek azonban csak jövőre kerülnek a boltokba.

Nem bírnak magukkal a félvezetőgyártók, egy napon belül mindjárt két fontos bejelentés is napvilágot látott új NAND technológiákkal kapcsolatban. Elsőként a Toshiba beszélt új, nem kevesebb mint 48 réteget tartalmazó 3D NAND eszközéről, röviddel ezután pedig az Intel és a Micron közös eseményen számolt be saját eredményeiről 3D NAND-téren - igaz, a két cég már tavaly novemberben bejelentette, hogy belép a területre.

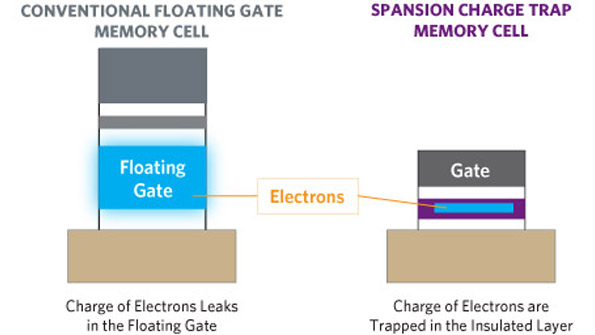

A flash (NAND) memória egyik legnagyobb problémája a relatív alacsony kapacitássűrűség a hagyományos merevlemezekhez viszonyítva. Az eddig követett megoldás, az egyre alacsonyabb csíkszélességű gyártás mára gyakorlatilag zsákutcának bizonyult: ezek a memóriák az elektronok csapdába ejtésével tárolnak információt, az egyre kisebb cellákba pedig annyira kevés elektron fér, ami már a tárolás stabilitását, és ezzel élettartamát illetve sebességét a kritikus szint alá csökkenti.

Introvertáltak az IT-ban: a hard skill nem elég Már nem elég zárkózott zseninek lenni, aki egyedül old meg problémákat. Az 53. kraftie adásban az introverzióról beszélgettünk.

A megoldás, amint azt az e téren úttörő Samsung már felfedezte a sík (egyrétegű) NAND lecserélése egy rétegzett megoldásra. A sűrűn egymásra helyezett rétegek cellamérete jóval nagyobb lehet, a csíkszélesség a 10-20 nanométer helyett 35-50 nanométerre emelkedhet úgy, hogy miközben a kapacitássűrűség tovább növelhető. A rétegzés persze megnöveli a gyártás abszolút költségét, de a fajlagos, kapacitásarányos költség még így is számottevően alacsonyabb tud lenni.

A vertikálisan rétegzett NAND flash lapkák terén tehát a Samsung lépett elsőként, a koreai gyártó már 2013 augusztusában kiadta első vállalati ügyfeleknek szánt V-NAND memóriáit, egy évre rá pedig annak konzumer verzióját is. Az Intel (illetve flash-ipari partnere, a Micron) és a Toshiba most bemutatott termékeivel igyekszik megvetni lábát a területen.

A minták már úton, a kész termékek jövőre érkeznek

A memóriatechnológiáját a SanDiskkel együttműködésben fejlesztő japán Toshiba egy 48 rétegű, 128 gigabites 3D NAND egységet leplezett le, amelyet új, BiCS (Bit Cost Scaling) névre keresztelt technológiájára épít. A koncepció lényege, hogy az a megszokott, lebegőkapus szerkezet helyett egy szigetelőkből készült úgynevezett töltéscsapdát használ, az elektronszivárgás megfékezése végett - a megoldás hasonlít a területen komoly rendelkező már-már "veteránnak" számító Samsung, TCAT (Terabit Cell Array Transistor) technológiájához.

Ahogy arra az AnandTech is rámutat, különösebben nem meglepő, hogy a vállalat nagyon nagy számú, 48 réteget helyez egymásra. A cég ugyanis sík-NAND memóriáiban 15 nanométerig jutott, hasonló kapacitássűrűséget pedig extrém rétegszámmal tudott elérni a gyártó. A lapkákból már elérhetők az első minták, a termékek a boltokban azonban várhatóan csak jövő év második felében tűnnek fel.

Olcsóbb és nagyobb tárolók?

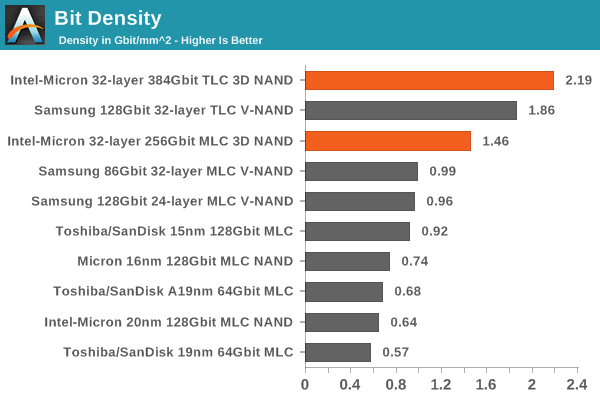

Az Intel-Micron termékéről már tavaly óta tudni lehetett, hogy annak első generációja egy 32 rétegű, 256 gigabites MLC-s lapka lesz, amelynek kapacitása TLC (cellánként három bitet tároló) módban szilíciumlapkánként (die) 384 gigabitre turbózható fel. A két vállalat itt a hagyományos lebegőkapus megoldást választotta, ami potenciálisan olcsóbb tárolókat hozhat a gyártópáros kínálatában.

Grafikon: AnandTech

Noha a vállalat nem fedte fel, hogy pontosan milyen litográfiát használ az új termék esetében, annyi azonban tudható, hogy a 3D NAND elektronszáma nagyjából megegyezik majd az 50 nanométeres eljáráséval, sőt, annál valamivel több is lehet - ez csaknem tízszeres növekedést jelent a 16 nanométeres eljáráshoz képest. Az AnandTech az Intel-Micron által használt szilíciumlapkák méretét nagyjából 175 és 170 négyzetmilliméter közé teszi, ami bár jóval nagyobb mint a Samsung V-NAND technológiájánál látott 87, sőt 69 négyzetmilliméteres értékek, cserébe bitsűrűség terén a koreai gyártó termékét is maga mögött hagyja.

A technológia az árcsökkenés mellett potenciálisan a tárolókapacitásra is pozitív hatással lehet: a cégek szerint az eljárással akár 10 terabájt tárhellyel ellátott, szabványos 2,5 hüvelykes SATA-s SSD-k is piacra kerülhetnek. A nagy méret hátránya, hogy ekkora chipek nem ágyazhatóak a népszerű microSD modulokba, így elsősorban SSD-kben vagy mobilos háttértár formájában találkozhatunk majd viszont velük.