Meglepetés: máris itt az első szerveres Broadwell

Újabb megelőző csapást kaptak a szerveres piacra belépni szándékozó leendő versenytársak az Inteltől. A cég tempósan lefedte az eddigi legolcsóbb Xeonok és az C200-es Atomok közötti rést, az új lapka ráadásul a magas integráltságnak köszönhetően hatékonyságban is újat mutat.

Eltökélt szándéka az Intelnek, hogy nem engedi be a versenytársakat az általa dominált szerveres piacra, ezért a vállalat most gőzerővel fejleszt olyan termékeket, amelyek a terület még le nem fedett szegmenseit célozzák. A stratégia: megakadályozni, hogy a tömegszerverek piacán az ARM vagy a POWER architektúra lendületet tudjon venni. Az Intel félelme érthető, a felhasználók igényeire egy pillanatra nem figyelt a cég, és ezalatt kinőtt a földből egy, mára másfél milliárd egységet mozgató okostelefonos világ - amelyben az Intelnek nem osztottak lapot.

A cég most mindent elkövet, hogy a legfontosabb piacának számító szerveres világban megőrizze dominanciáját, a kihívók alól pedig még azelőtt kihúzza a szőnyeget, mielőtt azok szoftveres-hardveres ökoszisztémát tudnának növeszteni maguk köré. A stratégia legújabb állomása ma mutatkozott be: ismerkedjünk meg a Xeon D-vel, marketinges nevén a Xeon processor D familyvel.

Első dobás: system-on-a-chip

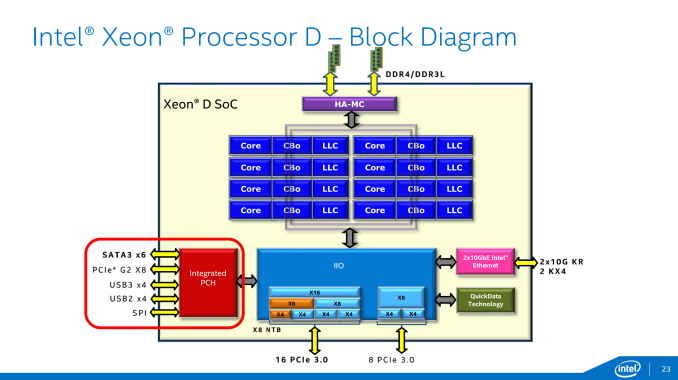

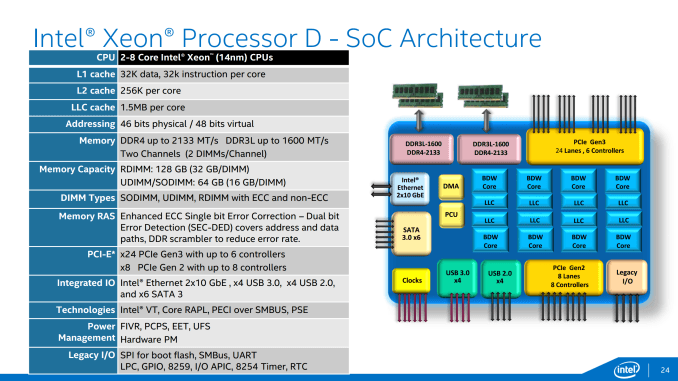

Nem meglepő, hogy ugyanaz a válasz a platformszintű fogyasztás csökkentésére a szervereknél is, mint a telefonokban és az ultrabookokban: magasabb integráció. Pontosan ezt az elvet követte a Xeon D-nél az Intel, a vállalat a platform szinte minden elemét a processzorra integrálta, így az joggal nevezhető rendszerlapkának (system-on-a-chip, SoC). A memóriavezérlő mellett ugyanis az eddig különálló PCH (déli híd), sőt, a hálózati vezérlő is a processzorra költözött, ami egyrészt azt jelenti, hogy közelebb került (fizikai és logikai értelemben is) a CPU-hoz.

Ennél is fontosabb hozadéka lehet annak, hogy ezek a chipek is a processzorral együtt, 14 nanométeres eljáráson készülnek. A ragyogó fogyasztási karakterisztikával rendelkező gyártástechnológia révén ezen áramkörök fogyasztása meredeken csökkenthető, és ezt a ziccert az Intel nem is hagyta ki. Hogy mekkora előrelépést hoz az integráció? A most bemutatott processzor hőkerete 45 watt, ebbe fér bele a nyolc processzormag, a memóriavezérlő, a teljes I/O-alrendszer plusz a dupla 10 gigabites hálózati vezérlő. Az utolsó kettő együtt mintegy 20-25 wattos állandó fogyasztó diszkrét chip formájában, ez ma már a processzor része.

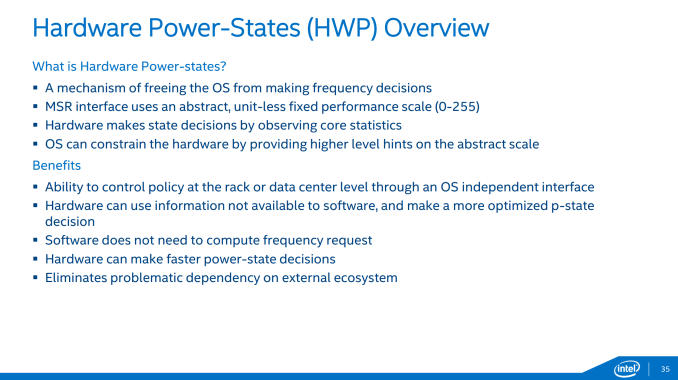

A fogyasztás csökkentését szolgálja az energiaszintek hardveres szabályozása is (HWP, hardware power-states). A Xeon D nem bízza az operációs rendszerre a power state átállítását, az Intel szerint ez ugyanis túl lassan követi le a terhelés változását, túl gyakran fordul elő az, hogy a processzor teljes fordulaton pörög terhelés nélkül, ami energiapazarláshoz vezet. A HWP révén a processzor figyeli a saját terhelését, és a szenzoradatok összevetése nyomán dönt a saját ideális órajeléről. Az operációs rendszernek továbbra is van beleszólása a processzor működésébe, meghatározhatja a minimális és maximális teljesítményszintet, de ezen belül a beépített áramkör nagyon finom lépésekben tudja az órajel-feszültség párost a terheléshez igazítani.

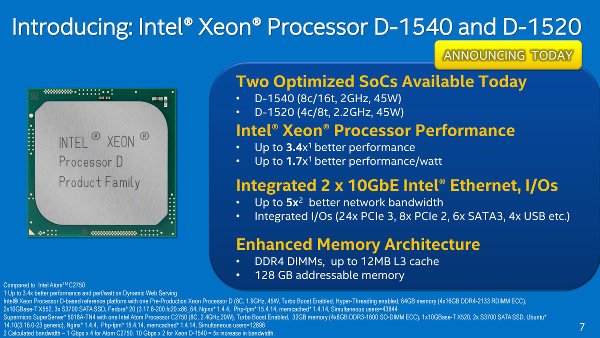

Második dobás: nyolc "asztali" mag

A Xeon D család egyelőre két tagból áll, a D-1540-ből és a D1520-ból . A két lapka egységesen 45 wattos hőkeretet kapott, ebbe nyolc illetve négy Broadwell-generációs, Hyper Threadinggel felszerelt mag fért bele, 2 illetve 2,2 GHz-es névleges órajelen (a Turbo Boost egységesen 2,5 GHz). A magokat 32+32 kilobájt első, 256 kilobájt másodszintű gyorsítótár szolgálja ki, a harmadszintű pedig 1,5 megabájt, magonként. Ezek a processzormagok gyakorlatilag azonosak azokkal, amelyek az Intel konzumer termékeiben ("ötödik generációs Core architektúra") teljesítenek szolgálatot, ezeket fogta most be szerveres feladatra a vállalat. A magokat azonban már egy más architektúra szolgálja ki, az egységeket összekötő adatbusz nem "keresztvas" (crossbar), hanem kétirányú ring bus, amelyen az adatok körben utaznak. Ezt a vállalat a csúcs-Xeonoktól hozta el, ha ott bevált, valószínűleg a Xeon D vásárlói sem fognak panaszkodni.

Rendszerlapka révén a processzorra kerültek az alaplapi chipset funkciói is. Ennek megfelelően a lapkák egységesen dupla 10 gigabites Ethernet csatlakozást kínálnak, ezt 24 PCIe 3.0 és 8 darab PCIe 2.0 csatorna egészíti ki, valamint hat SATA 3.0 és négy USB csatlakozó folytatja a sort. A PCI Express 3.0 közvetlenül a processzorhoz csatlakozik és 16+8, de akár 5 darab x4-es csatornára szétválasztva is kivezethető, ez a felhasználás módjától függően dinamikusan választható.

A memóriavezérlő külön említést érdemel, a processzorok két memóriacsatornát támogatnak, a maximális megcélozható kapacitás 128 gigabájt. Ez ennél persze kicsit bonyolultabb, processzoronként ugyanis csak négy memóriafoglalat támogatott, a maximális kapacitás pedig csak DDR4-es, regisztrált modulokkal érhető el. Nem-regisztrált (UDIMM) modulokkal a maximum 64 gigabájt - a megcélzott szegmensek számára azonban ez is elegendőnek ígérkezik. A legmagasabb támogatott sebesség 2133 MHz (effektív), ez bőséges sávszélességet kínál még kétcsatornás módban is a nyolc magnak.

Tényleg szerveres munkára termett

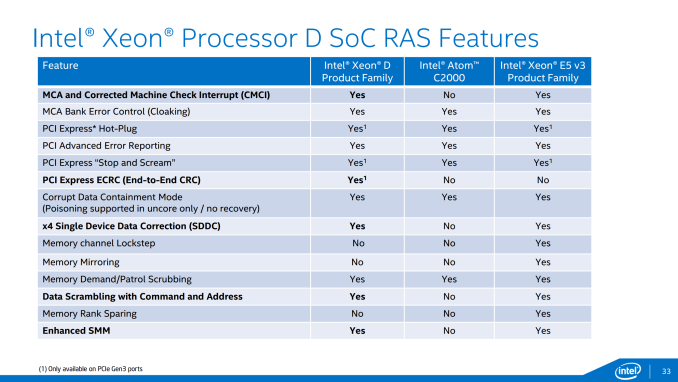

A processzort az Intel komolyan felkészítette a szerveres feladatokra, ezt mutatják a RAS (megbízhatóság, rendelkezésre állás, javíthatóság) terén tett fejlesztések is. Az előrelépés különsen az Atom C2000-zal összehasonlítva szembetűnő, teljes CRC-ellenőrzést kap a PCI Express, illetve bekerült az SDDC is, amellyel a processzor egy teljes DRAM-chip kiesését is adatvesztés nélkül tudja átvészelni. Jellemző, hogy a "nagy testvér" Xeon E5 v3-hoz képest csak az üzleti kritikus rendszerekre és mainframe-ekre jellemző funkciók maradtak ki (memory lockstep, memory mirroring, memory rank sparing), ezeket kivéve mindent tud a Xeon D.

Jogod van tudni: mankó kirúgáshoz, munkahelyi szkanderezéshez Ezúttal egy mindenki számára kötelező, de laza jogi különkiadással jelentkezünk. Ennyi a minimum, amit munkavállalóként illik tudnod.

Ha mindez még nem lenne elég, az Intel azt is bejelentette, hogy a Xeon D-ben már javította a Haswell és korai Broadwell chipek egyik hibáját, amely megakadályozta a TSX (transactional synchronized extensions) működését, így a beépített funkciót végre aktiválni tudta a gyártó ezekben a processzorokban. A TSX-ről korábban itt írtunk részletesen, a funkció a párhuzamosan futó kód futását tudja felgyorsítani azzal, hogy minimalizálja azokat az eseteket, amikor a szálak blokkolják egymást. Logikus, hogy a TSX kijavítása magas prioritást kapott a Xeon D esetében, a kifejezetten többszálú végrehajtásra kihegyezett processzorban ez érdemi gyorsulást hozhat.

Mi az üzleti cél?

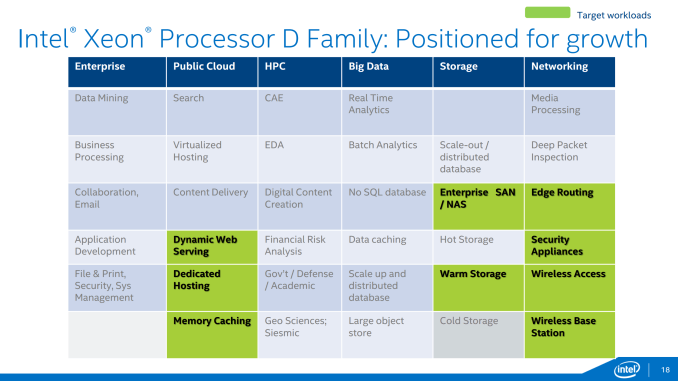

Az új processzorokkal az E3 sorozatú Xeonok és az Atom-magos Avotonok közötti rést töltené be az Intel. Vagyis olyan helyekre ajánlja a Xeon D-t, ahol a Xeon E3 már túlságosan drágák, a C2000-es lapkák viszont túl lassúak voltak. Köztes megoldásként a Xeon D az előbbinél olcsóbb (és lassabb), az Avotonnál lényegesen gyorsabb (de drágább) lesz. Megcélozható piacot bőven lát az Intel, a dinamikus webkiszolgálástól a tárolókig (SAN/NAS/warm storage).