Ráhajt a megbízhatóságra az új Intel Xeon E7

Magyar idő szerint kedd este az Intel hivatalosan is bejelentette a Xeon E7 v2 sorozatú processzorait. A lapkákról számos információ korábban már napvilágot látott, de még maradtak érdekességek, amelyek mindenképp említésre érdemesek.

Ahogy azt a korábbi cikkünkben már írtuk, a Westmere-EX kódnevű skálázódó Xeonok 2011 áprilisi bevezetése után az Intel kihagyta a 32 nanométeres Sandy Bridge generációt, az új processzorok a 22 nanométeres Ivy Bridge mikroarchitektúrára épülnek. A csúcsváltozatok 15 magot és 37,5 megabájt harmadszintű gyorsítótárat kaptak, amelyen a magok megosztoznak. A harmadszintű gyorsítótár sávszélessége 450 GB/s. Az új chipekről részletesebben ebben a cikkben írtunk, most az azóta felfedett technikai részletekre koncentrálunk.

Nagyobb megbízhatóság

A skálázódó Xeonokat az Intel egyértelműen a RISC processzorokkal szemben pozicionálja ma már. A vállalat által citált adatok alapján a négyfoglalatos szerverek szegmensében 80 százalék körüli a piaci részesedése a Xeon-alapú gépeknek, ha az eladott darabszámokat nézzük, árbevétel tekintetében azonban még csak fele - magyarán szóval a RISC rendszerek jóval drágábbak. Ennek két történelmi oka van, az egyik a RISC gépek hagyományosan nagyobb teljesítménye, a másik pedig az általuk kínált RAS (Reliablity, Availability, Serviceability) jellemzők, amelyek végeredményben nagyobb megbízhatóságot jelentenek.

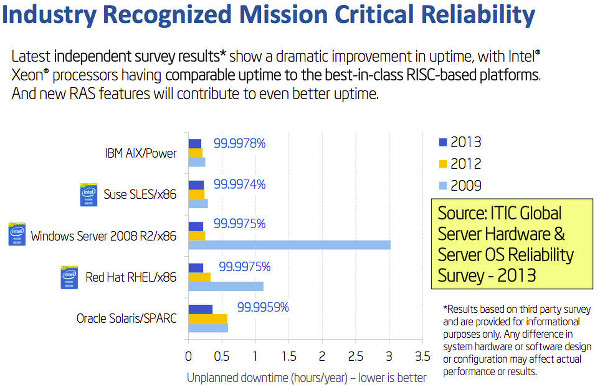

Időközben az x86 világ teljesítményben megelőzte a RISC chipeket (egy későbbi cikkben kitérünk rá, mennyire), és a cég által idézett nemzetközi felmérés alapján mára a Xeonok és a rajtuk futó operációs rendszerek (Linux és Windows) kombinációja rendelkezésre állás terén sem marad el látványosan a RISC/UNIX szerverektől. A citált adatok alapján a Linuxot vagy Windowst futtató Xeon szerverek nem tervezett leállások tekintetében fej-fej mellett teljesítenek akár az IBM POWER/AIX, akár az Oracle SPARC/Solaris gépekkel.

Okos memóriavezérlő

Érdekes fejlesztése az új Xeon-generációnak a memóriavezérlő. Az Intel is tisztában van azzal, hogy a piacon milyen sebességgel nyer teret az "in memory" számítástechnika, vagyis az a paradigma, amikor az adatok nem háttértáron, hanem teljes egészében az operatív memóriában helyezkednek el, ezért a processzorokat úgy alkotta meg, hogy hatalmas memóriakonfigurációkat is kezeljenek, mégpedig gyorsan. Ugyanakkor a skálázódó Xeonok által megcélzott piacon igény van a hibatűrésre is, az olyan feladatok esetén mint például a pénzügyi adatok feldolgozása.

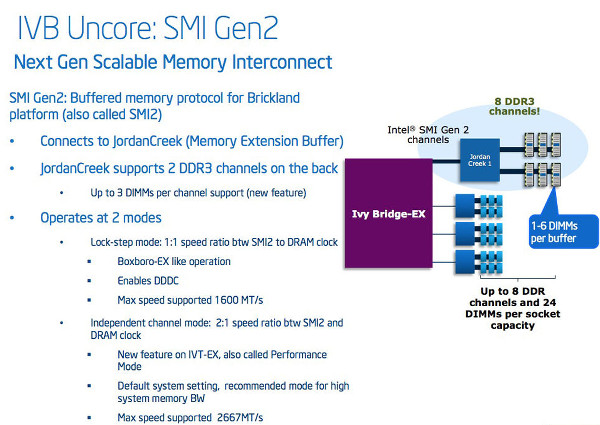

Erre a két igényre válaszul az Intel rugalmas memóriakonfiguráció lehetőségével vértezte fel az új Xeon-generációt, amelynek alapja a Jordan Creek nevű memóriapuffer-chip. A Jordan Creekből egy foglalathoz négy csatlakozhat, mindegyik két Scalable Memory Interconnect Gen 2 (SMI Gen2) csatornát támogat, amelyek 3 DIMM-et kezelnek egyenként, így egy foglalathoz összesen 24 DIMM csatlakozhat legfeljebb, ami 1,5 terabájt operatív tárat jelent.

Az SMI Gen2 érdekessége, hogy kétféle működési módot támogat. Az egyik a kimondottan nagy memóriakapacitásra és teljesítményre optimalizált Performance Mode (ez az alapbeállítás), amikor a memória órajele ugyan 1333 MHz-de, de az effektív órajel 2667 MHz. A másik mód (Lockstep) esetén 1600 MHz az órajel A Performance üzemmódot értelemszerűen akkor érdemes használni, ha a teljesítmény fontosabb a hibamentességnél, például médiaszerverek esetén, a Lockstepet pedig akkor, ha az adatbiztonság kritikus. Ebben a módban két-két memóriavezérlő-csatorna párosával, tükrözve hajtja végre a memóriaműveleteket, a Xeon ezzel próbálja meg kiszűrni a hibákat. A Performance vagy a Lockstep módot a gép firmware-ében lehet aktiválni, vagyis a módosításhoz mindenképp újraindítás kell.

Ahogy a korábbi processzorgenerációk esetén, most is Quick Path Interconnect interfésszel kapcsolódnak össze a chipek a multiprocesszoros konfigurációkban. "Glueless", vagyis a skálázódást biztosító külső chip nélkül legfeljebb nyolc foglalatig lehet nyújtózni, de a szervergyártók saját chipsetjei segítségévével ennél nagyobb konfigurációk is kialakíthatók. A processzorok 3 QPI 1.1 linkkel rendelkeznek, az egy foglalatra eső sávszélesség 8 GT/s (gigatransfer/sec), ami a korábbi generációhoz képest durván 25 százalékkal magasabb. Korábbi cikkünkben a kiszivárgott információkra alapozta azt állítottuk, 40 PCI Express sávot támogató vezérlő is került a die-ra, valójában azonban 32 csatornát támogat csak az új chipgeneráció - viszont a vezérlő a Westmere-EX által támogatott Gen2 helyett Gen3 szabványú.

Hogy ne álljon le...

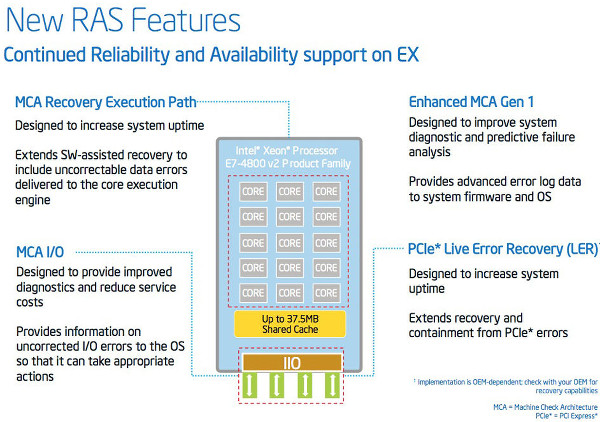

Az Intel számos új fejlesztéssel bővítette az Ivy Bridge generációs skálázódó Xeonok RAS képességeit. A fejlesztések többsége a memóriakezelést érinti, ami nem véletlen: az új Xeonokból már valóban extrém memóriakapacitású gépek építhetők (négyfoglalatos konfigurációban 6 terabájt, nyolcfoglalatos kiépítésben pedig 12 terabájt a csúcs), a nagy mennyiségű memóriát pedig a lehető legjobban meg kell védeni a hibáktól.

Az ECC fejlett formájának tekinthető Double Device Data Correction révén a szerverek két memóriachip meghibásodását is elviselik és képesek a hibás chipekből az adatokat menet közben kimenteni. Ehhez hasonló a Single Device Data Correction, amely egy memóriachip meghibásodását viseli csak el, és a korábban már említett Performance memóriakezelési módban használható, míg a DDDC a Lockstep módban védi az operatív tárat. Az Enhanced DDDC, másképp DDDC+1 révén a két meghibásodott memóriachip esetén is tovább működik az ECC, vagyis a bithibák észlelése és javítása. Ennek párja az SDDC+1.

A problémás memóriamodulokat el tudja szigetelni a rendszer, az Intel mérnökei ugyanakkor beépítettek egy csomó új trükköt annak érdekében, hogy a hibás modult a kicserélés után újra használatba lehessen venni anélkül, hogy a szervert ehhez újra kelljen indítani, ez a Memory On-Lining. A Fine Grained Memory Mirroring pedig azt a lehetőséget adja a felhasználó számára, hogy DIMM szintnél kisebb méretben is tükrözhesse a memóriát. Memóriahiba esetén a szoftverek számára láthatatlanul folytatódik az alkalmazások futása, majd a csere után minden visszaállhat a megszokott kerékvágásba, a gép leállítás nélkül újra 100 százalékban üzemkész.

Jogod van tudni: mankó kirúgáshoz, munkahelyi szkanderezéshez Ezúttal egy mindenki számára kötelező, de laza jogi különkiadással jelentkezünk. Ennyi a minimum, amit munkavállalóként illik tudnod.

A vállalat emellett új Machine Check Architecture (MCA) technológiákkal is felvérezte az Ivy Bridge generációs Xeonokat. Az MCA azokban az esetekben lép színre, amikor egy hibát nem sikerül kijavítani, ebben az esetben a hardver tájékoztatni tudja a rajta futó szoftvereker (operációs rendszert, hypervisort, stb) a problémáról, amelyek meg tudják tenni a szükséges lépéseket, például egy hypervisor le tudja állítani azt a virtuális gépet, amely a hibás memóriaterületet használja.

Az MCA lényege, hogy ne maradjanak nyom nélkül a hibák, az üzleti kritikus feladatok alatt ugyanis ezek okozzák a legnagyobb problémát - egyrészt lehet, hogy az egész gép leáll, másrészt pedig az adatok feldolgozás közben észrevétlenül módosulhatnak, valakinek a bankszámláján egy informatikai hiba miatt megváltozhat az egyenleg például. Ha pedig észrevett egy hibát a rendszer, akkor próbálja azt elszigetelve kezelni, ne kelljen az egész szervert leállítani és a munkát félbeszakítani, minél kisebb legyen a járulékos veszteség.

Az új Xeonokkal szerelt rendszerek már megrendelhetők a legnagyobb szervergyártók (IBM, HP, Dell, Fujitsu, Cisco, stb) kínálatából.