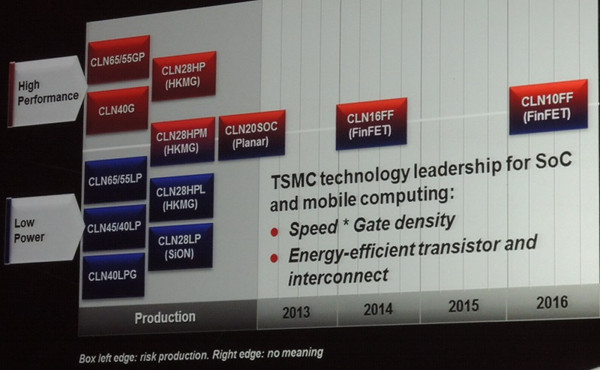

Jól halad a TSMC új technológiáinak fejlesztése

A világ legnagyobb szerződéses chipgyártója, a Taiwan Semiconductor Manufacturing Company (TSMC) jól halad a következő generációs gyártástechnológiáinak fejlesztésével, számol be egy Kaliforniában tartott eseményről az EE Times félvezetőipari szaklap.

A TSMC már több 20 nanométeres lapka mintapéldányát gyártotta le megrendelői számára, például a SPARC M7 korai változatát is, amelyet a múlt heti Oracle OpenWorld konferencián be is mutatott a nagyközönségnek Rick Hetherington, a cég chiptervezéseket irányító mérnöke. Emellett több FPGA-gyártó, köztük a Xilinx és az Altera is megkapta a 20 nanométeres lapkáinak első darabjait, de a mobilprocesszorok legnagyobb gyártója, a TSMC egyik legnagyobb ügyfele, a Qualcomm is tervez ezzel az eljárással természetesen.

20 nm: double patterning

A gyártástechnológia fejlesztésének legfontosabb gátját a TSMC számára is a litográfiai fejlődése jelenti - az évezred elején ígért, ultraibolya fényt (13,5 nanométeres hullámhossz) Ahasználó levilágítók továbbra sem terjedtek el (egyes vélekedések szerint nem is fognak), így minden chipgyártónak trükköket kell bevetnie annak érdekében, hogy a hagyományos, 193 nm-es hullámhosszúságú fénnyel dolgozó eszközei használatban maradhassanak. A 20 nanométeres eljárás mérföldkövet jelent a TSMC-nél, a vállalat itt alkalmazza majd először az ún. "double patterning" eljárást, írja az EE Times.

A double patterning módszernél egyes rétegeknél kétszer világítják le ugyanazt a mintát 193 nm-es hullámhosszú fénnyel, egymást kiegészítő maszkokkal. Az eljárás hátránya, hogy ez a lépés a korábbinál több időt igényel, vagyis a gyártósorok kapacitása csökken, cserébe viszont a korábban milliárd dolláros nagyságrendű befektetéssel megvásárolt levilágítók továbbra is használatban maradhatnak. Emellett immerziós litográfiát is használ a vállalat, vagyis a wafereket nagy tisztaságú vízbe mártják a levilágítás során, a folyadék pedig lencseként segít a fénysugár fókuszálásában. A 10 nanométeres csíkszélességű technológánál triple vagy quad patterningre is szükség lehet már, vagyis egyes rétegeket háromszor vagy négyszer kellhet levilágítani.

A vállalat tájékoztatása szerint a 20 nanométeres eljáráson készült chipek azonos sebesség mellett harmadával kevesebbet fogyasztanak mint a 28 nanométeres lapkák, azonos fogyasztás mellett pedig 15 százalékkal gyorsabbak lehetnek. Iparági becslések szerint a 20 nanométeres alkatrészek gyártása egységnyi területre vetítve 24 százalékkal kerül többe a TSMC-nél mint a 28 nanométeres chipeké, a double patterning ennyivel dobja meg a kiadásokat. Emiatt egyes vállalatok - köztük a Broadcom - már jelezte, nem minden termékét fogja átmozgatni 20 nanométeres eljárásra, a magasabb költségek miatt ugyanis ez nem mindig éri meg. A TSMC által mutatott diák szerint azonban a 20 nanométeres eljárás 1,9-szeres növekedést hoz kapusűrűség terén a 28 nanométereshez képest, vagyis a kisebb csíkszélesség elvileg ellenpontozza a költségnövekedést.

16 nm: FinFET

A 20 nanométeres chipek tömegtermelése még 2013-ben indul be a TSMC-nél, ezt követően pedig jöhet a 16 nanométeres eljárás bevezetése, amelyen a vállalat először alkalmaz FinFET tranzisztorokat - hasonlóakat azokhoz, amelyeket az Intel vezetett be először a 22 nanométeres eljárásán. Az ilyen tranzisztorok alkotóelemei nem rétegszerűen helyezkednek el, hanem három dimenziós struktúrát alkotnak. A forrás (source) és a nyelő (drain) a szubsztrátból kiemelkedő vezetéken kap helyet, amelyet azonban három oldalán érintve, satuszerűen fog közre a kapuelektróda (gate).

Jogod van tudni: mankó kirúgáshoz, munkahelyi szkanderezéshez Ezúttal egy mindenki számára kötelező, de laza jogi különkiadással jelentkezünk. Ennyi a minimum, amit munkavállalóként illik tudnod.

A várhatóan még idén nagyon korai termelésbe álló 16 nanométeres FinFET technológia a 20 nanométeres eljáráson alapul. A TSMC 16 nanométeres eszközei 35 százalékos fogyasztáscsökkenést vagy 20 százalékos teljesítménynövekedést kínálnak a 20 nanométeresekhez képest, ennek azonban ára van: a technológia további költségnövekedést hoz, de csak 1,05-szörös kapusűrűséget a 20 nanométeres eljárással összevetve - ez viszont már nem lesz elegendő a megnövekedő költségek ellensúlyozására, vagyis azonos áramkör hiába kisebb 16 nanométeren gyártva, az előállítási költsége magasabb mint 20 nanométeren.

Költségtakarékos rétegezés

Ahogy a félvezetőgyártási technológiák fejlődése lassul, ami a méretcsökkenést illeti, a gyártók más módszereket dolgoznak ki arra, hogyan lehet az elkészült lapkák méretét csökkenteni - ez főleg mobil eszközök esetén fontos, ahol a fizikai méretek csökkentése különösen kívánatos, például mert maga az eszköz is pici, vagy mert szükség van benne helynek más alkatrészek, például akkumulátor számára. Az egyik ilyen módszer a "stacking", amikor az áramkörök egymásra rétegezettek, a TSMC több ilyen eljáráson dolgozik, az egyik legújabb három réteget kínál 0,5 milliméteres vastagságban, négyzetmilliméterenként csupán 1 dollárcentes költség mellett.

A stacking eljárások széles körű használatát eddig a magas költség gátolta, a TSMC által kidolgozott módszer azonban már elég költségtakarékosnak tűnik a széles körű bevetéshez. A vállalat úgy látja, 2013 végére akár 2000 tűs chipek esetén is képes megvalósítani ilyen típusú rétegezést, 2014-ben pedig már bonyolultabb, 3600 tűs lapkák esetén is meg fog birkózni ezzel a feladattal.