Tizenkét maggal támad a POWER8

A héten zajló Hot Chips 2013 konferencián az IBM először beszélt a nyilvánosság előtt a következő generációs POWER processzorról, a POWER8-ról, amely a HWSW tippje szerint 2014 tavaszán mutatkozhat be és minden eddiginél brutálisabbnak ígérkezik.

A héten zajlik a Palo Altó-i Stanford Egyetemen a Hot Chips konferencia, ahol a vezető félvezetőgyártók beszélnek eddigi technológiai eredményeikről, illetve jövőbeli fejlesztéseikről. Tegnap az IBM képviseletében Jeff Stuecheli tartott előadást, aki az IBM POWER rendszerek hardvertervező mérnöke. Előadásában a következő generációs POWER processzor, a POWER8 főbb fejlesztési irányait vázolta fel.

12 magos szörnyeteg

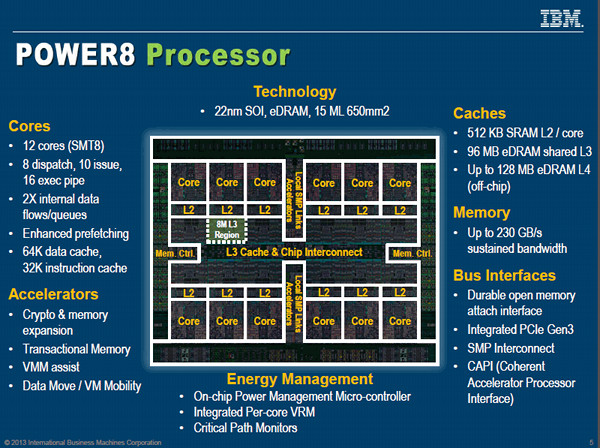

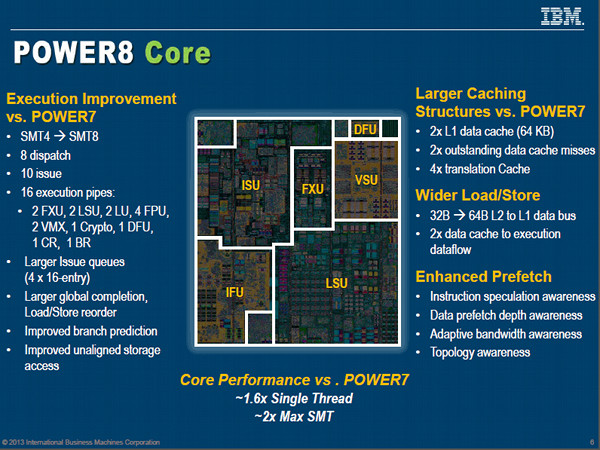

A POWER8 a tegnap elhangzottak alapján minden bizonnyal megtartja a legnagyobb nyers teljesítményt leadó processzornak járó képzeletbeli koronát. A vállalat mérnökei tovább fokozták a chip párhuzamosságát, a POWER7 legfeljebb 8 magjával szemben a POWER8 már tizenkét magot állít csatasorba, amelyek 4 helyett már 8 párhuzamos szálat kezelnek legfeljebb. A magok igazán erőteljesnek tűnnek papíron, egyenként 16 végrehajtóegységgel és 16 fokozatú futószalaggal rendelkeznek. Annak érdekében, hogy a lehető legnagyobb párhuzamosságot ki tudja aknázni és a magok végrehajtóegységei ne várakozzanak, az IBM továbbfejlesztette az elágazásbecslőt és duplájára növelte a párhuzamosan kezelt cache-missek számát.

A prezentáció szerint alapos ráncfelvarráson esett át a prefetcher, vagyis az utasításokat és adatokat előtöltő egység. A prefetcher sok szempontból „adaptív”, azaz figyelembe tudja venni, milyen körülmények között üzemel a processzor, például hogy hány további chp van a rendszerben és azok milyen topológiába vannak kötve – egy helyi memóriavezérlőre kötött memóriából egészen más késleltetéssel lehet előtölteni az adatokat, mint egy távoli processzorhoz tartozóból, például. A prefetcher figyeli a rendelkezésre álló szabad memória-sávszélességet is.

A cég becslései szerint a POWER8 magjai egyszálú feladatvégrehajtás esetén a POWER7-hez képest 1,6-szoros, többszálú végrehajtás esetén pedig kétszeres teljesítménnyel rendelkeznek. Stuecheli szerint összességében két és félszeres gyorsulást hoz a POWER8 a POWER7-hez képest egy foglalatra vetítve, ami a több és erősebb magnak köszönhető - persze hogy ezt milyen feladat alatt kell érteni, arról semmit nem tudni egyelőre. Az IBM rendszerint a saját rPerf metrika mentén adja meg POWER chipjeinek relatív teljesítményét, az rPerf mutató iparági sztenderd tesztek (pl. TPC, SPEC) és a vállalat által összeválogatott egyéb szoftverekből áll össze.

A több erőteljesebb mag beépítését a gyártástechnológiai váltás teszi lehetővé. A POWER8 a tegnapi előadás szerint már 22 nanométeres csíkszélességen készül, a POWER7-et még 45 nanométeres technológiával gyártotta a Nagy Kék, továbbfejlesztett utóda, a POWER7+ pedig 32 nanométeres eljáráson készült. A lapka a fejlettebb gyártástechnológia bevezetése ellenére jócskán meghízott. A POWER7+ 2,1 milliárd tranzisztorból állt és 567 négyzetmilliméteres alapterületet foglalt el, a POWER8 ezzel szemben 650 négyzetmilliméteres lesz. A prezentáción elhangzottak szerint a POWER8 a méretnövekedése ellenére nagyjából a POWER7-éhez hasonló energiakerettel rendelkezik, ami 200 Watt körüli csúcsfogyasztást jelent.

Óriási cache

Ennek fő oka, hogy a több mag mellé nagyobb cache is érkezik. A POWER7+ magonként 32+32 kilobájt elsőszintű és 256 kilobájt másodszintű cache-t, valamint összesen 80 megabájt beágyazott DRAM harmadszintű gyorsítótárat tartalmazott, a POWER8 ezzel szemben magonként 32+64 (I+D) elsőszintű, valamint 512 kilobájt L2 gyorstárral rendelkezik, a kettő közötti adatutak szélességét pedig megduplázta az IBM. Ezzel a célja szintén az volt, hogy az erőteljes magokat ki tudja szolgálni, azoknak ne kelljen se adatokra, se utasításokra várakoznia.

Hogy a processzor és az operatív tár közötti késleltetést minél jobban elfedje, a harmadszintű megosztott cache mérete 96 megabájtra szalad fel, a processzor emellett kivitelőtől függően legfeljebb 128 megabájt off-chip L4 gyorsítótárat is kap, hasonlóan a POWER6-hoz - igaz, ott még a harmadszintű cache volt "off-chip" és csak 32 megabájtos. Az L4 cache maximum sávszélessége 64 gigabájt lesz másodpercenként, 4 GHz-es órajelet alapul véve - az elérhető adatok szerint a POWER8 az elődjéhez hasonlóan 4 GHz körüli órajelen érkezik majd.

A The Register helyszíni beszámolója szerint a memóriavezérlő egy önálló lapkán helyezkedik el, amelynek a kódneve Centaur. Ez a chip tartalmazza az off-chip L4 cache-t és a memóriavezérlőt, amely kezdetben DDR3 szabványú, de az IBM később úgy is dönthet, hogy később DDR4-re cseréli. Ezt úgy teheti meg, hogy magának a processzornak a designját nem kell módosítania ahhoz, hogy módosítson a használt memóriatechnológiát. Egy POWER8-hoz legfeljebb 8 ilyen Centaur chip csatlakozhat, egyenként 16 megabájt cache-sel, így jön ki a maximális 128 megabájt L4 méret. Egy processzor 1 terabájt operatív tárat kezel legfeljebb, de ez a hardveresen gyorsított memóriatömörítés segítségével hozzávetőleg kétszeres használható méretet jelent. Ha a POWER7+-hoz hasonlóan a POWER8-alapú gépek közül is 32 foglalatos lesz a legnagyobb, az 32 terabájt memóriát, 384 magot és 3072 párhuzamos szálat jelent legfeljebb.

Az IBM a POWER7+ lapkában vezette be a lapkára integrált feladatspecifikus gyorsítóáramköröket. A POWER8-ban is lesznek ilyenek természetesen, a prezentáció alapján lesz integrált kriptomotor a titkosítási algorirmusok gyors futtatásához, egy gyorsító a hardveres memóriatömörítéshez, egy a tranzakcionális memóriakezeléssel kapcsolatos feladatok elvégzéséhez, valamint a virtualizációval járó overhead csökkentéséhez is beépítenek ilyet.

Nyitás

Amint arról a HWSW is beszámolt, az IBM nemrégiben úgy döntött, licenceli a Power architektúrát, ennek előremozdítása érdekében megalakította az OpenPower konzorciumot, amelybe olyan cégek szálltak be mint a Google, az (Oracle résztulajdonban levő) Mellanox és az NVIDIA. A szövetség tagjai számára az IBM megnyitja a POWER8 magokhoz, processzorokhoz és a teljes platformhoz kapcsolódó fejlesztési jogokat, valamint licencelhetővé teszi az architektúrához kapcsolódó szellemi tulajdonát.

Jogod van tudni: mankó kirúgáshoz, munkahelyi szkanderezéshez Ezúttal egy mindenki számára kötelező, de laza jogi különkiadással jelentkezünk. Ennyi a minimum, amit munkavállalóként illik tudnod.

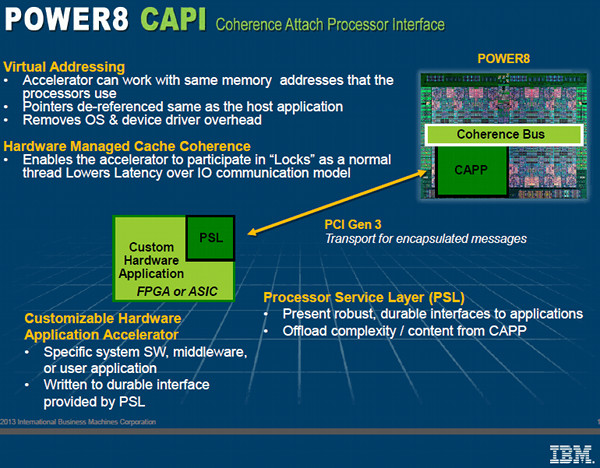

Annak érdekében, hogy a POWER8 jobban beilleszthető legyen más gyártók rendszereibe, az IBM leszámol a GX++ interfésszel, helyét a CAPI (Coherently Allocated Processor Interface) veszi át, amely PCI Express 3.0 felett működve gondoskodik a processzorok közti kommunikációról, illetve lehetővé teszi a külső gyártókról származó gyorsítók (pl. NVIDIA Tesla) beépítését a POWER8-alapú gépekbe. A CAPI-ak köszönhetően a külső gyorsítók ugyanazzal a memóriacímzéssel dolgozhatnak mint maguk a processzorok. A CAPI jelenléte egyben azt is jelenti, hogy a POWER8 integrált PCI Express 3.0 vezérlővel rendelkezik, hasonlóan a legfrissebb Xeonokhoz vagy az Oracle SPARC M5-höz.

Megjelenés 2014 elején?

A Hot Chips konferencián Stuecheli állítólag egy POWER8 prototípust is megmutatott, annak alátámasztására, hogy a fejlesztések milyen jól haladnak, arról azonban nem beszélt, hogy a processzor mikor érkezik piacra. A korábbi POWER-generációk menetrendjéből kiindulva 2014 tavaszi rajt látszik valószínűnek a HWSW szerint, ekkor érkezhetnek meg az első szerverek az új lapkával, vélhetően a középkategóriába (4-8 foglalat), ezeket követhetik a nyáron a belépőszintű gépek (1-2 foglalat), majd a csúcsmodellek (16-32 foglalat).

A Hot Chips programja ma többek között a SPARC M6 részletes bemutatásával folytatódik.