Ilyen lesz a Haswell tranzakcionális memóriakezelése

Új utasításokkal lesz aktiválható az Intel Haswell generációs processzorainak tranzakcionális memóriakezelése - jelentette be a chipgyártó. A szoftveres támogatás hamar széleskörűvé válhat.

Bemutatta a következő generációs processzorainak régóta várt új funkcióját az Intel. A Transactional Synchronization Extension (TSX) a párhuzamos programfuttatást teszi sokkal hatékonyabbá, ezzel sokat gyorsulhatnak a több utasításszálat használó alkalmazások. A technológiát összesen hat új utasítással, két csoportra bontva vezeti be az Intel, a Restricted Memory Access (RTM) a jövő zenéje, a Hardware Lock Elision (HLE) azonban már a Haswell piaci rajtjával egy időben, jövőre széles elterjedtséget mutathat.

Párhuzamos problémák

A párhuzamos végrehajtás továbbra sem triviális, a többszálú feldolgozást továbbra sem használja ki minden alkalmazás, amelyek pedig kihasználják, általában nem optimalizáltak erre a környezetre. A párhuzamosítás rendkívül összetetté válik ugyanis, ha a programszálak egymástól nem függetlenek, például mert egymás eredményeit használják fel vagy közös adatokon dolgoznak. Jelenleg a párhuzamos programozásban a "locking" módszer a legelterjedtebb, ilyenkor a programozó explicite zárolja a szál által érintett adatokat addig, amíg az adott szál futása be nem fejeződik. Jelenleg a zárolást a programozóknak kézzel kell optimalizálnia, hogy a szükségesnél se több, se kevesebb adatot ne érintsen, ez viszont idő- és erőforrás-igényes feladat, amire kevesen vállalkoznak. Komplexebb szoftver esetében pedig megnő az emberi hibák esélye is, ennek megtalálása pedig több millió sor esetében egyáltalán nem triviális.

A problémát természetesen érzékeli az Intel is, a processzorok jövőképeként vizionált több tucat magos, szálak százait egyszerre futtató lapkák hatékony kiaknázására addig esély nincs, amíg a csökkenő hozam elve szerint egy szinten felül már lassul a végrehajtás, nem pedig gyorsul. A chipgyártó ezért aktívan dolgozik a probléma hardveres megoldásán, ennek első eredménye a következő generációs 22 nanométeres Haswell mikroarchitektúrában debütáló Transactional Synchronization Extensions (TSX), amely két új utasításpárral bővíti az x86 ISA-t.

Optimista forgatókönyv

A Hardware Lock Elision (HLE) a hagyományos pesszimista zárolási megközelítést puhítja fel. Míg eddig tipikusan az alkalmazás az összes bemeneti és kimeneti változóra teljes zárolást kért a műveletek végrehajtásáig, a HLE használatával a bemeneti változók zárolására nincs szükség. A megközelítésről itt írtunk részletesen, röviden összefoglalva a processzor alapállapotban azt feltételezi, hogy zárolásra nincs szükség, így elvégzi az előírt utasításokat. Amennyiben a bemeneti adatokban közben valamilyen módosulás áll be, a művelet eredményét elveti és a számítási feladatot újra elvégzi, ezúttal hagyományos, szigorú zárolással.

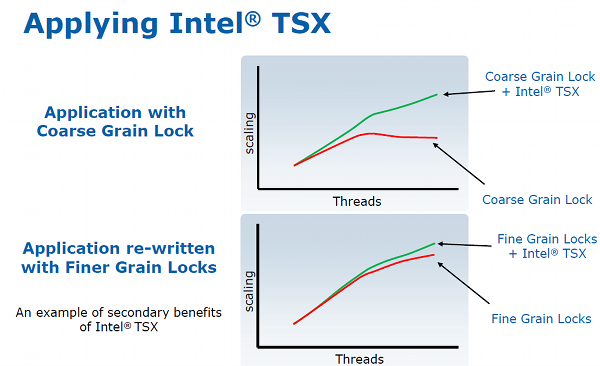

Az Intel szerint ezzel a megközelítéssel a processzor nem pazarol energiát. Ideális esetben a számítási feladat gyorsabban lefut mint korábban, de legrosszabb esetben, ha kétszer kell a feladatot elvégezni, a processzor akkor sem fogyaszt többet, mintha rajtra készen várakozna a szükséges adatok felszabadulására. A teljesítményben azonban drámai növekedést lehet elérni az új megközelítéssel, a gyengén optimalizált kód esetében a skálázódás jobban megközelíti a lineárist, de kézzel optimalizált kód esetén is számottevő gyorsulást hoz a HLE, egyrészt a zárolások további szűkítésével, másrészt azzal, hogy csökkenti a memóriahasználatot és ezzel a gyorsítótárak szinkronizációs forgalmát, tehermentesítve a processzor egyik fontos elemét.

A HLE mellett az RTM (Restricted Transactional Memory) is az új kiterjesztés részét képezi, ennek elterjedésére azonban még várni kell, visszafelé ugyanis nem kompatibilis. Az RTM a HLE alternatív implementációja, amely nagyobb rugalmasságot is ad a programozó kezébe - de működéséhez elengedhetetlen a TSX hardveres támogatottsága, az ilyen processzorok pedig még évek múlva sem jelentik a telepített bázis többségét. Az RTM egyébként képes specifikálni a kritikus kódrész elejét és végét az XBEGIN és XEND utasításokkal, amennyiben pedig a művelet nem fut le sikeresen (megváltoznak egyes változók), akkor az XBEGIN-nél specifikált úton folytatódhat a végrehajtás. A futás szándékosan is leállítható az XABORT utasítással, ekkor a futás automatikusan az alternatív útvonalra vált. Az új TSX utasításcsomag része az XTEST utasítás is, amellyel lekérdezhető, hogy a processzor éppen tranzakcionális végrehajtást végez-e.

Felkészült fordítók

Az Intel bejelentése szerint a HLE teljes visszafelé kompatibilitással rendelkezik, kiaknázásához azonban szükség van a zárolást kérő alkalmazásrészek módosításához. Mivel ezt a feladatot általában külső szoftverkönyvtárak látják el, a könyvtárak cseréjével bármely alkalmazás HLE-kompatibilissé alakítható - állítja az Intel.

Jogod van tudni: mankó kirúgáshoz, munkahelyi szkanderezéshez Ezúttal egy mindenki számára kötelező, de laza jogi különkiadással jelentkezünk. Ennyi a minimum, amit munkavállalóként illik tudnod.

A bejelentések szerint az Intel új utasításait már támogatni fogja a gcc 4.8, a Visual Studio 2012, az Intel saját C fordítójának v13-as kiadása és a glibc 2.17 pedig már most támogatja a megfelelő utasításokat. Ezzel az új utasítások gyakorlatilag minden platformon univerzális támogatásnak örvendenek és mivel az utasítások aktiválása nem igényel semmilyen újraírást, így elegendő a meglévő alkalmazásokat újrafordítani a funkció aktiválásához.

A tranzakcionális memóriakezelés elterjedésével a többmagos processzorokat olyan szoftverek is kihasználhatják a jövőben, amelyek ma képtelenek erre vagy a fejlesztők nem hajlandóak a megfelelő erőforrásokat erre szánni. Mivel többmagos processzorok ma már minden formátumban helyet kapnak, az okostelefontól a noteszgépen és az asztali munkaállomáson át a szerverekig és a HPC-fürtökig, a tranzakcionális memória haszna a számítástechnika minden területén hatalmas előrelépést hozhat a hatékonyságban.

A TSX-ről a múlt heti Intel Developer Forum konferencián tartott előadás prezentációja innen letölthető.