Több mint ráncfelvarrás: érkezik az IBM Power7+

A SPARC T5 mellett a RISC-szerverek piacának mára egyedüli meghatározó szereplője, az IBM is ismertette következő generációs processzorának részleteit. Bár a chip neve mást sugall, a Power7+ alapos vérfrissítésen esett át, távolról sem csak egy magasabb órajelű verzióval van dolgunk.

Elődjénél lényegesen nagyobb teljesítményt ígér a Power7+ processzor, amely a közeljövőben állhat hadrendbe az IBM szervereiben. A közvetlen előd IBM Power7-ről 2009-ben jelentek meg az első nyilvános részletek. A 2010-ben piacra került processzor radikálisan különbözött elődjétől, a Power6-tól, teljesen áttervezett magokat kapott, amelyekből nyolcat állított csatasorba.Egy mag legfeljebb négy utasításszál párhuzamos végrehajtására képes.

Kicsit áttervezett magokkal, hatalmas L3 tárral

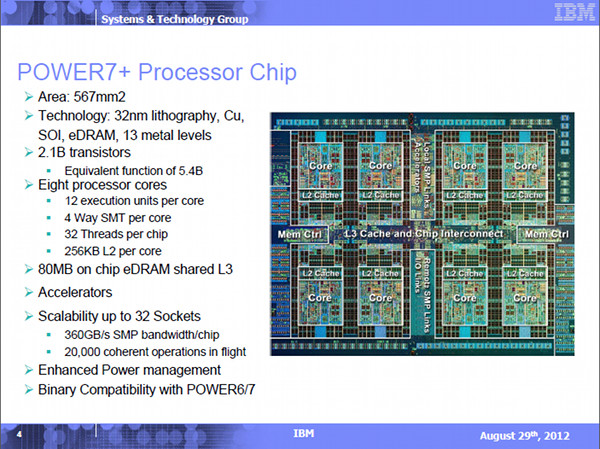

A Power7+ is nyolc magot tartalmaz, azonban a SPARC T5-től eltérően a magokat nem módosítás nélkül emelte át az IBM, hanem finomították őket a mérnökök, és nem csak azért, mert a Power7+ előállításához már 32 nanométeres technológiát vetnek be az East Fishkill-i üzemben a korábbi 45 nanométeres helyett. A Hot Chipsen elhangzott prezentáció alapján valószínűsíthető, hogy a lebegőpontos egységekhez nyúltak hozzá leginkább a mérnökök, a vállalat szerint ugyanis az FPU teljesítménye kétszeresére emelkedett, amit az ígért 25 százalékos órajel-növekedés és a nagyobb L3 cache önmagában nem magyaráz - noha tudjuk, hogy az iparági sztenderd SPEC_fpu2006 teszt "szereti" a nagy gyorsítótárakat.

A magok továbbra is 32+32 kilobájt elsőszintű és 256 kilobájt másodszintű cache-t tartalmaznak, de a fejlettebb gyártástechnológiának köszönhetően gigászi megosztott L3 táron osztoznak. Emlékezetes, hogy a Power7 egyik legütősebb újdonsága volt a chipre integrált 32 megabájtos L3 cache, amelyet a hely- és energiatakarékosság érdekében nem SRAM cellákból építettek fel, hanem beágyazott DRAM-ot (eDRAM) használtak a mérnökök. Az eDRAM ugyan némileg lassabb az SRAM-nál, azonban azonos kapacitás mellett jóval kevesebb tranzisztort igényel, így sokkal nagyobb lehet a gyorsítótár, ami ellensúlyozhatja az SRAM-nál lassabb működést. Amennyiben az IBM a Power7+ 80 megabájtos harmadszintű cache-ét SRAM-ból építette volna, a teljes chiphez 5,4 milliárd tranzisztorra lett volna szükség, eDRAM használatával viszont 2,1 milliárdból sikerült, így a chip "mindössze" 567 mm2 területű.

Okosan, takarékosan

A 32 nanométeres technológia által biztosított extra tranzisztorbüdzsét az IBM igyekezett "okosan" felhasználni. Az L3 cache növekedése mellett ezért megjelent a Power7+ chipben három Asymmetric Math Function (AMF) gyorsító, amelyek a titkosítási feladatoknál használt algoritmusokban gyorsítják a matematikai függvényeket. Szintén három van a processzorban AES/SHA gyorsítóból, valamint egy véletlenszám-generátornak is szorítottak helyet a mérnökök.

A Power7 chipben jelent meg először a memóriatömörítés lehetősége, amely az AIX 6.1 operációs rendszerrel együtt képes volt a szerver memóriakapacitását valós idejű tömörítéssel bővíteni, ideális esetben kétszeres "effektív" kapacitást is elérve. Az Active Memory Expansion (AME) technológiához két hardveres gyorsítót kapott a Power 7+, a "842" névre keresztelt egységek hardverese valósítják meg azokat az egyedi fejlesztésű tömörítőalgoritmusokat, amelyeket az AME során használ a rendszer.

Az IBM a chip energiahasználatát is optimalizálta. A gyorsítótárak a magokhoz hasonlóan agresszíven kapuzottak, vagyis a nem használt magok és a hozzájuk tartozó cache-ek az energiatakarékosság érdekében lekapcsolhatók. A Power7-ben már volt "nap" ("szundítás") mód, ekkor a tétlen magot lekapcsolta a chip, a hozzá tartozó L2 és L3 azonban továbbra is működésben maradt, ez azonban csak 10 százalékkal csökkentette az adott mag fogyasztását. Ennél mélyebb alvó állapot a "sleep", amely 35 százalékos visszaesést okozott a mag fogyasztásában. Ennek megjelent egy továbbfejlesztett verziója, amely a mag mellett a hozzá tartozó L2-t is lekapcsolja, valamint egy még takarékosabb üzemmód is bekerült a processzorba, amely a tétlen magot a hozzá tartozó L3 szegmenssel együtt üzemen kívül helyezi. Utóbbi 95 százalékos fogyasztáscsökkenést okoz a mag szintjén.

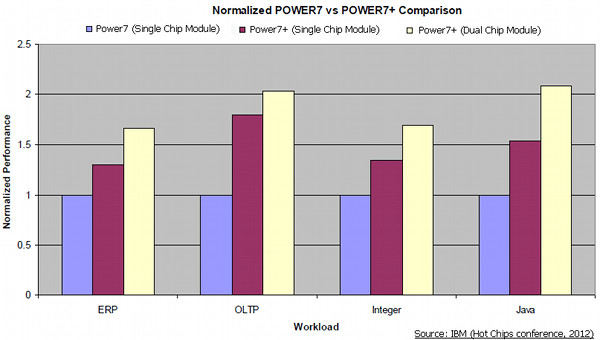

A Power7+ processzorok ugyanabba a foglalatba illeszkednek mint a Power7 lapkák, azonban a szerverek frissítéséhez szükséges az alaplapok (system board) cseréje. Ennek oka a PCI Express Gen3 támogatás (feltételezett) bevezetése mellett az lehet, hogy az új chipből készülnek majd két processzort tartalmazó multichip modulok. Ezek órajele persze jóval alacsonyabb lesz az egychipes változatoknál, a kétszer akkora magszám és a nagyobb L3 cache miatt azonban bizonyára lesznek területek, ahol jól teljesítenek, például masszívan párhuzamos jellegű feladatok esetén. Emellett indokolt lehet a használatuk olyan esetekben, amikor a felhasznált szoftver licencét nem magonként, hanem foglalatonként kell megfizetni.

Jogod van tudni: mankó kirúgáshoz, munkahelyi szkanderezéshez Ezúttal egy mindenki számára kötelező, de laza jogi különkiadással jelentkezünk. Ennyi a minimum, amit munkavállalóként illik tudnod.

Egy Power7+ szerver továbbra is 32 foglalatból állhat legfeljebb, a kétchipes modul használatával viszont ez 512 magot és 2048 szálat is jelenthet - feltéve hogy az IBM legnagyobb kiépítésű gépeiben is támogatja ezt a kiépítést. Az AIX azonban egyelőre 1024 szálnál többet nem kezel egyszerre, így a legnagyobb "single system image" telepítésekhez az operációs rendszer módosítására lehet szükség.

Még az idén befuthatnak az első gépek

A Power7+ teljesítmény szintjén komoly előrelépésnek ígérkezik a korabeli konkurenciát lesöprő elődhöz képest - az IBM által felvillantott adatok alapján a nagyobb órajel, a továbbfejlesztett magok, a titkosítási algoritmusok hardveres támogatása és egyéb újdonságok révén online tranzakciófeldolgozás alatt több mint másfélszeres a sebesség a Power7-tel összehasonlítva, a kétchipes modul pedig a foglalatszintű teljesítményt kétszeresére is növelheti például OLTP vagy Java feladatok futtatása esetén.

Bár a Power7+ az elhangzottak alapján több mint egyszerű ráncfelvarrás, az IBM szervereket nem kell teljesen áttervezni a frissítéshez, az új processzorra épülő gépek ezért akár már idén befuthatnak az első vevőkhöz. A Nagy Kék feltehetően fokozatosan mutatja majd be új rendszereit, először a kisebb, majd a közepes, végül pedig a legnagyobb kiépítésű, 32 foglalatos modelleket.