Dupláz az Oracle a SPARC T5-tel

A múlt héten zajlott a kaliforniai Cupertinóban a Hot Chips 2012 konferencia, ahol a legújabb processzorfejlesztések kerültek napirendre. Az Oracle például ismertette a következő generációs SPARC T5 részleteit. A fejlesztés receptje dióhéjban: a T4-hez képest legyen mindenből kétszer annyi!

Azonos magok

A tavalyi Hot Chipsen debütált először a nagyközönség előtt a SPARC T4, ennek továbbfejlesztéséből állt elő a SPARC T5, amelyről a Hot Chips konferencián beszéltek az Oracle szakemberei. Az előadás ugyan nem nyilvános, de a prezentáció anyagát közzétette a vállalat, amiből a legfontosabb adatok azért kiderülnek. Mire számíthatunk az első olyan processzortól, amely már teljes egészében az Oracle fennhatósága alatt készült?

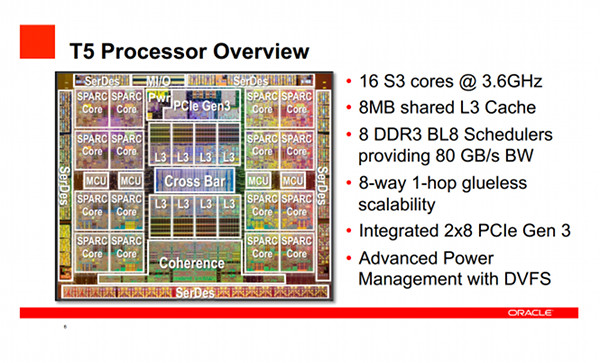

Ahogy azt már a SPARC T4 bemutatásakor és megjelenésekor is tudni lehetett, a SPARC T5 az elődjének out of order processzormagjait (S3) kapta meg, amelyek 16 fokozatú fixpontos és 11 fokozatú lebegőpontos futószalaggal rendelkeznek a magas órajel elérése érdekében. Az Oracle által nyilvánosságra hozott prezentáció szerint a TSMC által 40 helyett már 28 nanométeres csíkszélességgel gyártott SPARC T5 órajele 3,6 GHz lesz, szemben a T4 3 GHz-es induló órajelével.

Már a magasabb órajel is komoly teljesítménytöbbletet ígér a T4-hez képest, azonban a legnagyobb előrelépést nem ez hozza, hanem a magok számának megkettőzése, amelyet a gyártástechnológiai fejlesztés tett lehetővé. A SPARC T4-ben még nyolc S3 processzormag dolgozott, a T5-be ennek a duplája került, tehát tizenhatmagos chipet terveztek az Oracle mérnökei. Egy processzormag ugyanúgy legfeljebb 8 utasításszál párhuzamos futtatására alkalmas mint eddig, azaz egy T5 chip maximum 128 szálat kezel egyszerre.

A kisebb csíkszélesség miatt nem csak a magok száma nőtt, hanem a harmadszintű cache mérete is. A SPARC T4 még 4 megabájt megosztott L3 cache-sel rendelkezett, a T5-ben már 8 megabájt van - a kétszer annyi mag miatt szükséges is volt az L3 gyorsítótár megduplázása. Az S3 magokba épített cache mérete nem változott: 16 kilobájtos, négyutasan asszociatív elsőszintű adatcache-t és utasításcache-t kaptak, a másodszintű gyorsítótár pedig 128 kilobájtos és nyolcutas. Érdemes megemlíteni, hogy az L3 cache egy 8x9-es crossbar kapcsolón keresztül csatlakozik a magokhoz, amelynek sávszélessége másodpercenként 1 terabájt - ez is kétszerese a T4-ének.

A prezentáció több oldalon keresztül részletezi az S3 magokba épített kriptográfiai gyorsító képességeit, amely a gyakran használt titkosítási algoritmusok (RSA, DH, DSA, ECC, AES, DES, 3DES, Camellia, Kasumi, CRC32c, MD5, Sha-1, SHA-224, SHA-256, SHA-384, SHA-512) hardveres támogatásáért felelős - a T4-hez képest azonban ez is változatlan.

Továbbfejlesztett infrastruktúra

Az Intelhez hasonlóan az Oracle-nél is megfigyelhető egyfajta tik-tak ütem a processzorok fejlesztése terén, csak itt nem a mikroarchitektúra és a gyártástechnológia fejlődése van eltolva, hanem a magoké és az infrastruktúráé. Annak érdekében, hogy a SPARC T4 a lehető leghamarabb megjelenjen, a processzor új fejlesztésű magjait a T3 infrastruktúrájára ültették rá, ami sok tekintetben visszafogta a teljesítményt. A T5 esetében viszont a magok a változatlanok, az viszont teljesen megújul, így a magok jobban "ki tudják futni magukat".

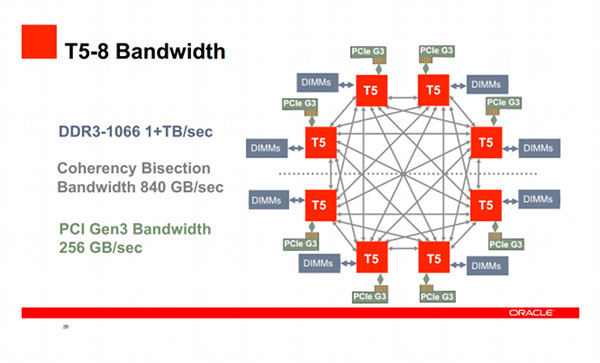

A legnagyobb továbblépést a T5 "uncore", vagyis a processzormagokon kívüli áramkörei jelentik, amelyek a jobb skálázódást hivatottak elősegíteni. A SPARC T5 már nyolc foglalatig "glueless", vagyis külön vezérlőáramkör nélkül skálázódik, a node-ok közti kommunikációt 26,5 GBps sávszélességű kommunikációs csatornák biztosítják. Kisebb konfigurációkban lehetőség van a processzorok közti összeköttetések nyalábolására is. Az architektúra lehetővé teszi két csomópont közti kommunikációt egy harmadik csomópont beiktatásával is, amennyiben a két node közötti csatornán "dugó" alakul ki. Az L3 cache-ek koherenciáját egy directory-alapú protokoll biztosítja. A cég által felvillantott ábra szerint a T5-tel közel lineáris teljesítménynövekedés érhető el, ahogy a processzorok számát növeljük.

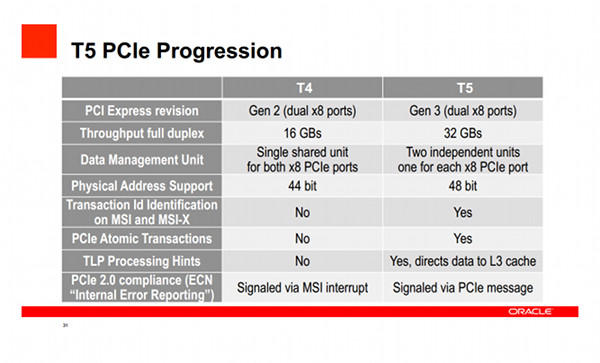

A memóriavezérlők számát is megduplázta az Oracle, kettő helyett már négy található a T5-ben, amelyek DDR3-1066 szabványú memóriamodulokat kezelnek továbbra is. Már a T4-nek is része volt két integrált PCI Express x8 vezérlő, azonban az elődben csak 2.0 verzió volt támogatva, az új processzorban viszont PCI Express Gen3 szabványt alkalmaz az Oracle, amely kétszer nagyobb sávszélességű, ráadásul mindkettő külön adatmenedzsment egységet kapott. A prezentáció ugyanakkor egy szóval sem említi az T4-ben még jelen levő integrált Ethernet-kontrollert, elképzelhető, hogy ez végül lemaradt a SPARC T5-ről - a megnövekedett PCI Express sávszélesség bőven lehetővé teszi Ethernet-vezérlők csatlakoztatását.

Introvertáltak az IT-ban: a hard skill nem elég Már nem elég zárkózott zseninek lenni, aki egyedül old meg problémákat. Az 53. kraftie adásban az introverzióról beszélgettünk.

Annak érdekében, hogy az elődjénél jóval több alkatrészből álló SPARC-T5 fogyasztása ne emelkedjen az egekig, az Oracle mérnökei változatos energiatakarékos technikákat is alkalmaztak. Az szinte természetes, hogy a chip órajele és feszültsége a terheléssel együtt csökkenthető, emellett a T5 le tudja kapcsolni vagy energiatakarékos módba tudja tenni a kommunikációs interfészeit is, amennyiben nincs rájuk szükség. Emellett órajelkapuzást is alkalmaz a SPARC-T5, vagyis a használaton kívüli egységek kikapcsolhatók.

Valószínűleg 2013-ban érkezik

A fentiekből kikövetkeztethető, hogy az Oracle által kínált legnagyobb T5-alapú gép minden valószínűség szerint a SPARC T5-8 lesz, amelyben 128 processzormag összesen 1024 programszál egyidejű futtatására képes. Amiről az Oracle egyelőre nem beszél, az a SPARC T5-re épülő gépek kereskedelmi bemutatkozása. A vállalat korábban azt ígérte, a T4 után egy-másfél évvel jöhet az új generáció, ami 2013-as megjelenést feltételez. Úgy tudjuk, az Oracle elégedett a SPARC T4 piaci teljesítményével, ezért nem is siet a T5 piacra dobásával, ami akár azt is jelentheti, 2013 őszén jönnek csak az új gépek.