A buta flash memóriának nincs jövője

A Micron szerint hamarosan lejár a "nyers" NAND flash chipek kora, ugyanis a minitarüziációval egyre kezelhetetlenebbé válnak a visszaolvasási bithibák. A probléma kezelésére a memóriagyártóknak kell alacsony szintű megoldást kitalálniuk, amely kifelé elfedi a jelenséget.

Egyre több a hiba

A Micron szerint a miniatürizációval egyre fokozódik az a kihívás, amit az adatok kiolvasása jelent. A tranzisztorok és egyéb struktúrák fizikai méreteinek évtizedek óta tartó fokozatos csökkenésével a chipekben található vezetékek, szigetelők és kapuk vastagsága mára sokszor csak néhány tucat vagy legfeljebb néhány száz atomot tesznek ki.

Ezzel folyamatosan erősödik az elektronszivárgás jelensége, amikor az elektromos töltés nem kívánatos módon áramlik, szökik, növelve a fogyasztást, fárasztva a nanométeres tartományban mozgó anyagok szerkezetét, a fémhuzalozásban elektromigráció okozhat idővel károsodást. A miniatűr vezetőkben áramló jelek ráadásul a fizikai méretek zsugorodásával egyre érzékenyebbek a külső elektromágneses behatásokra, például a kozmikus sugarakra, amelyek átfordíthatják a 0 és 1 jeleket. Ha ez észrevétlen marad, az adatkorrupciót vagy a számítógép hibázását, esetleges leállását okozhatja.

A NAND flash chipeknél a miniatürizáció problematikáját tovább súlyosbítja, hogy az apró tranzisztorstruktúrák adatokat tárolnak például az elektronok csapdába ejtésével, és a megfelelő töltés meglétének vagy hiányának visszaolvasásával. Ez egyre nehezebbé válik, ahogyan a néhány tucatnyi atomi szélességű szabályzó kapukon keresztül elszivárognak az elektronok, valamint a töltést tároló vékony réteg egyre hamarabb szennyeződik el, így a kiolvasás egyre zajosabbá, megbízhatatlanabbá válik, míg nem ellehetetlenül.

Jogod van tudni: mankó kirúgáshoz, munkahelyi szkanderezéshez Ezúttal egy mindenki számára kötelező, de laza jogi különkiadással jelentkezünk. Ennyi a minimum, amit munkavállalóként illik tudnod.

Ha a gyártók nem alkalmaznának trükköket, a miniatürizációval a NAND flash chipek cellái egyre kevesebb írási ciklust volnának képesek elviselni. A feladat nagyságát, és az ezzel járó adattömeget növeli, hogy a miniatürizációval egyre több adat kerül egységnyi szilíciumterületre. Ennek következményeként az ECC által igényelt bitek száma egyre duzzad.

Kontroller a tokon belül

A Micron szerint a helyzetet a NAND flash chipgyártóknak kell kezelniük, és a probléma jelentette komplexitást nem lehet a gazdavezérlőre, például az SSD szintjére áttolni. Emiatt a vállalat saját, integrált hibajavító menedzsment logikát mellékel, tervei szerint idővel összes NAND flash chipjéhez, amely leveszi ezt a növekvő terhet a gazdavezérlők válláról, amelyeknek a jövőben legfeljebb a meghajtó belső sínjeinek hibaellenőrzésére kell fordítaniuk a figyelmüket.

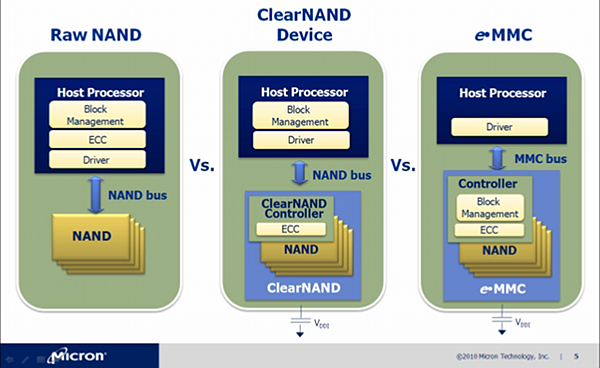

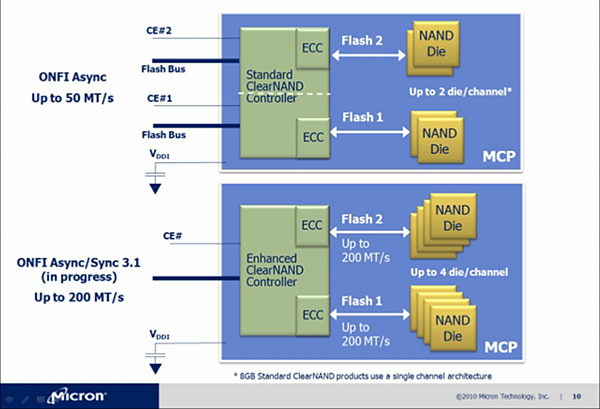

A ClearNAND lényege, hogy a NAND flash chipek számára hibajavítást és fáradáskiegyenlítés végző menedzsment logika tokon belülre került. A multichip tokozásban megbúvó ClearNAND vezérlő két csatornán összesen nyolc chipet képes vezérelni, miközben kifelé szabványos ONFI busszal kapcsolódik a gazdavezérlőre, például egy SSD-ben. A ClearNAND lényegében a csupasz NAND és a teljesen menedzselt eMMC (beágyazott MMC) közé esik, ahol utóbbinál a gazdavezérlőnek már csak a rendszerrel történő összeköttetést és az adatok címzését kell megoldania. A ClearNAND a Samsung OneNAND megoldásához hasonlít az ECC kezelése szempontjából, ugyanakkor azzal szemben már a mainstream, nyers NAND flash felváltását célozza.

A megoldás rengeteg előnnyel rendelkezik. A beágyazott menedzsmentnek köszönhetően a gazdavezérlőnek nem kell foglalkoznia, pontosan milyen típusú NAND chipekről van szó, milyen cellaszervezésűek, milyen hibajavító kódot és fáradáskiegyenlítést igényelnek, sőt az sem érdekes, milyen interfésszel rendelkeznek. Ez azt jelenti, hogy a chipgyártók a jövőben sokkal rugalmasabban fejleszthetnek a NAND chipek szintjén, mivel az nem fog zavart okozni a gazdavezérlők oldalán, azoknak nem kell foglalkozniuk a chipszintű hibajavítással.

A gazdavezérlőnek ráadásul a NAND chipek számával sem kell törődnie, a jövőben nem fogja látni ugyanis, tokon belül hány chippel van dolga. Ez nemcsak a logikai szintű vezérlést egyszerűsíti le, hanem az elektronikai implementációt is megkönnyíti és a teljesítményt is növelni tudja. A gazdavezérlő buszain (csatornáin) ugyanis így tokonként egyetlen termináció, avagy terhelés jelenik meg, a chipek számától függetlenül, nem pedig több, tipikusan kettő az adatbuszon, és négy a vezérlésen. Az elektronikai egyszerűsítéseknek köszönhetően összességében nyolcszorosára növelhető az adott huzalozással elhelyezhető tokok száma egyetlen buszon, állítja a Micron, vagy jelentősen csökkenthetők az SSD-k és más beágyazott implementációk gyártási költségei.

Eközben ráadásul a NAND chipek szintjén mért műveleti párhuzamosság és áteresztő kapacitás is drasztikusan megnövekszik, ugyanis egy tok valójában kettő párhuzamos, nagy sebességű belső buszt rejt, másodpercenként 200 megatranszferes gyorsasággal a tokon belül rétegelt NAND flash chipek felé. A nagyobb sűrűség és teljesítmény mellett a fáradáseloszlással a buszon fellépő adatforgalom is csökken, mivel a beágyazott ClearNAND vezérlő a tokon belüli adatmozgásokat képes lekezelni, ami tokonként nyolc NAND chipnél már jelentős lehet. Mivel a NAND ECC sem jelenik meg a belső buszokon, ezért ez is takarékoskodást jelent, ahogyan a ClearNAND vezérlő jelzi azt is, ha készen áll egy tok utasítások fogadására, nem kell a gazdavezérlőnek erről folyamatosan megkérdeznie, további sávszélességgel és energiával takarékoskodva.

Gyors térnyerés várható

A vállalat Enhanced ClearNAND néven kifejezetten nagy kapacitású és teljesítményű területekre kínál akár 64 gigabájt kapacitású tokokat, a külső busz ONFI 2.2 szabványú, 200 MT/s sebességű, de támogatja a kidolgozás alatt álló ONFI 3.1 generációt is, amely megduplázza ezt. A Standard ClearNAND célja, hogy a meglévő szórakoztatóelektronikai termékekbe gyorsan beilleszthető legyen, megtartva kompatibilitását a nyers NAND-dal.

A menedzselt NAND flash gyors terjedés előtt áll, ahogyan az ONFI, az Open Nand Flash Interface munkacsoport is megkezdte az ECC nélküli, úgynevezett EZ NAND interfész szabványosítását, ahol a gazdavezérlő nem akar alacsony szintű ECC-t alkalmazni. A Micron szerint a következő években a nyers NAND flash chipek rohamosan visszaszorulnak a piacról, és 2015-re szinte teljesen eltűnnek, ahogyan a gyártók jelenleg a 20 nanométeres osztályú, majd később a kisebb csíkszélességű termelésre állnak majd át.

Tekintve, hogy a Micron az Intel stratégiai partnere a NAND flash chipek gyártásában, amelyet közös leányvállalatukban végeznek, az Intel SSD-kben is várhatóan hamar megjelenik a ClearNAND, ami tovább fokozhatja az SSD-k műveleti sebességét, energiahatékonyságát, valamint a kevesebb huzalozás és egyszerűbb gazdavezérlők révén növelik költséghatékonyságukat. A Micron jelenleg tesztpéldányokat bocsát rendelkezésre ügyfeleinek, a tömegtermelés így várhatóan jövő év első felében indulhat be.