Amit a következő Itaniumról tudni lehet

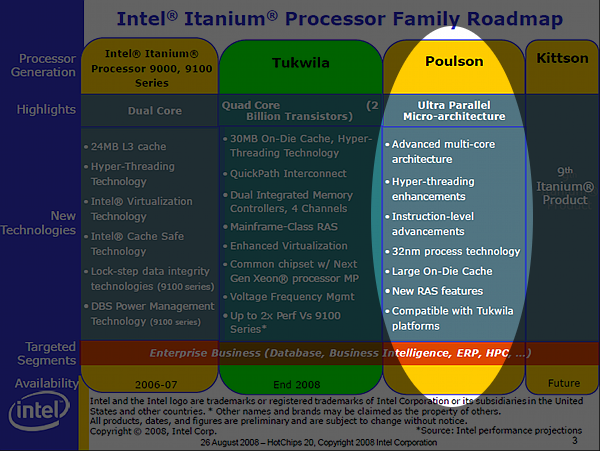

Minden eddigi nehézség és bizalomvesztés ellenére az Intel nem adta fel az Itanium vonalat, épp ellenkezőleg, a jelek szerint jelentős erőforrásokat ölt a következő generáció kifejlesztésébe. A valamikor egy-másfél éven belül debütáló Poulson ambiciózus és szokatlan próbálkozásnak tűnik, és valójában már jó ideje elkészült.

Összesen mintegy három év késést követően idén februárban mutatta be az Intel az Itanium család legújabb tagját, a Tukwilát, a HP pedig májustól tette általánosan elérhetővé a mainstream Integrity blade szerverek következő generációját. Az első Superdome 2 konfigurációkra egészen augusztusig várniuk kellett a vevőknek, ráadásul a nagyobb, 8 blade modul feletti (egy SD2 blade keretnél nagyobb) változatok továbbra sem elérhetőek, ami különösen fájdalmas ilyen hosszas késlekedést követően. A HP ígéretei szerint 2011 elején tudja telepíteni az első 32 foglalatos SD2 konfigurációkat, 64 foglalatos, vagyis 4 blade keretes összeállításról pedig egyelőre csak elméleti szinten esett szó.

Tekintve, hogy még a Tukwila sem futott fel a piacon, egyértelműen korainak tűnik az Itanium következő generációjáról beszélni. Másrészt ugyanakkor éppen az Itaniummal szembeni általános iparági hitelvesztés miatt különösen fontos, hogy a jövőben várható termékek részletezésével bizalmat tudjon építeni. Az elmúlt egy évben az Itanium elvesztette a Red Hat, a Microsoft, a Fujitsu és az Unisys támogatását is, ami jól jelzi a késés okozta károkat, amelyeket néhai partnereinek is okozott.

A következő generációs Itaniumról kiszivárgó technikai részleteket így árgus szemekkel várja a szakma, hogy abból az egész termékcsalád jövőképére következtessen. Amennyiben a Poulson kódnéven megjelenő chip nem hoz magával radikális újításokat a magok mikroarchitekturális felépítése révén, úgy könnyen kijelenthető, hogy az Intel már lassító sávba tette az Itaniumot, és csak a lehető legszükségesebb mértékű erőforrásokat bocsátja rendelkezésre a termékcsalád támogatási életciklusának lezártáig.

Amit a Poulsonról eddig tudni lehet

Ennek azonban pont az ellenkezőjéről van szó, egyelőre legalábbis úgy tűnik. A chiptervező szakma legrangosabbjának számító International Solid State Circuit Conference (ISSCC) előzetes programjában az Intel ügyesen csepegtetett néhány további kulcsfontosságú részletet a Poulsonnal kapcsolatban, amelyet eddig csak ultrapárhuzamos architektúraként jellemzett. Jövő februárban az Intel mérnökei prezentációt fognak tartani egy "32 nanométeres, 3,1 milliárd tranzisztorból felépülő, 12 utasítás szélességű Itanium" processzorról.

Az Intel már régóta hangoztatja, hogy az Itanium fejlesztéseinek felzárkóztatása érdekében a 65 nanométeres Tukwilát követően kihagyja a 45 nanométeres gyártástechnológiát, és a Poulsonnál 32 nanométerre ugrik. Ez nem jelent mást, minthogy a részben a néhai Alpha chipek tervezőiből álló fejlesztőcsapat hatalmas mozgásteret kapott ahhoz, hogy modernizálja az Itanium lényegében 2002-es mikroarchitektúráját, és a legkülönfélébb kódok futtatásával az elmúlt évtizedben felhalmozott tapasztalatok alapján továbblépjen.

Jogod van tudni: mankó kirúgáshoz, munkahelyi szkanderezéshez Ezúttal egy mindenki számára kötelező, de laza jogi különkiadással jelentkezünk. Ennyi a minimum, amit munkavállalóként illik tudnod.

A Poulson a korábban felszínre került információk alapján 8 magot fog integrálni. Ez 32 nanométeren egyáltalán nem sok, tekintve hogy a Nehalem-EX és a Power7 is nyolcmagos szilíciumok 45 nanométeres eljáráson. Ezek a magok azonban az ISSCC prezentáció címe alapján nem közönséges felépítésűek, hanem minden korábbinál szélesebbek és erőteljesebb mikroarchitektúrát sugallnak. A cikk közzétételét követően az Intel megerősítette, hogy a magokat belső körbusz kapcsolja majd össze, hasonlóan a Nehalem-EX chipnél ismert megoldáshoz. Bár a Poulson körbuszának architekturája nem ismert, elképzelhető, hogy közös alapokon nyugszik a házon belüli riváliséval.

A 12 utasítás szélességre, vagyis hogy egy processzormag torkolata órajelenként akár 12 utasítást is képes legyen kibocsátani és feldolgozásra továbbítani a végrehajtóegységek felé, sokan felkapták a fejüket. A Tukwila és a korábbi Itaniumok egy-egy magja órajelenként 6 utasítást tudnak befogadni, de ilyen széles a magas frekvenciákra tervezett Power7 is - az x86 szervervilágban a 4 utasítás szélesség uralkodott el. Az extrémnek számító szélesség egyértelművé teszi, hogy a Poulson egy radikálisan áttervezett mikroarchitektúrát hoz magával.

A 12 utasítás szélesség az Itanium utasításkészletének világában azt jelenti, hogy órajelenként négy darab csomagot tud fogadni, a csomagokban egyenként három utasítás lehet. Autós hasonlatot hozva a Poulson processzormagjai négyhengeresek lettek a Tukwila kéthengereseivel szemben. A csomagokat a compiler állítja össze, de összetétele nem tetszőleges, hanem bizonyos szabályokat követ annak érdekében, hogy ne legyen függőség és erőforrásütközés az egyes utasítások közt.

Nincs triviális magyarázat

A legnagyobb kérdés tehát az, a mérnökök hogyan oldották meg a rendkívül széles magok etetését. Ez egyáltalán nem triviális, ötletelésre készteti a processzortervezési tapasztalatokkal rendelkezőket is. Abban mindenesetre konszenzus mutatkozik, hogy nem igazán létezik olyan kód, amelyből reálisan ki lehetne nyerni ilyen fokú utasításszintű párhuzamosságot. Ha volna is, a viszonylag gyakran, integer kód esetében tipikusan 4-5 utasításonként felbukkanó elágazások felemésztik és elpazarolják az elágazások két ágán spekulatívan végrehajtó Itanium hardveres erőforrásait, amivel a legfejlettebb compiler technológia sem tud mihez kezdeni, mondta el a HWSW-nek Fischer Erik, a néhai Sun Microsystems egykori mérnöke és műszaki igazgatója.

A Tukwila magjaiban megtalálható párhuzamos feldolgozás nem szimultán (SMT), hanem nagy késleltetéssel járó eseményekkor vált szálat (SoEMT, switch-on-event multithreading), hogy áthidalja az akár több száz processzorciklust kitevő várakozási időket egy másik utasításfonál feldolgozásával. A kódok futásidejű statisztikai elemzése alapján ez a megfelelő választás az Itanium számára, ugyanis a kinyert utasításszintű párhuzamosság magas, miközben a végrehajtás gyakran áll le például a szükséges adatok hiányában.

A Poulson esetében az extra szélesség már valószínűleg szimultán párhuzamos végrehajtást igényel, aminek lekezelése azonban extra erőfeszítéseket vár a hardver részéről, hiszen versenyhelyzet alakulhat ki a szálak közt. Az IBM Power7 fejlesztői egy fele ekkora szélességű magon is a négyszeresen szimultán feldolgozás mellett döntöttek, hogy a maximális teljesítményt csikarják ki minden egyes magból. Elképzelhető, hogy az Intel-mérnökök keverik a kettőt, és kétszer kettő szálat alkalmaznak, amelyből egyszerre csak kettő lehet aktív, a másik kettő pedig a sorára vár.

Fischer reálisnak tartja a négyszeresen szimultán feldolgozást is egy ilyen széles magon, ahol implementációs szempontból a legegyszerűbb az volna, ha mindegyik szál lényegében dedikált szélességet kapna a mag erőforrásaiból. Mint mondta, minél kifinomultabb a technika, annál bonyolultabb, és annál több vezérlőlogikát kell integrálni, ami helyet és energiakeretet fogyaszt, de akár az órajelet is korlátozhatja. Abban is konszenzus látszik kialakulni, hogy egy ilyen szélességű magnál megvalósítani négyszeresen szimultán, az erőforrásokat a szálak közt dinamikusan megosztó magot bár lehetséges, a regiszterfájlok elektronikai kialakítása, adatbetöltő- és eltároló (load/store) egységek, a cache-ek kezelése elképesztően megbonyolódna.

Kevés a tranzisztor

Ennek ellentmondani látszik, hogy az Intel eközben egyértelműen magasabb órajeleket ígér a Tukwilához képest. Érdekes részlet a 3,1 milliárd tranzisztor is, amely alig másfélszer több csak a 65 nanométeres Tukwila mutatójánál, vagyis a Poulson jelentősen, ötödével kisebb lesz majd annál. 544 négyzetmilliméter. Ez egyúttal azt is jelenti, hogy a cache méretek nem emelkednek sokkal tovább a magszám duplázódása és megerősödése ellenére sem, pedig az Itanium utasításkészlet-architektúrája és szigorúan sorrendi végrehajtása igényli a nagy gyorstárakat a távoli memória késleltetésének elfedése érdekében. Nem zárható ki, hogy az Intel mérnökei a hagyományos hat tranziszoros (6T) SRAM struktúrák helyett helytakarékosabbra váltottak, bár a bőségesen rendelkezésre álló szilíciumterület ezt nem indokolná. A chip összesen 50 MB gyorstárral rendelkezik majd szilíciumon, a cache hierarchiája azonban nem ismert.

Ami bizonyos ugyanakkor, hogy a Poulson fejlesztései befejeződtek már egy jó ideje, idén márciusban már biztosan szilíciumon volt, vagyis az Intel és partnerei laborjaiban már folyik a chipek tesztelése. Erre a Nehalem-EX és Tukwila rendszerekben megtalálható memóriapuffer tesztelési hibalistáján található egy elejtett bizonyíték, hiszen a memóriapuffernek együtt kell majd működnie a Poulsonnal is, tekintve, hogy az foglalatkompatibilis frissítésként érkezik majd - várhatóan legkésőbb 2012 első negyedévében.

A foglalatkompatibilitás a Poulson gyors piaci adoptációját vetíti előre, ugyanakkor bekorlátozza a memória- és interprocesszor sávszélességek növelésének lehetőségét. A gyorsabb DIMM-eknek, valamint a gyorsított QPI linkeknek köszönhetően a Poulson foglalatonként 45 GB/s sávszélességgel éri el a lokális memóriát, míg a többi processzor felé 128 GB/s kapacitással rendelkezik az Intel közzététele szerint, amely értékek harmadával magasabbak a Tukwilla mutatóinál. A februári ISSCC-n, három hónap múlva remélhetőleg az összes fontos részlet kiderül az Itanium új generációjával kapcsolatban.