Az Intel bemutatta a Sandy Bridge generációt

A San Franciscóban a héten zajló Intel Developer Forum leginkább várt újdonsága a Sandy Bridge kódnevű mikroarchitektúra, amelyre a cég 2011-es portfóliója épül. A vállalat mindent megtett annak érdekében, hogy csillapítsa a tömegek kíváncsiságát és telt házas előadások keretében mutatta be, mi várható a cég következő nagy dobásától.

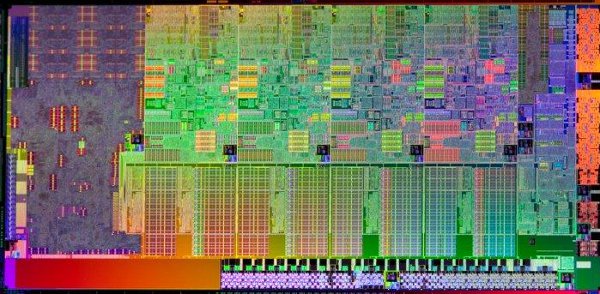

Az Intel által hivatalosan csak "második generációs Core architektúra" néven emlegetett Sandy Bridge a vállalat már tömegtermelésben alkalmazott 32 nanométeres csíkszélességű, fémalapú tranzisztorokat használó eljárásán készül. Amint az ismert, az Intel néhány éve átállt egy olyan ütemes fejlesztési stratégiára, amelynek értelmében páros években új gyártástechnológiát, páratlan években pedig új mikroarchitektúrát mutat be, és egyszerre sosem változtatja meg mindkettőt - ezzel nagyban csökkentette a kockázatát annak, hogy egy-egy projekt kicsússzon a kezei közül, a termékterv kiszámíthatóbb.

Ennek jegyében idén mutatkozott be az új, 32 nanométeres technológia, amely eljárást elsőként a Nehalem mikroarchitektúrájú Westmere chipek használják, az új mikroarchitekúra, a most bemutatkozó Sandy Bridge pedig jövőre érkezik erre a gyártástechnológiára. Ezt követően, jövő év végén, 2012 elejére, az Intel átülteti a Sandy Bridge mikroarchitektúrát az egyelőre tesztsorokon üzemelő új, 22 nanométeres csíkszélességű félvezető-technológiára, így kódneve Ivy Bridge lesz.

Skálázható

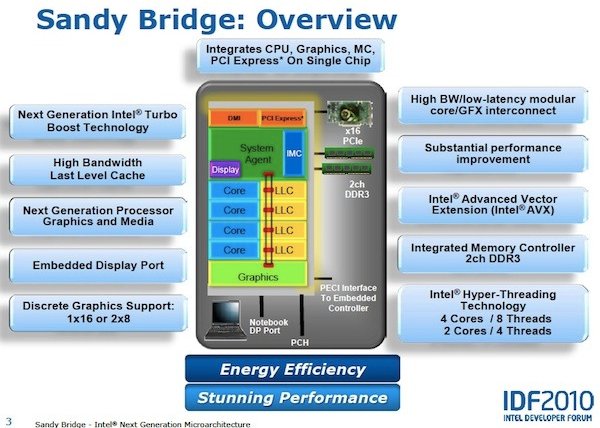

A tömegpiacra szánt asztali és mobil Sandy Bridge chipek kettő vagy négy magot tartalmaznak, amelyek a Hyper-threading révén 4 vagy 8 szálat kezelnek egyidejűleg. A magokat az utolsó szintű gyorstáron keresztül egy nagy sávszélességű, alacsony késleltetésű körbusz köti össze, csakúgy mint a Nehalem-EX esetében ugyanerre a körbuszra csatlakozik a grafikus vezérlő, valamint az ún. system agent, amely a memóriavezérlőt és a PCI Express interfészt is tartalmazza, valamint menedzseli az adatok mozgását, chipen belül, és chipek közt.

A körbusz egy órajelciklus alatt 32 bájt adatot képes továbbítani, vagyis 3 GHz-es órajelet figyelembe véve 96 gigabájt a sávszélesség állomásonként. A körbuszt úgy tervezték meg az Intel mérnökei, hogy az adattovábbítással járó legtöbb feladatot maguk az állomások képesek legyenek végrehajtani, vagyis nincs szükség központi vezérlésre, logikára. Opher Kahn, az Intel egyik vezető chiptervező mérnöke elmondta, a körbusz használatának egyik előnye,hogy könnyen lehet a chip konfigurációját módosítani, egyszerűen adhatok hozzá vagy vehetők el magok például, így gyorsan lehet különféle teljesítményű derivatívákat létrehozni például szerverek számára.

Nyolcmagos változat biztosan készül majd kétfoglalatos gépekbe (Sandy Bridge-EP), egy ilyen konfigurációt ugyanis demózott az IDF-en az Intel, de piacra csak 2011 második felében kerülhet a felvillantott termékterv szerint. A skálázódó szerverekbe szánt Sandy Bridge csak 2012-ben érkezik, legkorábban, mivel a jelenlegi Nehalem-EX chipeket jövőre váltja csak a Westmere-EX, amit a hosszabb és drágább validációs idők, valamint részben emiatt a hosszabb termék életciklusok magyaráznak.

Új magok

A Sandy Bridge chipek elektronikailag három fő részből állnak: a processzormagokból, az ugyanerre a magra integrált grafikus vezérlőből, valamint a system agentből. Ezek egymástól függetlenül működnek, eltérő lehet a feszültségük és az órajelük, a magok és a grafikus vezérlő esetében ráadásul a terhelés és a rendelkezésre álló energiakeret függvényében változhat is.

Az Intel már a tavaszi, pekingi IDF-en élőben demózott Sandy Bridge chipeket, eddig azonban nem nyilatkozott magok felépítését érintő változásokról. A Sandy Bridge az Intel állítása szerin egy teljesen új mikroarchitekúra, jelentős fejlesztésen estek át maguk a processzormagok is, amelyek felépítése erősen eltér a Nehalem/Westmere generációtól. Bob Valentine vezető tervező szerint a cél az volt, hogy energiahatékony módszereket találjanak a teljesítmény növelésére az Intel mérnökei számos új ötlettel álltak elő.

A Sandy Bridge magok teljesen új dekóder fokozatot kaptak, amely a dekódolt mikroutasításokat gyorstárazza ha jól működik az elágazásbecslés, a processzor ebből a cache-ből dolgozhat és néhány órajelre a hagyományos dekóder front-endet le lehet kapcsolni, ami jelentős energiamegtakarítással jár, mivel ezek igen komplex és magas tranzisztorszámú áramkörök a modern x86-os processzorok esetében, ami jelentős fogyasztással is jár.

Annak érdekében, hogy jól működjön az elágazásbecslés, az Intel mérnökei teljesen új logikát fejlesztettek ki, amely a korábbinál nagyobb előzmény (historikus) pufferrel rendelkezik, így elvileg még nagyobb hatékonysággal dolgozhat. Bob Valentine szerint a jó elágazásbecslés kulcsfontosságú egy processzor energiahatékonysága szempontjából, hiszen ez gondoskodik arról, hogy egy processzormag ne hajtson végre felesleges utasításokat, és ne fűtse feleslegesen az univerzumot.

Az OoO (out of order) motort, azaz az utasítások végrehajtási sorrendjét optimalizáló logikát is teljesen áttervezték az Intel mérnökei, a Nehalem/Westmere generációnál nagyobbak lettek a pufferek, vagyis az OoO motor 33 százalékkal nagyobb "utasítás ablakot" kapott, vagyis ennyivel több utasításból választhatja ki, melyik és mikor kerüljön feldolgozásra, vagyis igyekszik eltalálni, hogy mikor áll majd rendelkezésre az adat, amellyel dolgozni kell.

A cél, hogy a végrehajtóegységek folyamatosan a lehető legmagasabb kihasználtsággal üzemeljenek, ez a nagyobb ablakkal és kifinomultabb ütemező logikával valószínűleg tovább javul a Sandy Bridge processzorokban, így órajelenként átlagosan több utasítást hajtanak végre, mint a jelenlegi Intel processzorok. Kérdéses ugyanakkor, mindez mennyi extra tranzisztorba és fogyasztásba került, és hogyan befolyásolja az elérhető órajeleket.

Új vektoros utasítások: AVX

A Sandy Bridge új utasításkészlettel is gazdagodik, a 256 bites AVX (Advanced Vector Extension) SSE- kiterjesztés olyan területeken növeli a teljesítményt mint a médiafeldolgozás (audio- és videotömörítés és konvertálás), képfeldolgozás, 3D grafika, illetve akár tudományos szimulációk vagyis olyan esetekben, amikor sok lebegőpontos számításra van szükség. Bob Valentine elmondása szerint a Sandy Bridge egy órajel alatt ideális esetben három 256 bites AVX utasítás végrehajtására képes.

Az AVX utasításkészletet (vagy legalábbis egy részét) az AMD is használni tervezi a Bulldozerben, vagyis teljes iparági támogatottság alakult ki mögötte, amely egyben azt is jelenti, a szoftverfejlesztők is valószínűleg igyekeznek mihamarabb erre optimalizálni. Az Intel azt ígéri, hogy az AVX révén a meglévő SSE-kódok is gyorsíthatóak, a kód portolása 256 bites feldolgozásra pedig egyszerű feladat lesz.

Az AVX bevezetése a mikroarchitektúrát is érinti, a 16 XMM regiszter mindegyikét 256 bitesre növelték az Intel mérnökei és a lebegőpontos adatutakat is kiszélesítették ezeket használja az AVX. Jelentős teljesítménynövelő újdonság, hogy a Sandy Bridge magjai órajelenként két LOAD és két STORE utasítást tudnak végrehajtani erre a fejlesztésre is részben az AVX bevezetésre miatt volt szükség. A mobil és asztali Sandy Bridge lapkák kétcsatornás DDR3 memóriavezérlőt integrálnak az Intel szerint ennél több csatornás megoldás gazdaságtalan lenne.

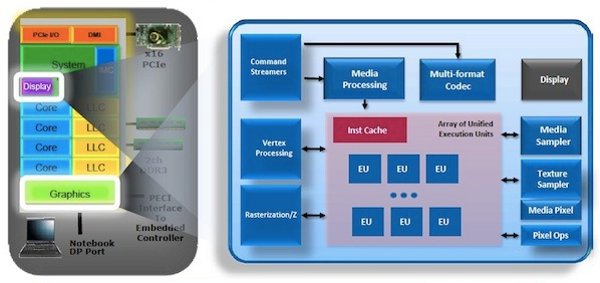

Kétszer gyorsabb integrált grafikus vezérlő

A grafikus vezérlő a jelenlegi generációs Westmere chipekben is integrált, azonban nem a szilícium, hanem a tok szintjén. Ez a gyakorlatban azt jelenti, hogy a Core i3/i5/i7 processzorok egy tokban két lapkát tartalmaznak, a 32 nanométeres processzort és a 45 nanométeres grafikus vezérlőt, amely egyébkén a memóriavezérlőt is tartalmazza. A Sandy Bridge esetében a grafikus vezérlő, és vele együtt a memóriavezérlő is ismét már a chipre kerül, így szintén 32 nanométeres csíkszélességgel készül. A 6 shader feldolgozóegységet felvonultató grafikus mag külön 3D gyorsítót és médiagyorsítót tartalmaz, utóbbi elég nagy teljesítményű akár egy 3D Blu-ray videó lejátszásához és a legtöbb ismert kodekhez hardveres támogatást biztosít, hangzott el a rendezvényen. A Sandy Bridge processzorok termékmodelltől függően nulla, egy vagy kettő grafikus maggal rendelkezhetnek.

Érdekesség, hogy a grafikus vezérlő a CPU magokkal közös cache-en osztozik, ami rendkívüli mértékben felgyorsítja a köztük zajló kommunikációt. A megoldás nem csak a teljesítményre van jó hatással, hanem a fogyasztásra is, ugyanis így ritkábban van szükség a memóriához fordulni, ami lassú és energiaigényes, továbbá a PCI Express vagy DMI sínek fogyasztása is eltűnik, nem beszélve a költségükről.

Arra azért senki se számítson, hogy csúcskategóriás játékokat futtathat a Sandy Bridge integrált videovezérlőjén, de az Intelnek nem is volt célja, hogy ezeker az igényeket kiszolgálja, mondta el egy beszélgetés során Thomas Piazza, az Intel grafikus fejlesztéseiért felelős vezető. A mainstream, nem túl gépigényes játékokhoz azonban elegendő lehet az új videomag, ami az elejtett megjegyzések szerint a Westmere-be épített HD Graphics vezérlőnél kétszer gyorsabb - emellett továbbra is használható PCI Express felületű külső videovezérlő is, 1x16 vagy 2x8 konfigurációban.

Az Intel mérnökei továbbfejlesztették a Turbo Boost technológiát is, amely lehetővé teszi, hogy egyes processzormagok, vagy a grafikus magok a névleges órajel felett üzemeljenek, ha a chip nem meríti ki a fogyasztási keretet. A Sandy Bridge esetében akár az összes magot fel lehet turbózni és néhány másodpercre akár a megadott fogyasztási keretet is túllépheti a chip. A másik fontos fejlesztés, hogy már a grafikus vezérlő is részt vesz ebben a játékban és az órajele is dinamikusan változhat a terhelés, valamint a CPU-magok terhelésének függvényében. Az Intel szerint ritka, hogy az alkalmazások egyszerre terheljék a processzort és a grafikus vezérlőt, vagyis elég nagy a mozgástér a rendelkezésre álló fogyasztási keret elosztására.

2011 elején

Az első Sandy Bridge chipek termelése még idén beindul, de csak a PC-gyártók készleteinek feltöltésére. Amiről az Intel nem beszél, az az, hogy pontosan milyen változatokban lesz kapható a Sandy Bridge, mekkorák lesznek az órajelek, a cache méretek, vagyis azok a paraméterek, amelyek alapján pontosabban becsülni lehetne a várható teljesítményszinteket. A konkrét termékbejelentésre minden bizonnyal a januári CES-en kerül majd sor, legalábbis ami a mobil és asztali változatokat illeti. A szerverekbe szánt változatok pedig az év későbbi részében érkeznek meg, mivel az Intel jelenlegi, friss szerverkínálata iránt így is rendkívül erős a kereslet, így az új alaplapokat igénylő platform bevezetése előtt hagyják kifutni a jelenlegieket.