Bemutatkozik az AMD Hammer

Cikkünkben régi adósságunkat törlesztve a K8 architektúra leglényegesebb jellemzőit és újdonságait mutatjuk be. Célunk, hogy az olvasónak támpontokat adjunk a rövidesen az asztali számítógépekbe is beköltöző új processzorok megítéléséhez.

Fred Weber és gyermeke, a Hammer

(Fotó: Paul Sakuma, AP)

A vállalat azonban rendíthetetlenül folytatta a fejlesztést: 2000-ben elkészült az akkor x86-64, ma AMD64 néven ismert kibővített architektúra specifikációjával, miközben gőzerővel dolgozott az azzal kompatibilis nyolcadik generációs, Hammer (K8) kódnéven ismert processzor tervezésén. A 64 bites mikroprocesszor az eredeti tervek szerint 2001 végén jelent volna meg, azonban többszöri halasztást követően a premier az idei évre tolódott. Ma már kapható a munkaállomásokba és szerverekbe szánt Opteron, míg küszöbön áll az asztali számítógépek számára tervezett Athlon 64 megjelenése.

Cikkünkben régi adósságunkat törlesztve a K8 architektúra leglényegesebb jellemzőit és újdonságait mutatjuk be. Célunk, hogy az olvasónak támpontokat adjunk a rövidesen az asztali számítógépekbe is beköltöző új processzorok megítéléséhez. Így számos fontos területre nem térünk ki, például nem szólunk a több Opteron processzort tartalmazó rendszerekről vagy az AMD64 utasításkészlet-architektúra előtt álló kihívásokról sem.

[oldal:Az AMD64 ISA]

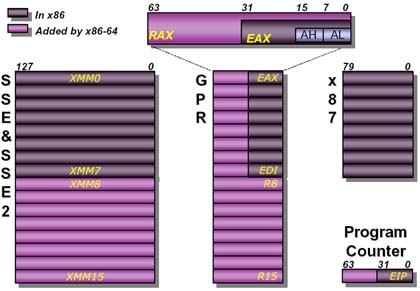

Az AMD nyolcadik generációs architektúrájának egyik leglényegesebb újdonsága az x86-os utasításkészlet kibővítése és továbbfejlesztése. Hasonló kaliberű változatásra a nemrégiben negyedszázados születésnapját ünneplő utasításkészlet-architektúra (ISA) történetében legutóbb 18 évvel ezelőtt került sor a 32 bites Intel 386 bevezetésével. A korábban x86-64, újabban AMD64 néven ismert ISA -- amint azt a neve is sugallja -- egy lépéssel továbbmegy és az architektúrát 64 bitesre bővíti. Ez a gyakorlatban azt jelenti, hogy az AMD64 első implementációjának számító K8 általános célú regisztereinek szélessége megkétszereződött, azaz a processzor képes 64 bit hosszúságú egész számokkal (így memóriacímekkel) dolgozni. A további regiszterek hossza nem változott, így az MMX regiszterek továbbra is 64 bitesek, az SSE regiszterek továbbra is 128 bitesek, míg a lebegőpontos regiszterek továbbra is 80 bitesek.A 64 bites adatoknak köszönhetően a processzorral megcímezhető memória mérete elméletben a jelenlegi 32 bites processzorok felső határát kijelölő 232 byte (4 Gbyte) helyett 264 byte-ra, azaz 18 millió terabyte-ra növekszik. A gyakorlatban a megcímezhető memória mérete ennél kisebb: a K8 48 bites virtuális címzésre (körülbelül 282 terabyte) és 40 bites fizikai címzésre (1 terabyte) képes. A 4 gigabyte-nál nagyobb tárterület számos alkalmazási területen tehet jó szolgálatot. Ezek közé tartoznak a teljesség igénye nélkül a hatalmas méretű adatbázisok, a grafikus alkalmazások, a tervezőprogramok, a 3D-s animációs alkalmazások vagy a szimulációs programok, míg a 64 bit hosszúságú egész számokkal való műveletvégzés a tudományos alkalmazások lehetőségeit bővíti.

A 64 bites regiszterek bevezetésén túl az AMD64 egyben igyekszik orvosolni az x86 egyik leggyakrabban kritizált hendikepjét: a programozó rendelkezésére álló regiszterek alacsony számát. Tulajdonképpen a 8086 huszonöt évvel ezelőtti bevezetése óta 8 darab általános célú regiszterrel gazdálkodhattak az x86-os programok írói, miközben számos más ISA jóval nagyobb mozgásteret enged: a PowerPC ISA például 32 darab architekturális regisztert tartalmaz. Márpedig minél több az adatok átmeneti tárolására szolgáló regiszter, annál több a végrehajtó egységek által közvetlenül elérhető adat, a processzornak annál ritkábban kell a memóriaműveletekre várni, míg a programozók és a fordítóprogramok annál nagyobb mozgástérrel rendelkeznek a kód függőségeket elkerülő optimalizálására.

Az AMD64 architektúra megkétszerezi az általános célú regiszterek és az SSE/SSE2 utasítások által használt XMM regiszterek számát. Amint az az ábrán látható, a nyolc x86-os általános célú regiszter elnevezése egy R betűvel bővült (AX 16 bit, EAX 32 bit, RAX 64 bit), míg a nyolc új regisztert számokkal jelölik (R8, R9...R15). Hasonlóan bővült az XMM regiszterek sora is (XMM8, XMM9...XMM15). Változatlan maradt ugyanakkor a veremszerűen elrendezett nyolc regiszterből álló lebegőpontos regiszterfájl. Ennek az lehet az oka, hogy az AMD -- minthogy ez nyújtja a legnagyobb teljesítményt -- maga is az SSE/SSE2 vektorutasítások használatát javasolja a lebegőpontos műveletek elvégzésére.

[oldal:Működési módok]

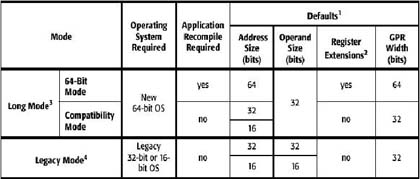

Az AMD64 előző oldalon áttekintett újításai azonban nem minden esetben használhatóak ki, a processzor ugyanis a már meglévő x86-os programokkal való kompatibilitás megőrzése érdekében többféle működési módot ismer. Az egyes módok jellemzőit az alábbi táblázat foglalja össze:

Amint az látható, legacy módban a processzor éppen úgy viselkedik, mint egy hagyományos 32 bites processzor; ekkor nem érhetőek el az AMD64 által bevezetett bővítmények, azonban támogatott a kompatibilitás biztosítása érdekében megkívánt valós, védett és virtuális 8086-os mód. A processzor ebben a módban üzemel a jelenleg hozzáférhető (16 és) 32 bites operációs rendszerek futtatása során.

Az AMD64 architektúrát támogató 64 bites operációs rendszerek alatt nyílik meg a lehetőség a sokkal izgalmasabb long mód előtt, amelynek két részmódja van. 64 bites módban felhasználható az AMD64 minden kiterjesztése, így a 64 bites általános célú regiszterek, a nyolc új általános célú és XMM regiszter, valamint a 64 bites utasításpointer. Ez tehát azt jelenti, hogy az AMD64-re írt (vagy újrafordított) programok minden esetben ebben a módban futnak. Ebben a módban az x86-os szegmentált tárcímzés helyett egységesen címezhető a 48 bites virtuális memória.

Ezzel szemben a compatibility módban problémamentesen futtathatóak a már meglévő 16 és 32 bites alkalmazások 64 bites operációs rendszer használata mellett is. Ezek ugyanakkor értelemszerűen nem férnek hozzá az AMD64-kiterjesztésekhez, és csupán a virtuális tárterület első 4 Gbyte-ját érhetik el. Long mode-ban tehát egyaránt futtatható 32 és 64 bites program az ISA-t támogató 64 bites operációs rendszerek alatt.

Az AMD64-bővítmények az utasítások elé írandó REX (register extensions) prefixumok segítségével érhetőek el. Az egy byte hosszúságú prefixumok egyben azt is jelentik, hogy a 64 bitre fordított programok mérete valamelyest megnő a 32 bites változatokhoz képest. Az AMD számításai szerint a kód -- elsősorban a prefixumoknak köszönhetően -- átlagosan kevesebb, mint 10 százalékkal lesz hosszabb átfordítás után.

[oldal:K8 inside]

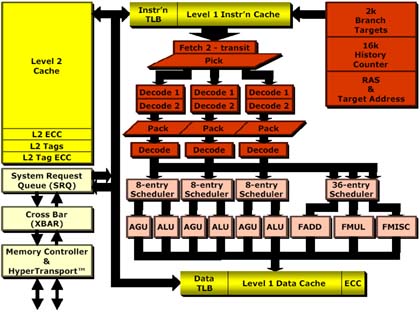

Ha annak idején a K7-ről is írtunk volna ehhez hasonló, az architektúrát több-kevesebb részletességgel bemutató cikket, abban a K8 belső felépítését sematikusan ábrázoló alábbi illusztrációhoz nagyon hasonló ábra szerepelt volna. Ez nem véletlen. Az AMD mérnökei ugyanis az "ami (jól) működik, azt ne bolygassuk" elv mentén jártak el, és nem terveztek egy teljesen új architektúrát például több végrehajtóegységgel, hanem hol kisebb, hol látványosabb módosításokat hajtottak végre a kiforrott Athlon magon. Így a K8 is egy kilenc végrehajtó egységgel rendelkező, szuperskalár, teljesen futószalagelvű processzor, amely azonban az AMD64 ISA támogatásán túlmenően olyan újdonságokat vonultat fel, mint az integrált memória- és HyperTransport-vezérlő, az SSE2 utasításkészlet támogatása, hosszabb futószalag a magasabba működési frekvencia érdekében, megnövelt méretű címfordítási pufferek és javított hatékonyságú elágazásbecslés.

A K8 az első olyan x86-os processzor, amely integrálva tartalmazza a hagyományos északi híd egyik legfontosabb funkcióját, a memóriavezérlőt. Az integrált, magsebességen működő vezérlő legkézzelfoghatóbb előnye a memória-hozzáférés késleltetésének jelentős csökkenése: az AMD adatai szerint a késleltetés közel fele az Athlon XP esetében elért legkedvezőbb mutatóknak. És minthogy a memóriavezérlő a processzor órajelével üzemel, a működési frekvencia növelésével a késleltetés tovább csökken. A megoldás további hozadéka, hogy többprocesszoros környezetben a memória-sávszélesség egyenes arányban nő a processzorok számával, hiszen azok nem egy közös memóriabuszon osztoznak. A 144 bites (128 bit + 16 ECC paritásbit) DDR333 vezérlővel rendelkező Opteron elméleti maximális sávszélessége 5,3 Gbyte/sec, amely egy négyprocesszoros rendszerben 21,3 Gbyte/sec-ra nő.

A K8 az AMD által kifejlesztett nagysebességű kétirányú kapcsolatot lehetővé tevő pont-pont interfészt, a HyperTransportot használja az alaplapi vezérlőlapkákkal folytatott -- illetve többprocesszoros környezetben a processzorok közötti -- kommunikációra. A szerverekbe és munkaállomásokba szánt Opteron három 16 bites HT interfésszel, míg az asztali számítógépekbe szánt Athlon 64 egy 16 bites HT interfésszel rendelkezik. Az 16 bites interfész mindkét irányban 3,2 Gbyte/sec maximális sávszélességet biztosít. Érdekességképpen érdemes megemlíteni, hogy az integrált memóriavezérlő és a HT kapcsolat meglétének van egy terminológiai hozadéka is: a K8 architektúrára épülő processzorok esetében nem beszélhetünk hagyományos értelemben vett rendszerbuszról (FSB), amikor a processzort és az alaplapi vezérlőlapkát összekötő kapcsolatra hivatkozunk, hiszen az FSB részben a processzormagra került.

(Forrás: Real World Technologies)

A K8 a magasabb működési frekvencia elérése érdekében két fokozattal hosszabb futószalagot tartalmaz, mint a K7, így integer futószalagja 12, míg lebegőpontos futószalagja 17 fokozatból áll. Az új architektúra az utasítások végrehajtását (a behívást és dekódolást) több részfeladatra bontja le, mint a K7, így a részfeladatokat elvégző áramköri elemek bonyolultsága csökkenthető, ami pedig lehetőséget ad az órajel növelésére. Az újonnan bevezetett második behívó fokozat (Fetch 2) feladata például nem több, mint hogy az adatokat az utasításcache-ből az 1 és 15 byte közötti hosszúságú x86-os utasítások határait azonosító egységhez továbbítsa.

Ezen túlmenően a K8 megnövelt méretű és csökkentett késleltetésű exkluzív és spekulatív címfordítási puffereket (Translation Look-aside Buffer, TLB) kapott. E pufferekben cache-elődnek el a címfordítás felgyorsítása végett a tényleges memóriacím kiszámításához szükséges adatok. Minél nagyobb a TLB, annál több adat és utasítás címei állnak azonnal rendelkezésre. A K8-ban a teljesen asszociatív elsőszintű utasításcím-fordítási puffer befogadó képességét 24 bejegyzésről 40-re növelték, a 4-utas csoportasszociatív másodszintű utasításcím-fordítási és adatcím-fordítási pufferek méretét pedig megduplázták, mégpedig 512 bejegyzésre.

[oldal:Elágazó ösvények]

A K8 fontos architekturális újítása az elágazáskezelő logika továbbfejlesztése. A mikroprocesszorok tervezői számára a kezdetektől fogva komoly kihívást jelentett, hogy a programokban természetüknél fogva számos elágazás található. Különféle statisztikai adatok szerint egy általános célú programkód minden 4-6. utasítása elágazási utasítás. Ezek végrehajtása a régebbi processzorokban jelentős teljesítményveszteséggel járt. A feltétlen elágazások (GO TO) esetében ugyanis ki kell számítani az elágazási címet, azaz azt a címet, ahol a program futása folytatódik, míg a feltételes elágazások (IF-THEN-ELSE) esetében a feltételt is ki kell értékelni, mielőtt eldönthető, hol folytatódik a program futása. A korai processzorok e műveletek több ciklust igénylő elvégzése alatt nem kezdtek újabb utasítás(ok) feldolgozásába, ami értelemszerűen jelentősen csökkentette a feldolgozási teljesítményt.A modern szuperskalár processzorokban a hosszú futószalagok és a többszörös utasításkibocsátás miatt még fájdalmasabb teljesítménycsökkenéssel kell számolni. Nem véletlen, hogy e processzorok igen fejlett és egyre összetettebb elágazáskezelő megoldásokat alkalmaznak a probléma megoldására. A leghatékonyabb és egyben legelterjedtebb eljárás a feltételes elágazások spekulatív végrehajtása. Ennek során a processzor megbecsüli a feltétel eredményét és a becslésnek megfelelő ágon folytatja a program végrehajtását. Számos mikroprocesszor mellett ezt a módszert alkalmazza az AMD K7 és K8, valamint az Intel Pentium 4 is. Érdekességképpen érdemes szót ejteti a többszörös elágaztatásról, melynek lényege, hogy a processzor a feltétel lehetséges eredményeinek megfelelő összes ágat végrehajtja, majd a feltétel kimenetelének rendelkezésre állását követően kizárólag a helyes ág eredményeit tartja meg. Ilyen megoldást használ az Intel Itanium.

Spekulatív végrehajtás mellett rendkívül fontos, hogy az elágazásbecslés a lehető legpontosabb legyen. Helytelen becslés esetén ugyanis a processzornak törölnie kell a spekulatív módon végrehajtott utasításokat, vissza kell állítania az elágazás előtti állapotot és a helyes ágon kell megkezdenie a végrehajtást. A téves becslés az olyan mély futószalaggal rendelkező processzorok esetében, mint amilyen a K8, számos ciklusnyi kiesést eredményez. A Hammer a legjobb esetben, azaz amikor a helyes ág megtalálható az elsőszintű gyorsítótárban, 11 ciklust veszít helytelen becslés esetén. Nem véletlen, hogy az AMD mérnökei kiemelt hangsúlyt fektettek az új architektúra elágazásbecslő pontosságának javítására.

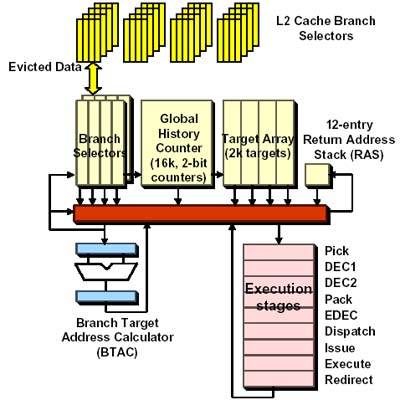

A K8 már az utasításbehívás során észleli az elágazási utasításokat, és továbbítja azokat az elágazásbecslő egységnek (BPU, Branch Prediction Unit). A BPU feladata az elágazási címek kiszámítása (BTAC), az egyes elágazási utasításokhoz tartozó címek tárolása (Branch Target Array) és az elágazások kimenetelének megbecslése az elágazástörténeti tábla (Global History Counter) alapján. A K8 esetében az elágazástörténeti tábla mérete négyszeresére növekedett a K7-hez képest: 16384 bejegyzést tartalmazhat 4096 helyett. E táblában a már végrehajtott elágazási utasítások kimenetelét jegyzi fel a processzor. A K8 két bitet használ a feltételek históriájának vezetésére: e két bit értéke határozza meg az elágazás sorsát (a két bit lehetséges értékei: határozott elágazás, gyenge elágazás, gyenge soros folytatás, határozott soros folytatás). Az AMD adatai szerint a korai elágazásészlelésnek és megnövelt méretű elágazástörténeti táblának köszönhetően a becslés pontossága 5-10 százalékkal javul az Athlonhoz képest.

[oldal:K8 outside]

Az AMD64 architektúra egyelőre két processzorban öltött testet: a többprocesszoros szerverekbe és munkaállomásokba szánt AMD Opteronban és az asztali számítógépekbe szánt AMD Athlon 64-ben. Az Opteron idén április 22. óta megvásárolható, míg az Athlon 64 megjelenése a többször módosított útitervek szerint szeptemberben esedékes. Jelenleg mindkét modellt 0,13 mikronos SOI (silicon on insulator) technológiával gyártja az AMD. A SOI alkalmazásával gyorsítható a tranzisztorok kapcsolási sebessége és csökkenthetőek a chipek disszipációs értékei.

A maximálisan nyolcprocesszoros rendszerekben használható Opteron kétcsatornás 144 bites memóriavezérlővel (128 bit + 16 ECC bit), 128 kbyte elsőszintű (64 kbyte utasítás- és 64 kbyte adatcache) és 1 Mbyte, magsebességgel működő másodszintű gyorsítótárral rendelkezik, és legfeljebb 8 Gbyte DDR200/266/333 szabványú memóriát támogat processzoronként. Az Opteron három 16 bites HyperTransport interfésszel (6,4 Gbyte/sec/interfész) rendelkezik a multiprocesszoros támogatás miatt. A processzor 940 tűs kerámia mPGA tokozásban kerül forgalomba, körülbelül 105,9 millió tranzisztort tartalmaz egy 193 mm2 méretű magon, és 1,55 Volt tápfeszültséget igényel.

Az Opteron processzoros rendszerek háromféle változatban kerülnek forgalomba: a 100-as sorozat az egyprocesszoros, a 200-as sorozat a kétprocesszoros, míg a 800-as sorozat a négy- vagy többprocesszoros rendszerekbe szánt modelleket jelöli. Az egyes lapkák ezen túlmenően egy 40-es számot is kapnak: így például a 140 az egyprocesszoros rendszerekbe szánt legalacsonyabb órajelű modellt jelöli. A harmadik szám pedig e processzorok közötti teljesítménykülönbségre utal. A 142 például egy ennél gyorsabb, míg a 144 egy még gyorsabb modell jele. Ez azt jelenti, hogy az 1,4 GHz-es, kétprocesszoros rendszerekbe szánt Opteron jele 240, az 1,6 GHz-en futó hasonló változaté pedig 242 lesz, és így tovább. Amint újabb modellek kerülnek piacra, a vállalat vélhetően növeli a modellszámot x50-re, x60-ra stb.

Az egyprocesszoros asztali számítógépekbe szánt Athlon 64 pedig egy 72 bites DDR memóriavezérlővel rendelkezik, és maximálisan 4 Gbyte DDR200/266/333, esetleg DDR400 szabványnak megfelelő memóriát támogat. A processzor egyetlen 16 bites HyperTransport interfészt, 128 kbyte elsőszintű (64 kbyte utasítás- és 64 kbyte adatcache), míg -- legalábbis kezdetben -- 1 Mbyte másodszintű gyorsítótárat tartalmaz, és 754 tűs mPGA tokozásban kerül forgalomba. A processzorok teljesítményét az Athlon XP sorozatnál bevezetett modellszámozási módszer alapján jelölik majd. Egy a HP-tól nemrégiben kiszivárgott dokumentum szerint a 3100+ jelölésű, 1 Mbyte másodszintű gyorsítótárral rendelkező Athlon 64 processzor órajele 1,8 GHz lesz.

A felhasználók számára jó hír, hogy mind az Opteron, mind az Athlon 64 processzorok -- az Intel Pentium 4 esetében is alkalmazott -- hővezető fémsapkával ellátott tokozást kapnak, ami megfelelő védelmet biztosít a processzormag számára, megóvva azt az Athlonok és Duronok magja felett Damoklész kardjaként lebegő lesarkazás veszélyétől.

Ajánlott irodalom: