Intel és AMD: a jövő tranzisztorai

A héten zajlik Japánban a félvezetőgyártás legújabb fejleményei bemutatásának fórumot adó, évente megrendezésre kerülő VLSI Symposium konferencia. A rendezvényen számos iparági nagyágyú ismertette új fejlesztéseit. Cikkünkben az Intel és az AMD legújabb eredményeit mutatjuk be röviden.

A kutatók jó ideje igyekeznek olyan tranzisztorstruktúrákat létrehozni, amelyek alacsonyabb fogyasztás mellett képesek megbízhatóan működni. Az alacsony fogyasztás elérésének egyik kulcsfontosságú eleme a szivágási áram csökkentése. A szivárgás (szivárgási áram) a félvezetők lezárt átmenetén létrejövő jelenség, amely szabad elektronok és lyukak kombinációjából származik és nanoamper nagyságrendű. Ez a jelenség az egyik legnagyobb probléma a nagyteljesítményű processzorok tervezésében. A processzorok fogyasztása a működési feszültség csökkentésével mérsékelhető, azonban ahogy a tranzisztorok nyitófeszültsége (az a feszültségszint, amikor a tranzisztor "bekapcsol") tart a 0 Volthoz, a szivárgási áram nő és egyre nagyobb problémát okoz.

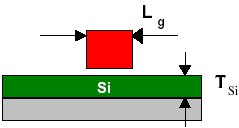

Planáris tranzisztor

A szivárgási áram elsősorban azért jelent komoly problémát a növekvő komplexitású processzorokban, mert a chipben található összes tranzisztorban jelen van, még azokban is, amelyek az adott időpillanatban nem aktívak -- az aktív tranzisztorok száma adott pillanatban általában 10 százalék körüli. Ezért a szivárgás rendkívüli módon növeli a disszipációt, ráadásul az áramkör bonyolultságával, a tranzisztorszám növekedésével együtt növekszik. A szivárgási áram -- mivel a tápfeszültséggel fordítottan arányos -- egy kisebb csíkszélességű gyártástechnológia bevezetésénél akár két-háromszorosára is nőhet, ezért a jelenség megnyugtató kezelése a kutatók elsőszámú feladata.

Az Intel által tavaly bejelentett planáris (réteges felépítésű) TeraHertz tranzisztor is alacsonyabb szivárgási mutatókkal bír a jelenleg elterjedteknél, de a vállalatok az utóbbi időben egyre gyakrabban alkalmaznak nem-planáris technológiákat, mint amilyen az IBM által kifejlesztett Double Gate (FinFET). Az Intel azonban úgy véli, hogy a riválisok által alkalmazni kívánt tranzisztorok előállítása költséges, teljesítményük pedig nem igazolja a várakozásokat. A cég kutatói ezért egy háromkapus nem-planáris tranzisztort fejlesztettek ki, amely elmondásuk szerint a jelenlegi gyártástechnológiával is előállítható, míg a hasonló kapuhosszúságú planáris tranzisztorokénál 20%-kal jobb teljesítményt nyújt.

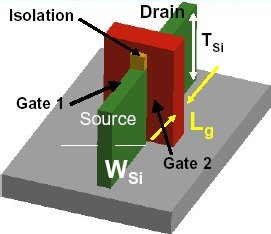

Double-gate (FinFET) tranzisztor

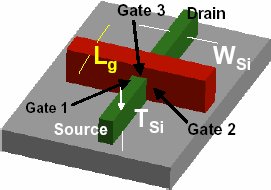

A tri-gate tranzisztor alkotóelemei nem rétegszerűen helyezkednek el, hanem három dimenziós struktúrát alkotnak. A double gate tranzisztorhoz hasonlóan a forrás (source) és a nyelő (drain) a szubsztrátból kiemelkedő vezetéken kap helyet, amelyet azonban három oldalán érintve (tri-gate) satuszerűen fog közre a kapuelektróda (gate). Az Intel először a 2002 őszén rendezett ISSDM (International Solid-State Devices and Materials) konferencián jelentette be tri-gate tranzisztorának elkészültét. Bár már a tavaly ősszel bemutatott megoldás is rekordteljesítményt és egyedülállóan alacsony szivárgási mutatókat tudott felmutatni, a vállalat azóta folyamatosan tökéletesítette az elgondolást, amelynek eredményeképp a kapuhosszt 60 nanométerről 30 nanométerre tudta csökkenteni.

Tri-gate tranzisztor

[oldal:A tri-gate jelentőségéről]

Ken Davis, az Intel gyártástechnológiai fejlesztési részlegének vezető kutatója a telefonos konferencia keretében tartott előadásában kiemelte, hogy a tri-gate tranzisztorok életciklusa a kutatási szakaszból immár a fejlesztési szakaszba lépett. Az Intel kutatója elmondta, hogy a következő generációs gyártástechnológiák és megoldások esetében az ötletek először az útkeresési fázison mennek keresztül, ekkor a vállalat szakemberei a létező összes olyan alternatívát megvizsgálják, amely szóba jöhet az új generációs fejlesztéseknél. Davis szerint ebben az esetben az Intel mind a planáris, mind a double gate (FinFET), mind a tri-gate tranzisztorokat vizsgálta és végül legutóbbiak mellett döntött. Ez a döntés egyben azt jelenti, hogy minden bizonnyal tri-gate tranzisztorok képezik a vállalat 2007-ben bevezetendő, P1266 kódnevű, 45 nanométeres csíkszélességű gyártástechnológiájának alapját.

Ken Davis rámutatott, hogy a planáris tranzisztorok esetében a kapuhossz közel háromszor nagyobb, mint a szilíciumcsatorna vastagsága, utóbbi azonban nem csökkenthető tetszőleges mértékben. A double-gate (FinFET) tranzisztorok esetében a kapu alatt található szigetelőréteg mérete a kapuhossz kétharmada, ezért ezbben az esetben a litográfiai eszközöknek egy generációval meg kell előznie korukat, ugyanis a félvezető áramkörök a kapuhossznál lényegesen kisebb elemeket is tartalmaznak. A tri-gate tranziszotoroknál azonban a szilíciumcsatorna vastagsága gyakorlatilag megegyezik a kapuhosszal.

Davis szerint az Intel kísérletei azt mutatják, hogy a tri-gate tranzisztorok alkalmazásával a kapcsolási sebesség jelentősen növekszik, a szivárgási áram pedig a hasonló méretű sík tranzisztoroknál akár százszorta kisebb lehet. A kísérletek alapján elmondható, hogy a tri-gate tranzisztorok alkalmazásával a szivárgási áram az AMD és az IBM által is alkalmazni kívánt, SOI technológiával előállított fully-depleted (rendkívül vékony szilíciumfilm választja el a szigetelőréteget és a csatornát) tranzisztorokat magában foglaló technológiához mérhető.

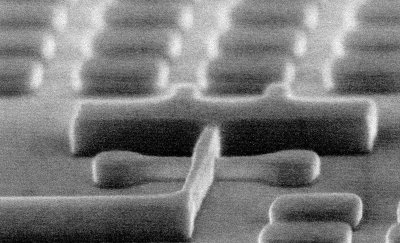

Tri-gate tranzisztor fotója

Az Intel kutatója elmondta, hogy a tri-gate tranzisztorokból álló kísérlei áramkörök a vállalat oregoni D1C üzemében készültek és ez lesz az a chipgyár, ahol az Intel elsőként bevezeti a 45 nanométeres csíkszélességű P1266 gyártástechnológiát. Davis kiemelte, hogy az alkatrészek gyártásához a már meglevő eljárások és eszközök jelentős része felhasználható, ami rendkívüli módon csökkenti az előállítási költségeket. A 45 nanométeres technológiával előállított Intel chipek sorozatgyártása a jelenlegi tervek szerint 2007-ben kezdődik meg.

A fogyasztás és hőtermelés csökkentésének jegyében az Intel három további újdonságról is beszámolt. A vállalat többek között olyan technológiákkal küzd ezen jelenségek ellen, mint a már ismertetett tri-gate tranzisztor, speciális áramkörtervezési eljárások, többszálú utasításvégrehajtás (multi-threading), vagy új tokozás. A vállalat szintén a VLSI Symposium 2003-on hozta nyilvánossága egy, a Purdue egyetemmel közösen végzett kutatás eredményeit. Ezek szerint az áramkör elemeinek megfelelő elrendezésével a felhasznált gyártástechnológiától függetlenül akár ötödére csökkenthető a gyártástechnológiai pontatlanságokból adódó selejtarány.

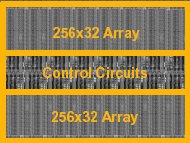

256 bejegyzést tartalmazó 64 bites regiszterfájl

A vállalat az alacsony szivárgás kapcsán még két további újdonságról számolt be, azonban a telefonos konferencián ezeket részleteiben nem ismertették. Az egyik újdonság egy 90 nanométeres csíkszélességű, 256 bejegyzést tartalmazó 64 bites regiszterfájl, amelynek tápfeszültsége 0,9 és 1,2 Volt között változhat. A változó tápfeszültségnek köszönhetően az Intel 46 százalékkal tudta csökkenteni a szivárgást. A regiszterfájl maximális órajele 6,5 GHz lehet. A másik hasonló újdonság egy 1 GHz-es órajelű 16x16 bites MAC (szorzatösszeg) egység, amely szintén 90 nanométeres csíkszélességgel készül és a dokumentált megoldások közül a legnagyobb teljesítmény/fogyasztás aránnyal rendelkezik, ugyanis 1 GHz-es órajelet figyelembe véve fogyasztása 22 milliwatt. A MAC igény esetén 500 MHz-es órajelen is járatható, ekkor 0,8 Voltos tápfeszültséggel 3 milliwattot fogyaszt.

[oldal:Újdonságok az AMD műhelyéből]

Az Intel elsőszámú riválisának számító Advanced Micro Devices (AMD) az év eleje óta az IBM-mel szoros együttműködésben dolgozik a jövő félvezető áramköreiben felhasználható technológiák fejlesztésén. A sunnyvale-i vállalat kutatóinak -- amint arról a rendezvényen beszámoltak -- az IBM által kifejlesztett SOI és feszített szilícium (strained silicon) technológiákat alkalmazva sikerült minden korábbi dokumentált megoldásnál gyorsabb tranzisztorokat létrehozniuk. A sebességnövekedés az újonnan bevezetett, fémből készült gate-elektródának köszönhető.A jelenlegi tranzisztorok nagy többségén az áram folyását szabályozó kapuelektróda polikristályos szilíciumból (poliszilícium) készül. Az AMD kutatói azonban nikkelszilicidet használtak, és azt tapasztalták, hogy jelentősen javult a kapu vezetőképessége és csökkent a szivárgás. Ezt a megoldást kombinálva a fully depleted SOI (FDSOI) technológiával készítettek el egy olyan p-csatornás MOS (PMOS) tranzisztort, amely 30 százalékkal gyorsabb, mint a dokumentált hasonló megoldások. A SOI gyártási mechanizmus során a csatornát, ahol a tranzisztor árama folyik, egy rendkívül vékony üveg vagy szilícium-dioxid szigetelőréteggel választják el a szilíciumkristálytól.

Feszített szilícium (Forrás: IBM Research)

Szintén nikkelszilicid kapuelektródával, de feszített szilícium technológiát alkalmazva pedig olyan n-csatornás MOS (NMOS) tranzisztort sikerült létrehozniuk a kutatóknak, amely 20-25 százalékkal nyújtott jobb teljesítményt, mint a publikált hasonló megoldások. A feszített szilícium technológia hátterében az a felismerés áll, hogy egyes ásványok atomjai természetüknél fogva idomulnak egymáshoz. Amennyiben szilíciumot helyeznek egy lazább atomi szerkezetű hordozóra (mint amilyen az egyebek mellett az IBM által használt szilícium-germánium), a szilícium atomjai idomulnak a hordozóéihoz és "kifeszülnek". E kifeszülő, elnyúló szilíciumon a kisebb ellenállásnak köszönhetően a technológiát kidolgozó IBM szerint 70%-kal gyorsabban áramolnak keresztül az elektronok, ami a chipek esetében 35%-os teljesítménynövekedéshez vezethet.

Craig Sander, az AMD gyártástechnológia-fejlesztési igazgatója a rendezvényen elmondta, hogy az ismertetett fejlesztések várhatóan a 65 nanométeres és annál fejlettebb gyártástechnológia bevezetésekor juthatnak szerephez. Az AMD kutatásai azt mutatják, hogy a feszített szilícium és a SOI technológia egyszerre is alkalmazható a gyártási folyamat során. A vállalat egyben vizsgálja a többkapus megoldásokat is, így kísérletezik az IBM által preferált FinFET, vagy kétkapus, és az Intel által támogatott háromkapus tranzisztorokkal is, azonban egyelőre még egyik megoldás mellett sem kötelezte el magát.