Intel Itanium 2: egy új korszak kezdete

Az Intel és a HP 1993-ban kezdték meg közös projektjüket, amelynek célja egy teljesen új, versenyképes 64 bites processzor megalkotása volt. Az Itanium tavaly május végén jelent meg a piacon, de nem aratott túl nagy sikert. Eltelt egy év és megjelent a második generációs Itanium processzor. Vajon sikeres lesz? Szerintünk igen...

Réges-rég, egy messzi-messzi galaxisban...

Bár az Itanium (IA-64) projekt hivatalosan csak 1994 óta létezik, a története sokkalta régebbre vezethető vissza. A HP mérnökei -- élükön a VLIW architektúrák egyik gurujával, Josh Fisherrel -- már 1989-ben elkezdték egy VLIW processzor tervezését, amelyet később az Intellel együtt fejlesztettek tovább. A HP és az Intel együttműködése 1993-ban kezdődött és 1994-ben hozták nyilvánosságra. Az IA-64 utasításkészlet-architektúra specifikációi 1997 óta érhetők el, az első IA-64 processzor (Merced) pedig 1999 elején készült el, azonban a kereskedelmi megjelenésére még további két évet kellett várni: a Merced hivatalosan 2001. május 29-én került piacra Itanium néven.

Az Intel Itanium processzor

Nemcsak az Intel, hanem a HP is elkötelezettje az Itanium processzorcsaládnak (IPF, Itanium processor family). A jelenlegi termékterveken már 2005-2006 táján megjelenő hardverek is szerepelnek. Ismeretes, hogy a Compaq tavaly bejelentette, hogy Alpha és MIPS alapú számítógépeit Itanium alapokra helyezi át és megkezdi a Tru64, OpenVMS, illetve NonStop Kernel operációs rendszereinek Itaniumra történő átültetését. Miután a HP felvásárolta a Compaqot, az Itanium még hangsúlyosabb szerephez jutott, lévén az Intel és a HP közös gyermeke, másrészt az egyesült HP a UNIX/RISC piac első számú szállítója. A nagy szervergyártók közül az IBM és az SGI (MIPS) is jelezte, hogy hosszú távon számít az Itaniumra, egyedül a Sun Microsystems nem tervezi a processzor használatát, noha egy 1997-es HP Itanium prezentáció az architektúra legnagyobb támogatói között említi a UNIX-piac második számú gyártóját.

Az IA-32 szerverek egyik vezető gyártója, a Dell egyelőre nem kíván Itanium 2 processzoros rendszereket forgalmazni. Sokan ezt az Itanium 2 kudarcaként értékelik, azonban szakértők rámutatnak, hogy a Dell üzleti modellje a nagy volumenű értékesítésen alapul, márpedig az Itanium egyelőre nem illik bele ebbe a modellbe.

Az Itanium processzorcsalád tagjain jelenleg Windows XP, Windows Advanced Server Limited Edition, Linux (SuSE, Red Hat, MSC, TurboLinux, Debian, UnitedLinux) és HP-UX operációs rendszerek futtathatók, de a Microsoft bejelentése szerint a közeljövőben megjelenik a Windows .NET Datacenter Server és Enterprise Server Itaniumon futó változata, a HP pedig gőzerővel dolgozik az OpenVMS, illetve a NonStop Kernel portolásán. A vezető nagyvállalati alkalmazások közül a BEA Weblogic, i2 Supply Chain, Factory Planner, IBM DB2, Websphere, Microsoft SQL Server 2000, Oracle 9i, SAP R/3, APO, LiveCache és SAS v9.0 szoftverekne kmáris elérhető az Itanium processzorokon futó változata.

Természetesen nem csak a számítógépgyártók és az alkalmazásfejlesztők hisznek az Itanium sikerében, hanem az elemzőcégek is. Az IDC előrejelzése alapján 2006-ra a világon eladott szerverek több, mint 50 százaléka épül majd az Itanium processzorcsalád tagjaira.

[oldal:VLIW és EPIC]

Ahhoz, hogy megértsük az Itanium működését, kicsit vissza kell mennünk az időben, mégpedig az első VLIW (very long instruction word) architektúrák megszületéséig. Azt mindannyian tudjuk, hogy egy processzor teljesítménye akkor lehet a legmagasabb, ha adott időben minél több műveletet végez el párhuzamosan. Azonban az utasítások párhuzamosításának előfeltétele a megfelelő függőségek kezelése és az utasítások hatékony ütemezése. A szuperskalár processzorok esetében e feladatok jelentős részét hardveresen valósítják meg, azaz a program futásakor a processzorra hárul a párhuzamosítható utasítások felismerése és a párhuzamosan végrehajtható kódrészletek kinyerése. E funkciók azonban egyre bonyolultabb és bonyolultabb áramköröket kívánnak: egy modern szuperskalár processzorban a tranzisztorok jelentős része nem az utasítások végrehajtását, hanem a párhuzamosságok felismerését és kezelését, az utasítások ütemezését szolgálja.Az első VLIW processzorok a 70-es években jelentek meg és főként tudományos célra szánt számítógépekben alkalmazták őket. A VLIW architektúrák lényege, hogy az utasítások párhuzamosításáról nem a processzor, hanem a fordítóprogram gondoskodik, és a hardver gyakorlatilag egy teljesen párhuzamosított kódot kap meg végrehajtásra. Egy utasításban ilyen formán több mező található, amelyek egy-egy végrehajtóegységet vezérelnek. Innen ered a VLIW, vagyis "nagyon hossszú utasításszó" név is, ugyanis a VLIW processzorok utasításai a végrehajtóegységek számától függően akár 1024 bit hosszúak is lehetnek. A VLIW elnevezést egyébként a 80-as évek elején vezették be.

A fordítási időben történő ütemezés előnye, hogy a fordítóprogram több információval rendelkezik a futtatni kívánt szoftverről, mint a processzor, ráadásul a függőségek kezelésére és párhuzamosítható utasítások kinyerésére gyakorlatilag végtelen mennyiségű idő és erőforrás áll a rendelkezésre. Gyártástechnológiai szempontból előny, hogy a processzorról lekerül a bonyolult ütemezési mechanizmus, így adott tranzisztorszám mellett több végrehajtóegység, vagy nagyobb cache memória kerülhet a chipre. Más szóval azonos komplexitás és órajel mellett egy VLIW processzor nagyobb teljesítménypotenciállal rendelkezik, mint egy szuperskalár architektúra.

A VLIW-ek hátránya, hogy a fordítónak rendkívül részletes ismeretekkel kell rendelkeznie a programot futtató processzorról, az egyes utasítások végrehajtásához szükséges időről, a végrehajtóegységek számáról és felépítéséről, hiszen csak így van lehetőség a hatékony ütemezésre. Könnyen belátható, hogy abban az esetben, ha a programot egy másik -- például több végrehajtóegységgel rendelkező -- processzoron szeretnénk futtatni, azt újra kell fordítani, hogy kihasználhassuk az új erőforrásokat. A VLIW-ek a 80-as évek végén tűntek el a számítástechnika színpadáról, azonban ma szinte reneszánszukat élik: számos beágyazott processzor és DSP mellett általános célú processzorok (Transmeta Crusoe, Sun MAJC) is a VLIW filozófia mentén épülnek fel.

Az Itanium nem VLIW architektúra, azonban erősen hasonló elképzelésen alapul. A leginkább lényeges különbség, hogy az utasítások nem ugyanolyan "szélesek", mint a processzor, egy IA-64 utasítás (bundle) mindig 128 bites és összesen három vezérlőmezőt tartalmaz. Ez teszi lehetővé, hogy az IA-64 utasításkészlet-architektúra több, különböző generációs megvalósulásán, azaz a jelenlegi és következő generációs Itanium processzorokon is változtatás nélkül lehessen ugyanazt a kódot futtatni. A végrehajtóegységek számának növelésével párhuzamosan a processzor több "utasításcsomagot" lesz képes fogadni és feldolgozni, nem szükséges a programokat újrafordítani. Az utasítások a konkrétan végrehajtandó kód mellett az utasítások típusáról és az esetleges függőségekről is tájékoztatják a processzort, így az megfelelően tudja kezelni őket.

[oldal:Pár szó az EPIC-ről]

Az Itanium ún. EPIC (explicitly parallel instruction computing) processzor. Az EPIC -- hasonlóan a RISC, CISC vagy VLIW fogalmakhoz -- nem egy szabálygyűjtemény vagy konkrét leírás, inkább afféle tervezési filozófia, amelynek lényege, hogy a létező legtöbb utasítás fusson párhuzamosan, még akkor is, ha azok egy része feleslegesen hajtódik végre. Ennek érdekében az Itanium elágazáskezelése is elég érdekes: mint ismeretes, a processzorok az erőforrások leghatékonyabb kihasználása érdekében elágazó utasítás esetén becslést alkalmaznak, azaz valamilyen szabály -- például az addigi elágazások viselkedése -- alapján megpróbálják megbecsülni, milyen ágon fut majd a program, és abba az irányba folytatják a végrehajtást.A kifinomult elágazásbecslési algoritmusok ma már akár 92-97 százalékos becslési pontosságot is lehetővé tesznek, azonban természetesen még így is előfordul téves becslés. Ilyenkor a futószalagokat ki kell üríteni és a program végrehajtását a másik ágon kell folytatni. Ez nyilvánvaló időveszteség. Az Itanium ezt a veszteséget úgy hidalja át, hogy az elágazó utasítás után mindkét feltételes ágat elkezdi végrehajtani, majd utólag, a feltétel kiértékelésekor dönti el, hogy melyik volt a "helyes út". Mindkét ág kap egy megkülönböztető jelzést, és a feltétel kiértékelődése után a jelzés alapján a processzor eldönti, melyik ág futtatását kell tovább folytatni és a feleslegesen végrehajtott utasítások eredményei pedig törlődnek. Ezt a megvalósítást az Intel "predication"-nek nevezi.

Korunk processzoraiban egyre nagyobb problémát jelent a memória késleltetése, vagyis az az idő, amennyi egy adatbetöltő utasítás (LOAD) és a kért adat megjelenése között eltelik. Az is nyilvánvaló, hogy minél több erőforrással rendelkezik egy processzor, annál több megy "pocsékba" az alatt az idő alatt, amíg a CPU a memóriára vár -- hiszen ezt az időt hasznosan, számolással is tölthetné. Mivel az Itanium utasítás-ütemezése fordítási időben történik, lehetőség van ún. spekulatív adatbetöltésre, vagyis az utasítások olyan átrendezésére, hogy az adatbetöltő utasítás és az adat feldolgozása (LOAD-USE) közé más, független utasítások kerüljenek.

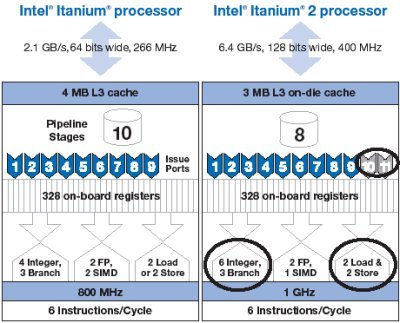

Miben különbözik az Itanium 2 az Itaniumtól? Az új processzor két fokozattal rövidebb futószalaggal rendelkezik és két további egész végrehajtóegységgel gyarapodott, így összesen 6 egész, 3 elágazáskezelő, 2 lebegőpontos és 1 SIMD végrehajtóegységgel rendelkezik, és egy órajelciklus alatt két LOAD (adatbetöltés) és két STORE (adatkiírás) elvégzésére képes, szemben az Itaniummal, amely csak két LOAD vagy két STORE műveletet hajt végre órajeleként. Az elsőszintű cache struktúrája nem változott, azonban a késleltetését 2 órajelciklusról az elméleti minimumnak mondható 1 órajelciklusra csökkentették. A másodszintű gyorsítótár 96 kbyte-ról 256 kbyte-ra nőtt, miközben a késleltetése 12 órajelciklusról 5 órajelciklusra csökkent. A 4 Mbyte harmadszintű cache az Itanium esetében -- a Pentium II-höz hasonlóan -- külső chipben foglalt helyet, az Itanium 2-ben már a mag része, a késleltetése 20 helyett 12 órajelciklus, a sávszélessége 11,7 Gbyte/sec helyett 32 Gbyte/sec. Az Itanium 2-ben kiviteltől függően 1,5 Mbyte vagy 3 Mbyte L3 cache található.

Változott a rendszerbusz is: az Itanium 64 bites, 133 MHz-es "double pumped" buszt használt, amelynek maximális sávszélessége 2,1 Gbyte/sec volt, az Itanium 2 busza 128 bites és 200 MHz-en működik, elméleti maximális adatáteresztő képessége 6,4 Gbyte/sec. Míg az Itanium órajele 733, illetve 800 MHz volt, az Itanium 2 900 MHz-es és 1 GHz-es kivitelben lesz elérhető. Az Intel becslései szerint az órajel növekedésének és az architekturális fejlesztéseknek köszönhetően az Itanium 2 akár másfél-kétszer nagyobb teljesítményt is nyújthat elődjénél, miközben az alkalmazások változtatás nélkül futnak rajta.

Ami az Itanium 2 fizikai paramétereit illeti, a processzor 0,18 mikronos, alumínium-alapú gyártástechnológiával (P858) készül, a mag mérete 421 mm2, a tranzisztorok száma 221 millió, bár ennek jelentős részét a harmadszintű gyorsítótár teszi ki.

| Processzor | Órajel | Csíksz. | Tranzisztor | Magméret |

|---|---|---|---|---|

| Itanium 2* | 1 GHz | 0,18 mikron | 221M | 421 mm2 |

| Itanium | 800 MHz | 0,18 mikron | 30M | N/A |

| HP PA-8600 | 552 MHz | 0,25 mikron | 140M | 467 mm2 |

| HP PA-8700 | 800 MHz | 0,18 mikron | 200M | 350 mm2 |

| HP PA-8800* | 1 GHz | 0,13 mikron | 300M | 361 mm2 |

| Alpha EV6 | 575 MHz | 0,35 mikron | 15,2M | 314 mm2 |

| Alpha EV67 | 750 MHz | 0,25 mikron | 15,2M | 225 mm2 |

| Alpha EV68C | 1,25 GHz | 0,18 mikron | 15,2M | 125 mm2 |

| Alpha EV7* | ~1,2 GHz | 0,18 mikron | 152M | 400 mm2 |

| UltraSPARC III Cu | 1,05 GHz | 0,18 mikron | 29M | 244 mm2 |

| IBM Power4 | 1,3 GHz | 0,18 mikron | 170M | 400 mm2 |

A HP zx1 chipkészlet

A HP Itanium 2 és későbbi processzorokat támogató chipkészlete zx1 névre hallgat. A zx1 három részből áll, a "MIO" (memória és I/O vezérlő), az "I/O adapter" (PCI, PCI-X, AGP vezérlő) és a "scalable memory expander" (memóriakapacitás- és sávszélesség-növelő) chipekből. A zx1 MIO chip 25 millió tranzisztorból áll, 1657 kivezetéssel rendelkezik és a HP tervei alapján az Agilent Technologies gyártja. A zx1 chipkészlet DDR200 SDRAM-ot támogat, 1 és 2 processzoros rendszerekbn 8,5 Gbyte/sec, 4 processzoros rendszerekben 12,8 Gbyte/sec memóriasávszélességet biztosít.

4 és 2 processzoros Itanium 2 rendszer zx1 alapokon

A hírek szerint a HP eközben már tervezi a zx1 utódját, a 8-32 processzort támogató "Pinnacles" kódnevű chipkészletet, amely a McKinley mellett további két Itanium generációt (Madison, Montecito) is támogat majd. A Pinnacles piaci premierje a várhatóan 2003-ban megjelenő és a 0,13 mikronos csíkszélességű, 6 Mbyte L3 cache-t tartalmazó Madison processzorokra épülő új HP Superdome szerverben lesz.

[oldal:Itanium: sikerre ítélve]

Az Itanium 2 rendkívül fontos tulajdonsága, hogy buszkompatibilis a HP PA-RISC család legújabb tagjaival, ami azt jelenti, hogy egyes HP szerverek a későbbiekben akadály nélkül alakíthatók át az Itanium processzorcsalád fogadására. Mivel a HP-UX operációs rendszer ugyanazokat a funkciókat biztosítja IPF (Itanium processzorcsalád) platformon, mint PA-RISC-en, a befektetések hosszú távon is védve vannak. A PA-RISC architektúrára fordított HP-UX alkalmazások binárisan kompatibiisek az Itaniummal, azaz változtatás nélkül futtathatók az új processzoron.Az Itanium várt sikerében kulcsfontosságú szerepet játszanak az operációs rendszerek. Egy nagyvállalatnál nem ritka a UNIX, Windows és Linux együttélése, amelyek különböző feladatokat (pl. adatbázis-szerver, alkalmazás-szerver, webszerver) látnak el és különböző architektúrákon futnak. Mivel az IPF mindhárom operációs rendszer (UNIX, Windows, Linux) futtatására képes, a vállalatok egyszerűsíthetik és szabványosíthatják informatikai infrastruktúrájuk egyes elemeit, vagy akár egyetlen Itanium-alapú gépen konszolidálhatják szervereiket és az egyes partíciókon más és más operációs rendszert, illetve alkalmazásokat futtathatnak.

Az Itanium jelenleg az egyetlen 64 bites processzor a piacon, amelyen Windows futtatható. Az első generációs Itaniumot sok kritika érte, mert elvben ugyan képes IA-32 kód futtatására, a gyakorlatban viszont ezt rendkívül lassan teszi. Jelenleg ez a probléma is megoldódni látszik, ugyanis a WoW64 (Windows on Windows 64) technológia segítségével lehetővé válik, hogy az Itaniumon futó 64 bites Windows operációs rendszeren 32 bites Windowsra írt programok fussanak, mégpedig a natív alkalmazások sebességének mintegy 70 százalékával.

A HP és az Intel szerint az Itanium eleinte elsősorban a munkaállomások piacán lesz sikeres, köszönhetően a széles körű támogatottságnak és a kiemelkedő teljesítménynek. Vegyük észre, hogy lebegőpontos teljesítmény (SPECfp_2000) tekintetében az Itanium 2 a legerősebb processzor a piacon, egész teljesíménye (SPECint_2000) pedig a 64 bites processzorok között a második legjobb, azonban az első helyezett IBM Power4 egyelőre kizárólag szerverekben fordul elő. Sokan vélik úgy, hogy a munkaállomások esetében a közeljövőben egyre inkább terjedni kezd a Linux operációs rendszer, amelynek legnagyobb disztribútorai (Red Hat, SuSE, TurboLinux, MSC, Debian, UnitedLinux) mind támogatják az Itanium processzorcsaládot. A HP várkozásai szerint 2003 közepére az általa eladott munkaállomásokban több Itanium processzoros gép lesz, mint PA-RISC alapú.

HP zx6000 és zx2000 munkaállomások (Fotó: HWSW)

A HP a mai napon két Itanium 2 processzorra épülő munkaállomást is bejelentett: a zx2000 egy darab 900 MHz-es, 1,5 Mbyte L3 cache-el rendelkező Itanium processzort, HP zx1 chipkészletet, legfeljebb 4 Gbyte memóriát és AGP grafikus kártyát (NVIDIA Quadro, ATI FireGL, ATI Radeon) tartalmaz. A HP zx6000 két processzort támogat, amelyek akár 1 GHz-en is működhetnek és egyenként 3 Mbyte L3 cache-t tartalmazhatnak. A zx1 chipkészletre épülő munkaállomás legfeljebb 12 Gbyte memóriát támogat. A gépeken HP-UX 11i v1.6, Windows vagy Linux operációs rendszer futhat. A gépek ára 4600 dollárnál kezdődik.

A HP zx6000 munkaállomás belülről (Fotó: HWSW)

Természetesen az Itanium 2 szerverfeladatok (tranzakció-feladolgozás, adatbázis-kezelés, ...) elvégzésekor sem vall szégyent. A HP bejelentése szerint a két-, illetve négyprocesszoros, Itanium 2-alapú rx2600 és rx5670 szerverek 40638, illetve 79000 pontos TPC-C eredményükkel maguk mögé utasítanak minden más két- és négyprocesszoros rendszert, mindezt rendkívül alacsony, mintegy 5,1 dollár/TPmC ár/teljesítmény viszony mellett. Az SAP R/3 SD (Sales and Distribution) tesztben a HP Itanium 2 alapú rendszere pedig 470 felhasználót tudott egy időben kiszolgálni, amely a legmagasabb eredmény a négyprocesszoros gépek között.

HP rx5670 szerver

A HP ma bejelentett Itanium 2 processzoros szerverei közül az rx2600 egy rackbe építhető, 1 vagy 2 processzort és legfeljebb 12 Gbyte memóriát tartalmazó belépő szintű rendszer, az rx5670 pedig egy 1-4 processzoros, torony kivitelű, alsó kategóriás, legfeljebb 48 Gbyte memóriát támogató rendszer. Az rx2600 szerver ára 5400 dollárnál indul, a négyprocesszoros rendszer alapkiépítésben 23 ezer dollár körüli összegért kapható.

HP rx2600 szerver

Természetesen eközben gőzerővel folynak a következő generációs Itanium processzorok fejlesztési munkálatai. A 0,13 mikronos csíkszélességgel készülő Madison megjelenése a következő évre várható az olcsóbb, alacsonyabb fogyasztású Deerfielddel együtt. Az Intel nemrégiben jelentette be, hogy a Madison első mintapéldányai már elkészültek és a processzorokat több operációs rendszerrel is tesztelik. A vállalat 2004-ben tervezi piacra dobni a Montecito kódnevű chipet és 2005-2006 táján érkezik a Chivano fedőnevű lapka. A Montecito minden bizonnyal tartalmazni fogja a Xeonból már ismert Hyper-Threading technológiát, a Chivano -- amely valószínűleg már 65 nanométeres csíkszélességgel készül -- pedig egy chipen várhatóan két processzormagot (CMP) tartalmaz majd.