Az Intel már a Nehalemet demózta

A tegnap kezdődött őszi Intel Developer Forumon a november 12-én érkező Penryn-generációs chipekről gyakorlatilag szó se esett, a vállalat vezetői már az azt követő lapkákkal foglalkoztak. Pat Gelsinger, az Intel Digital Enterprise Group vezetője működés közben prezentált egy Nehalem-alapú gépet, Paul Otellini elnök-vezérigazgató pedig bemutatott egy olyan szilíciumszeletet, amelyen már 32 nanométeres chipek kaptak helyet.

Működik a Nehalem

Az Intel 2006 tavaszán jelentette be, hogy kétéves termékciklusra áll át, amelynek keretében a páratlan években új gyártástechnológiát, a páros években pedig új architektúrát vezet be. Az idei év újdonsága a Penryn-generáció, amely 45 nanométeres csíkszélességgel készül, de architektúráját tekintve nem sokban különbözik a tavaly útjára indított Conroe-tól. A Nehalem ugyanazzal a 45 nanométeres eljárással készül majd mint a Penryn, a chipben azonban számos architektúrális fejlesztés kapott helyet. Ennek köszönhetően azonos fogyasztás mellett mintegy 20 százalékkal nagyobb teljesítményt nyújt elődjénél -- becslik az Intelnél.

A Nehalem legfontosabb újdonsága, hogy végre integrált memóriavezérlőt tartalmaz, illetve a korábban CSI (Common System Interface) néven ismert, végül QuickPatch Interconnectre keresztelt, PCI Express-alapú rendszerbuszhoz csatlakozik -- 2008 végétől, a Tukwila kódnevű chiptől kezdve ezt használja majd az Itanium termékvonal is. A Nehalemben emellett ismét helyet kap majd az Intel Hyper-Threading technológiája, vagyis a magok két utasításszálat képesek majd egyszerre feldolgozni. Az Intel Developer Forumon bemutatott demógép -- amely a vadonatúj Talesberg chipsetre épült -- két darab négymagos chipet tartalmazott, amelyeken összesen 16 programszál futott.

Pat Gelsinger és Jim Brayton, a Nehalem projektmenedzsere

A Nehalemet úgy tervezték meg, hogy a lehető legegyszerűbben lehessen a piaci igényeknek megfelelő változatokat létrehozni, így csak üzletpolitikai kérdés, hogy egy processzorban 1 vagy 8 mag van, mekkora a gyorsítótár vagy hogy hány memóriavezérlő kerül bele. A Nehalem asztali és mobil változataiba már grafikus vezérlőt is képes integrálni az Intel. Ez azt jelenti, hogy a tervezőmérnökök ezekből az építőelemekből dolgozva könnyen és gyorsan hozhatnak létre mobil, asztali és szerverprocesszorokat, amelyek feladataihoz szinte tetszőlegesen kombinálhatják a részegységeket. Jól értesült források szerint két-, négy- és nyolcmagos Nehalemeket ad majd ki az Intel.

A Nehalem piaci bevezetése 2008 második felében esedékes majd, és hogy az Intel milyen jól áll a fejlesztéssel, azt az is mutatja, hogy a három hete elkészült első mintapéldányok már működőképesek, Windows és Mac OS X operációs rendszert futtatnak a vállalat laborjaiban. Otellini az IDF közönsége előtt működés közben is bemutatott egy Nehalem-alapú rendszert, a kiállított gépen egy beszédszintetizátor a következőket mondta: "Hello, Paul, én Nehalem vagyok. Még csak három hetes vagyok, de már tudok beszélni". A monolitikus négymagos Nehalem 731 millió tranzisztort tartalmaz egyetlen lapkán.

Az első 32 nanométeres chipek

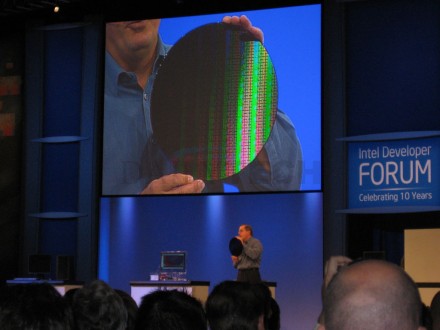

2009-ben, a 32 nanométeres gyártósorok beindítása után az Intel már nyolcmagos Nehalemeket építhet. Hogy a vállalat mennyire jól áll a 32 nanométeres csíkszélességű technológia bevezetésével, mi sem mutatja jobba annál, hogy Otellini a színpadon bemutatott egy szilíciumszeletet, amelyen 32 nanométeres csíkszélességű SRAM chipek sorakoztak. Az Intel jellemzően SRAM lapkákat használ az új gyártási eljárások tesztelésekor. A Nehalem 32 nanométeres változatának kódneve egyébként Westmere, ezt 2010-ben követi az új architektúrára épülő Sandy Bridge.

Amint arról korábban már beszámoltunk, az Intel 32 nanométeres gyártási eljárásában elsőként alkalmazza majd azt a háromkapus (tri-gate) tranzisztor-struktúrát, amelynek prototípusát még 2002-ben mutatták be. A cég szerint a processzorok fogyasztása ennek köszönhetően azonos órajel mellett 35 százalékkal alacsonyabb lehet a jelenleginél. A háromkapus tranzisztor alkotóelemei nem rétegszerűen helyezkednek el, hanem háromdimenziós struktúrát alkotnak: a forrás és a nyelő a szubsztrátból kiemelkedő vezetéken kap helyet, amelyet három oldalán érintve satuszerűen fog közre a kapuelektróda.

Mike Mayberry, az Intel gyártástechnológiai felelőse szerint a 32 nanométeres technológia a tri-gate tranzisztor mellett magas k-együtthatójú dielektrikummal történő szigetelést, szigorú titokként kezelt összetevőkből álló, fémoxidból készült kapuelektródát, valamint feszített szilíciumot tartalmaz majd, amelyeknek köszönhetően azonos teljesítményfelvétel mellett akár 45 százalékkal nőhet a kapcsolási sebesség, illetve jelentősen csökkenhet a szivárgási áram.