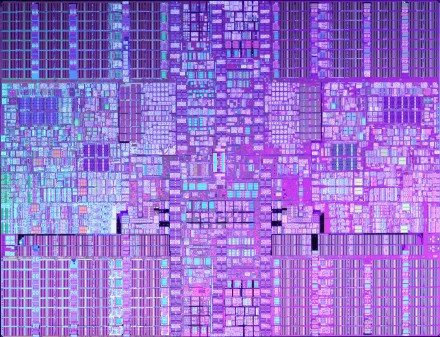

Power6, második kör: tervezési koncepció, és teljesítmény

Egy hónapja jelentette be következő generációs Power6 szerverchipjét az IBM, mely a radikális designjával elért extrém órajelekkel hívta fel magára a figyelmet. Bár a jelenlegi információink szerint az erre épülő új System p és i dobozok csak az év vége felé, de szélesebb körben inkább csak jövőre válnak elérhetővé, érdemes a Power6 koncepciójára, és az ezzel elért teljesítményre egy pillantást vetni.

A Power6 design koncepciója

Az ezredfordulót követő processzortervezés legmarkánsabb vonása, hogy a tervezők az órajelek további srófolása és a chipek egyre erőteljesebb felépítése helyett a szálszintű párhuzamosság felé fordultak. Erre három meghatározó erő késztette a vállalatokat. Ezek közül a legkérlelhetetlenebb az energiafal: a processzorok komplexitásának és órajelének emelkedésével a fejlettebb gyártástechnológia ellenére is exponenciálisan növekedett a fogyasztás, ami egy szint felett tolerálhatatlan. Tekintve, hogy az órajel emelkedésével a tápfeszültség emelése miatt négyzetesen növekszik a fogyasztás, lényegesen energiahatékonyabb két alacsonyabb órajelű processzor, mint egy azonos, de magasabb frekvencián futó.

A másik ezzel szorosan összefüggő, hogy a '90-es években bevetett futásidejű optimalizációs technikák, mint az utasítások átrendezése, ütemezése és soronkívüli végrehajtása, az elágazásbecslés, spekulatív előtöltések kezdtek kifulladni, vagyis a szilíciumra pakolt logika komplexitásának fokozódásával nem tartott lépést a teljesítmény -- az utasításszintű párhuzamosság futásidejű előállítása jelentős kihívás. A harmadik jelenség pedig a memóriafal, vagyis a processzorok teljesítményének fokozódásával a memória nem tudott, és nem tud lépést tartani késleltetésben.

Az iparág emiatt a többmagos (valójában több processzor) felépítés felé fordult, így az Intel, az AMD immár négy magról beszél, miközben igyekeznek növelni az órajelet és magok teljesítményét is. A Sun Microsystems eközben a masszívan párhuzamos felépítés felé fordult a nyolcmagos, magonként 4 utasításszállal rendelkező UltraSPARC T1-gyel, és a másfél-két éven belülre várható felsőkategóriás Rockkal, mely 16 magot és 32 szálat kezel majd -- miközben a magonkénti teljesítmény elmarad a riválisoktól. Akkor miért döntöttek úgy az IBM-nél, hogy a Power6-tal mégis az extrém órajelek felé veszik az irányt?

Bár a masszívan párhuzamos felépítés tisztán hardver implementációs szemszögből nézve előnyös minden szempontból, ha a minél nagyobb teljesítmény és az energiahatékonyság a cél, ez feltételezi, hogy létezik hozzá a megfelelő szoftverréteg is. Márpedig sok fejlesztőnek úgy tűnhet, mintha a processzortervezők nem kérdezték volna meg őket arról, hogy mit szeretnének. A masszívan párhuzamos felépítésű szoftverek előállítása ugyanis nem triviális feladat a szoftveripar számára, ahogyan azt a PC-s alkalmazás-fejlesztőkön és a játékiparon is látni lehet, de a kernelek és a szerverszoftverek többségének skálázódása is csak az utóbbi időben kezdi utolérni a hardvert. Somma sommárom: a szoftvereseknek a nagyteljesítményű processzorok (magok) fekszenek jól, minél kevesebb konkurrens szállal.

Ha a fejlesztők meg is tudnák oldani a tökéletes párhuzamosítás problematikáját, a nagy szoftverszállítók licencelése alapvetően továbbra is a processzorok vagy a processzormagok számán alapul, vagyis amit nyerünk a nagyobb teljesítményű chipeken, azt bőven elveszíthetjük a drága licenceken. Ha mindezt összerakjuk, akkor jobban érthető, az IBM miért tért ki látszólag az új megatrend medréből, és maradt a Power5 chiphez hasonlóan két magnál, és chipenként 4 szálnál: az alapjaiban azonos design a lehető legkisebb kihatással van a szoftverek működésére, miközben a teljesítmény ugrik.

A Power6 az extrém órajelek érdekében (jelenleg 3,5 és 4,7 gigahertz közötti modellek ismertek) redukálta belső komplexitását, így például a komplex soronkívüli utasításvégrehajtás nagy része kikerült a Power RISC-magokból, és a tervezők az egyszerűbb magok agresszív mikroelektronikai implementációjára helyezték a hangsúlyt. Az extrém órajeleket a két mag, és a magonként két párhuzamos utasításszál (melyeket több végrehajtóegység szolgál ki) igyekszik ellensúlyozni a memória felől, és a chip memóriavezérlője és más összeköttetései is azt célozzák, minél kevesebbet álljanak üresen a végrehajtósegységek -- a Power6 önmagában is radikális, de az IBM ismét egy nagyot lépett tovább az infrastruktúra terén is, mely nagy egyszálú teljesítmény mellett közel lineáris skálázódást biztosít többutas rendszerben a bődületes sávszélességek és alacsony késleltetések révén.

Pudingpróba

Hogy mutat mindez a gyakorlatban? A 4,7 gigahertzen ketyegő Power6 napjaink vitathatóan legnagyobb teljesítményű processzora, energiahatékonyság szempontjából viszont a mérnökök nem voltak képesek meghazudtolni a mikroelektronika törvényeit. Ami az egyszálú számítási teljesítményt illeti, a Power6 a korábbi királlyal, a 3 gigahertzes Woodcresttel (Xeon 5160) van egy szinten az egész számokkal végzett műveletekben (SPECINT2006), optimalizált kódban meg is veri mintegy 5 százalékkal -- viszont eközben jó két és félszer annyi energiát emészt fel. A Power6 lebegőpontos teljesítménye (SPECFP2006) ennél is biztatóbb, itt magabiztosan, 10 százalékkal veri a mezőnyt, beleértve az Itanium 2-t is -- azonban ne feledjük, a Power5 kétszeres energiabüdzséjéből.

A Power6-ot ugyanakkor az IBM nem egyutas munkaállomásokba tervezte, az architektúra ereje egyetlen szálnál nem mutatkozik meg. A többszálú műszaki-technikai számításokra többé-kevésbé releváns SPEC Rates (HPC szerverek) tesztekben a p 570 gépek szégyenbe hozzák a mezőnyt. A 16-magos IBM System p 570 közel 10 százalékkal nagyobb teljesítményt nyújt SPECINT2006_rates alatt, mint egy 32-magos (16 Montecito Itanium 2) HP Integrity rx8640, és ez a különbség megmarad arányosan kisebb gépeknél esetében is. SPECFP2006_rates esetében is hasonló a helyzet -- ezen az új Xeonok sem tudnak változtatni, ha a magok számát nézzük, a négymagosok foglalatonként megközelítik kétutas rendszerben.

A műszaki-technikai számításokat közelítő SPEC CPU teszteket követően, nézzük a szerverfeladatokra valamivel relevánsabb teszteket. A Java-alapú üzleti feladatok számára tesztelni igyekvő SPECJbb_2005 alatt az Intel négymagos Xeonjai 1- és 2-utas szerverekben továbbra is verhetetlennek teljesítmény oldaláról, 20-30 százalékos fölényt mutatnak a Power6-tal szemben -- igaz kétszer annyi maggal, de ugyanannyi utasításszállal. Lineáris skálázódása révén ugyanakkor a Power6 a 4- és 8-utas gépekben elegánsan és megalázóan maga mögé utasítja a konkurenciát, több mint másfél-kétszeres teljesítményt adva le. A Power6-tal az IBM versenyképessége drasztikusan javul a Java-alapú workloadok terén, a Power5+ chipekkel szerelt gépekkel szemben kétszeres fölényt mutat -- köszönhetően a magas órajelnek.

Az adatbázis-alapú natív OLTP (online tranzakciókezelés) feladatot szimuláló TPC-C teszt hagyományosan IBM-es erősség. Elméletileg az OTLP-feladatok nem kedveznek a magas órajelnek, ugyanis alacsony számítási tömeggel bírnak, a futásidő nagy része lemez- és memóriaműveletekkel telik. A 16-magos System p 570 ennek ellenére így is mintegy 60 százalékkal múlja felül a p5 570-et, pedig utóbbinak sem voltak skálázódási problémái.

A jelentős különbséget magyarázhatja a Power6 teljesen szélsőséges memória- és tárolókonfigurációja (768 gigabájt és 117 terabájt), mely rendre másfél- és kétszerese a Power5 kiépítésének, és az új adatbáziskezelő is (DB2 9). Azonos konfigurációban a Power6 rendszer fölénye vélhetően 30, de inkáb 20 százalék alá olvadna, ami már ésszerű, ugyanakkor sokkal kevésbé nevezhető generációs előrelépésnek -- igaz, teljesítményben ezzel csak tovább növekszik mögötte tátongó szakadék, melyet a konkurencia a következő másfél év során biztosan nem fog tudni eltüntetni.

A TPC-C-hez hasonló, 50 százalékot meghaladó ugrás figyelhető meg az SAP Sales and Distribution (S/D) tesztjében is az előző generációs System p 570 rendszerhez, és jellemzően kétszeres teljesítmény a konkurenciához képest, de például 24 Sun UltraSPARC IV+ chip mindössze a háromnegyedét nyújtja egy harmadakkora Power6 konfigurációnak -- magonként egynegyed teljesítményt. Az Oracle benchmarkja alatt a nyolcmagos p 570 gépek lényegében kétszer annyi felhasználót képesek kiszolgálni azonos válaszidő mellett, mint elődeik.

Zárszó

Látható, hogy a Power6 nemcsak egy agresszív design, hanem egy jól teljesítő termék is, melyet egy fejlett infrastruktúrával megtámogatva az IBM tovább erősíti teljesítménybeli vezető szerepét alkalmazások számos típusa alatt, de általánosságban is jelentősen javítja a Power-alapú szerverek versenyképességét. Ezzel az IBM főként a jelentős AIX-bázisának lemorzsolódását minimalizálhatja, a potenciális új ügyfelek megszerzése mellett. Ha a tesztek korlátozott relevanciája miatt nem is győztek volna meg minket a számok, akkor érdemes megnézni a Sun amerikai oldalain a Power6 elleni elszánt támadásokat is lejáratást.

Az architektúra gyenge pontjának a memóriafal tűnik, aminek jelét a TPC-C tesztben is láthattuk, vagyis a jövőben az IBM is minden bizonnyal növeli majd magok számát a teljesítmény, valamint az energiahatékonyság érdekében. A piac alsó feléből érkező, gyorsan felfejlődő négymagos Intel Xeon és AMD Opteron processzorok teljesítményben a 2, 4, vagy akár a 8-utas Power6 gépekkel is rivalizálhatnak majd, majd a jövő év második felében, vagy 2009 elejére már piacra kerülhetnek a következő generációs Itanium és felsőkategóriás UltraSPARC chipek, melyek drasztikus előrelépést képeznek majd, így az IBM így sem ülhet sokáig a babérjain.