Problémák a következő generációs Itaniummal

Tegnap több, egymástól független forrásból röppentek fel olyan nem hivatalos hírek, melyek szerint az Intel Itanium processzorok (IPF) termékvonala komoly csapást szenvedhet. A belsős forrásokkal rendelkező iparági szakértők között futótűzként terjedő, így nagy valószínűséggel valódi hírek szerint komoly problémák adódtak az IPF következő generációs, Montecito kódnevű tagja körül, amelynek megjelenését az év végére ígérte az Intel.

Új technológia - új problémák

Az IPF stratégiai jelentőségű nem csak az Intel, hanem több szervergyártó vagy megoldásszállító számára, nem beszélve azokról az ügyfelekről, amelyek erre a platformra alapozták jövőbeli IT-stratégiájukat. A problémák bizonytalan nagyságú késésre kényszerítik az Intelt, ami kellemetlenül érinti az iparág érdekelt szereplőit. Az esethez közelebb állók szerint a gondok a "Merced-katasztrófa" óta a legrosszabbak (a Merced a legelső Itanium processzor volt).

| The Itanium story |

|

Az Itanium processzorok (IPF) az Intel első chipjei, melyeket a felső kategóriás vállalati rendszerek igényeinek szem előtt tartásával terveztek meg. A koncepció több mint egy évtizeddel ezelőtt kezdett körvonalazódni. Az alapelv az, hogy a szilícium minél egyszerűbb legyen, elkerülve a túlzott komplexitást, valamint az elérhető teljesítménypotenciált növeljék. Az Itanium teljesen új utasításkészlet-architektúrára épül, az IA-64-re. Az Intel elsődleges célja az Itaniummal, hogy alternatívát nyújtson az elburjánzó RISC-architektúrákra, melyek a legtöbb esetben az egyes megoldásszállítók saját fejlesztésű platformjai voltak.

Az eszkalálódó fejlesztési költségek azonban egyre többek számára tették gazdaságtalanná ezeknek az életben tartását, így az Intel a HP-vel közösen megkezdte az IPF-platform megalapozását, amit már akkor is több vállalat támogatott, és azóta újabbak csatlakoztak. Ma IPF-re alapozza jövőjét a HP, az SGI, és beszállt többek között a Fujitsu, az NEC, a Hitachi, a Bull, és a Unisys is. Az IPF-fel szemben két főbb erő maradt egyelőre talpon, az IBM Power-architektúra, és a Sun SPARC, míg az Alpha vagy a PA-RISC sorsa már megpecsételődött. A sokat kritizált és sok ellenszenvet keltő IPF kezdeti gyenge szereplését követően az elmúlt időszakban lendületet szerzett a piacon. A több éves késést követően 2001-ben megjelenő IPF-re alapuló szerverek forgalma 2003-ban megközelítette az 500 millió dollárt, tavaly a 1,5 milliárdot, idén pedig az IDC és a Gartner becslései szerint eléri a 2,5 milliárdot. Az IBM és a Sun RISC-piaci bevételei (egyenként) nagyjából 7 milliárd dollárt tettek ki 2004 során. |

A Foxton végeredményben tehát adott fogyasztási keretből lényegesen több teljesítményt csikar ki, mint a hagyományos tervezésű processzorok. A Foxton teljesen szokatlan módon generálja az órajelet, és végzi a disztribúciót a chipen. A probléma egyik gyökerét talán pont ez szolgáltathatja, hogy a korszerű, nagy teljesítményű processzorok tervezéséhez és teszteléséhez eddig használt automata eszközökön, eljárásokon némileg túlmutató designról van szó -- véli Paul DeMone, a Real World Technologies szakértője.

Az igazi gondot azonban az jelenti, hogy nincs megfelelő B-terv. A Foxton működését ugyan ki lehet iktatni, mikor ún. Fixed Frequency Mode-ba kapcsol a lapka, ekkor azonban a Montecito áramköreinek limitáltsága miatt csak 6-20 közötti egész számú szorzóval képes generálni a busz alapórajelét. Ez azt jelenti, hogy a tervezett 667 MHz-es effektív (333 MHz valós) órajelű busz esetében legalább 2 GHz-en kellene üzemelnie a chipnek. Tovább tetézi a bajt, hogy Foxton nélkül adott órajelet a chip lényegesen magasabb fogyasztáson képes csak elérni, hiszen megszűnik a kifinomult monitorozás és a feszültségek és órajelek folyamatos megfeleltetése.

Eltúlzott célok?

A Montecito végleges tervei már tavaly elkészültek, és az első szilíciumok már hónapok óta a partnereknél vannak. Az eredetileg az idei év végére tervezett piaci premierig a validációs időszak folyik, mikor is a chipeket folyamatosan ellenőrzik, tesztelik, javítják az esetleges hibákat, finomítanak a gyártásán, és igyekeznek elérni a kitűzött órajeleket és fogyasztási mutatókat.

És itt kapcsolódik be a másik feltételezett probléma: a kitűzött órajel-fogyasztás-kihozatal hármas rendszerében a Montecito mintegy 25 százalékkal elmarad attól, amit az előző évben hallottunk. A Montecitónak eredetileg el kellett volna érnie a 2 GHz-et, 667 MHz-es busszal, 100 wattos energiabüdzséből. Jelenlegi állás szerint a fogyasztás és gyártási kihozatal 1,6 GHz-es példányokat enged meg, amelyek Foxtonnal 1,8 GHz-re skálázódhatnak.

Az Inquirer bulvárszaklap egyik szerkesztőjének, Charlie Demerjiannak értesülései szerint a Montecito jelenleg a C0 steppingél tart már, de ez még nem validálható. Amennyiben a C1-es változat átmegy a teszteken, jövő februárban megindulhat a chipek szállítása. Amennyiben ez nem történik meg, további hónapos késlekedés várható a D0 stepping validálásáig. Ezek a példányok ráadásul -- amennyiben Demerjian értesülései helyesek -- 1,6 GHz-es órejelen 24 helyett legfeljebb 18 megabájt L3 cache-t kapnak, és csak 400 MHz-es buszon ülnek majd, ami jócskán visszafogja majd a teljesítményt.

Az 1,8 GHz-es változat, mely Foxtonnal akár a 2 GHz-et is elérheti, jövő év vége felé várható, az Intel reményei szerint már 667 MHz-es busszal. Így elmondható, hogy a Montecito majd egy évet késik, és elmarad a korábban várt órajelektől. A Montecito utódjának szánt Montvale a jelen állás szerint még később jelenik meg, mindössze 2 GHz-es órajelen, csak 24 megabájtos harmadszintű gyorsítótárral, de várhatóan 800 MHz-es busszal, fogyasztása pedig 130 watt lehet. Ez azt jelenti, hogy a késést követően is mintegy 25 százalékos órajelcsökkenést volt kénytelen elkönyvelni a Montecito és a Montvale.

A Montecito az IPF következő jelentős lépcsőfoka, jelentős mikroarchitekturális fejlesztésekkel, melyek a teljesítmény felpumpálása mellett javítják a chip megbízhatóságát, hibatűrését, nem beszélve az energiatakarékos képességekről. Elődjével, a 130 nanométeren termelt Madisonnal szemben a 90 nanométeres tervezésű Montecito már két magot tartalmaz, melyek egyenként két utasításszálat tudnak kezelni, azonban nem egyidejűleg (mint a Pentium 4 Hyper-Threadingje), hanem felváltva, nagy késleltetésű esemény bekövetkeztekor. A Fort Collinsban dolgozó csapat ezen túlmenően jelentősen javította a cache-hierarchia felépítését, különválasztva és megnövelve a másodszintű utasítás- és adatgyorsítótárakat. A Montecito ezeken túlmenően virtualizációs képességekkel is bír már.

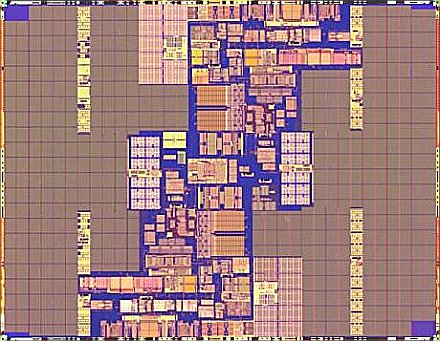

Montecito, 1,72 milliárd tranzisztor

Keserű tapasztalatok

A késés láthatóan kellemetlenül érinti az Intel partnereit is, kifejezetten a számításéhes feladatokra megoldást kínáló vállalatokat, mint például az SGI, amelyek így újabb hónapokat kénytelenek áthidalni a jelenleg hozzáférhető Itanium 2 chipekkel.

A Montecito késlekedése egyet jelent az IPF terjedésének megtorpanásával, ugyanakkor a platform már kinőtte magát annyira, hogy elviseljen egy ilyen fiaskót. A nagy szállítók részéről támogatottsága már elérte a kritikus tömeget, a gyártók dollár százmilliókat öltek és ölnek nagy teljesítményű, csúcskategóriás chipsetek és IPF-gépek megtervezésébe, miközben már alkalmazások ezrei állnak rendelkezésre, kezdve a tudományos, technikai kutatásoktól a nagyvállalati szoftverrendszerekig.

Ezekben a napokban erősítette meg például elkötelezettségét a japán NEC, valamint most alakult meg az Itanium Solutions Alliance is, amely a platform támogatottságának elősmozdítását tűzte ki célul. Tagjai között megtalálható minden jelentős hardver- és szoftvergyártó, mely érdekelt az IPF-platform terjedésében.

A terjedés késés okozta lassulásán, és a legfőbb ellenfeleknek számító IBM Power5 és hamarosan megjelenő Power5+ rendszerekkel szembeni versenyképesség romlásán túl a legnagyobb csapást a bizalom és az elkötelezettség gyengülése jelentheti. Egyes vélemények szerint az Intelnek ezt követően nagyon erős és egyben biztos jövőt, terméktervet kell a partnerek és ügyfelek számára prezentálnia, hogy fenntartsa az IPF-tábor elkötelezettségét. Ugyanakkor a Montecito így is jelentős előrelépést jelent majd, ezenkívül a compilertechnológia is látványosan halad előre, így a teljesítmény karakterisztikája évről évre javul adott hardveren is. Az Itanium-koncepció egyik alapköve a fejlett fordítóra való támaszkodás.

Egyelőre nem tiszta, hogy mostani fejlemények hogyan befolyásolják a hosszabb távú termékterveket, konkrétan a 2007-re tervezett, 65 nanométeres és négymagos Tukwila megjelenését. Talán öröm az ürömben, hogy ez a probléma elegendő tapasztalattal szolgál ahhoz, hogy a jövőben ne fordulhasson elő hasonló -- például hogy nincs kielégítő B-terv kudarc esetére.