Új részletek az Intel 65 nanométeres gyártástechnológiájáról

Mark Bohr |

Az egyre komplexebbé váló integrált áramkörök tervezésénél napjaink talán legnagyobb kihívását a fogyasztás és a hőtermelés kordában tartása jelenti. Ma már nem csak a noteszgépek és az asztali gépek, hanem a szerverek esetében is lényeges szempont a hőtermelés, hiszen az adatközpontok hűtése komoly pénzbe kerül. A kedvezőbb hőleadási adatok lehetővé teszik adott helyen nagyobb számú processzor, végső soron nagyobb számítási kapacitás elhelyezését, amely alacsonyabb hatékonyabb helykihasználáshoz, végső soron pedig alacsonyabb fajlagos költségekhez vezet. Ezért a chipgyártók számára kulcsfontosságú a mindél kedvezőbb fogyasztási és hőtermelési mutatókkal rendelkező alkatrészek előállítása.

Az Intel mantrája, Gordon Moore unos-untalan hangoztatott törvénye kimondja, hogy a félvezetőkre integrált tranzisztorok száma 18-24 havonta megkétszereződik. A vállalatnak az utóbbi időben egyre komolyabb kihívást jelentett megfelelni ennek a jóslatnak, mindazonáltal a cég mérnökei mindent megtesznek annak érdekében, hogy életben tartsák az 1960-as években keletkezett és azóta többször is módosított törvény érvényességét.

A várhatóan 2005-ben debütáló, 65 nanométeres csíkszélességű alkatrészek előállítását lehetővé tevő P1264 kódnevű gyártástechnológia többek között magában foglal új generációs "feszített szilícium" (strained silicon) eljárást, csökkenő hosszúságú, de változatlan szélességű nikkel-szilicid kapuoxidot, valamint ún. alvó tranzisztorokat, amelyneknek köszönhetően látványosan csökkenthető a fogyasztás és a szivárgási áram.

A szivárgási áram a félvezetők lezárt átmenetén létrejövő jelenség, amely szabad elektronok és lyukak kombinációjából származik és nanoamper nagyságrendű. A processzorok fogyasztása a működési feszültség csökkentésével mérsékelhető, azonban ahogy a tranzisztorok nyitófeszültsége (az a feszültségszint, amikor a tranzisztor "bekapcsol") tart a 0 Volthoz, a szivárgási áram nő és egyre nagyobb problémát okoz. A szivárgási áram egy kisebb csíkszélességű gyártástechnológia bevezetésénél akár két-háromszorosára is nőhet. Egyelőre úgy tűnik, a szivárgási áram már a 90 nanométeres alkatrészek esetében is komoly problémákat okoz.

A 90 nanométeres csíkszélességű alkatrészek gyártásánál bevezetett és a 65 nanométeres technológiához továbbfejlesztett "feszített szilícium" technológiának köszönhetően az elektromos áram nagyobb sebességgel áramolhat a vezetékekben, így az áramkör magasabb órajelen működhet. Az utóbbi időben az Intel mellett több jelentős félvezetőgyártó, köztük az IBM és az AMD is jelezte, hogy a jövőben alkalmazni fogja a feszített szilícium módszert. Mark Bohr, az Intel gyártástechnológiai fejlesztésekért felelős vezetője szerint vállalata a technológia alkalmazásában legalább egy generációval versenytársai előtt jár: az Intel 90 nanométeres csíkszélességű gyártástechnológiája is feszített szilíciumra épül. Az eljárás továbbfejlesztése lehetőséget ad az áramkörök tervezői számára, hogy növelhessék a teljesítményt, vagy csökkenthessék a szivárgási áramot.

A 65 nanométeres gyártástechnológia kapcsán bevezetésre kerülő újdonság még a teljesen új kapuoxid. A P1264 eljárással készített alkatrészek kapuhossza 35 nanométerre csökken, amely minden eddiginél kisebb, ugyanakkor a nikkel-szilicidból készített kapuoxid továbbra is 1,2 nanométer széles marad. Az Intel szerint a rövidebb, ám szélességében nem változó kapuoxid 40 százalékos teljesítmény-növekedés mellett lehetővé teszi a kapacitás 20 százalékos mérséklését, amely végső soron a szivárgási áram csökkenését eredményezi.

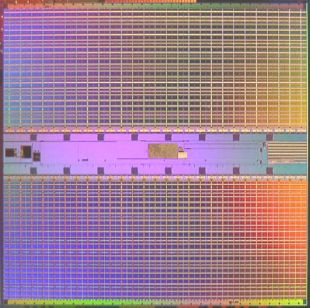

Az első, 65 nanométeres csíkszélességű processzorok megjelenése 2005-ben várható. A P1264 chipgyártási eljárás segítségével nyolcrétegű áramkörök hozhatók létre, rézalapú átkötésekkel és alacsony k-állandójú szigeteléssel. A technológia működőképességét az Intel egyenként több mint félmilliárd tranzisztorból álló, 70 megabit kapacitású SRAM chipek legyártásával demonstrálta.

Több mint félmilliárd tranzisztor mindössze 110 mm2-en

A fentieknél lényegesen látványosabbnak tűnő újítás a legyártott SRAM chipek esetében az ún. alvó tranzisztorok bevezetése. A szivárgási áram elsősorban azért jelent komoly problémát a növekvő komplexitású áramkörökben, mert a chipben található tranzisztorok közül egy időpillanatban csak mintegy 10 százaléka aktív, azonban a szivárgási áram az inaktív tranzisztorokban ugyanúgy jelen van, és az egyre nagyobb számú tranzisztor miatt a jövőben egyre csak nőni fog. Az alvó tranzisztor technológia hasonló a jelenleg is használt "clock gating"-hez, amelynek során az áramkör éppen nem használt részei felé megszűnik az órajel továbbítása. Az alvó tranzisztorok esetében nem az órajel szünik meg, hanem a chip egy része egyszerűen nem kap áramot, így itt egyáltalán nem jön létre szivárgás. Bohr szerint az alvó tranzisztorok bevezetése a fogyasztást és a szivárgási áramot egyaránt látványosan csökkenti.

A 65 nanométeres csíkszélességű alkatrészek gyártásához az Intel számos már meglevő, 193 nanométeres hullámhosszúságű litográfiai berendezést fel tud használni, ami jelentősen csökkenti a gyártási költségeket. Bohr szerint a 90 nanométeres csíkszélességről 65 nanométeres csíkszélességre való átállás egyszerűbb lesz, mint a 130 nanométerről 90 nanométerre történő konverzió. Mindazonáltal szakértők úgy vélik, a jövőben egyre ritkábban váltják egymást az újabbnál újabb chipgyártási technológiák, tekintettel a felmerülő műszaki problémákra, valamint a szükséges berendezések emelkedő árára. Az Intel várhatóan a 45 nanométeres csíkszélességű alkatrészek fotómaszkjait is részben vagy egészben 193 nanométeres litográfiai berendezésekkel tervezi előállítani.

A litográfiai berendezések relatív lassú fejlődése szintén hátráltatja a csíkszélesség csökkentését. A chipgyártóknak különféle trükköket kell használnia annak érdekében, hogy továbbra is fel tudják használni már meglévő, méregdrága berendezéseket. Az Intel tervei szerint továbbra is az ún. száraz litográfiai eljárásokat használja majd, míg egyes gyártók az ún. immerziós eljárásokat kutatják, amelyek lényege, hogy a szilíciumlemezen egy folyadékréteg segít a fénysugár fókuszálásában és a minták rajzolásában. Egy másik, az Intel által is favorizált fejlődési irány az extrém iltraviola -- vagy ultraibolya -- litográfia (EUVL), amely várhatóan az évtized végén kezd elterjedni. Az Intel várhatóan a 2009 környékén bevezetésre kerülő, 32 nanométeres csíkszélességű alkatrészek előállításához használ először EUV litográfiát.

Az extrém ultraviola litográfia alkalmazásához speciális, 10-70 nanométer hullámhosszúságú fény kibocsátására alkalmas fényforrásra, valamint az ilyen hullámhosszúságú fény visszaverésére alkalmas tükrökre van szükség. A jelenlegi, kísérleti EUVL rendszerek az USA csillagháborús programjának keretén belül kikísérletezett fényforrásokra épülnek. Az EUV fény használata azonban igencsak költséges szórakozás, ugyanis a levilágítás csak vákuumban történhet, mivel bármilyen apró porszemcse megzavarja a folyamatot. Az EUVL esetén a fényt nem áteresztő, hanem 40 réteg szilíciumot és molibdént tartalmazó speciális tükrök segítségével irányítják a szilíciumlemezekre. Az EUV litográfiai berendezések ára a kezdetekben tízmillió dollár fölött is lehet.

Ami viszont egyelőre biztosnak látszik, az az, hogy az Intel belátható idő belül nem tervezi a Silicon-on-Insulator (SOI) alkalmazását. A vállalat ugyan kísérletezett ilyen megoldásokkal, azonban a cég jelenlegi álláspontja szerint más jellegű fejlesztésekkel, például a háromkapus (tri-gate) tranzisztorok bevezetésével lényegesen jobban csökkenthető a fogyasztás és a hőtermelés, mint a SOI bevezetésével.